在SaberRD中进行FPGA的系统仿真

电子说

描述

前言

在自动化领域,FPGA(现场可编程门阵列)的作用越来越重要。这些设备构成控制单元的大脑,控制单元包含控制系统各种功能的逻辑。

从环境中收集信息的不同传感器信号被传递到FPGA,并驱动必要的控制输出。随着系统复杂性的增加,迫切需要对各种输入和输出条件下的电路行为有一个全面了解。

SaberRD是一款综合仿真软件,可以虚拟设计和验证任何与电气系统有关的东西。健壮的仿真引擎为模拟和混合信号系统提供了可靠的资源。该仿真器支持VHDL-AMS,它是IEEE标准VHDL语言的扩展,主要用于FPGA和其他数字系统的建模。

此设计示例演示了在SaberRD中包含FPGA的系统仿真。该设备使用VHDL语言建模,系统仿真的目的是为监视器提供适当的信号,系统通过VGA接口将八种颜色的视频发送到显示器。

VGA显示系统介绍

当今的系统变得越来越复杂,必须针对所有可能的组合对系统进行分析。以下分别说明示例系统的详细信息。

1、 数字系统仿真

数字系统由以离散步长改变信号状态的代码组成。FPGA是数字系统,它接收数字输入并根据设备上编程的逻辑提供数字输出。来自各种外设(例如传感器和驱动器)的信息通常是模拟性质的,使用模数转换器将信息传输到FPGA。同样,FPGA的输出通过接口将数字信号转换为有意义的输出。

此类设备可以使用VHDL语言轻松建模。随着仿真需求的增加,大多数设备制造商通常会在组件上附带VHDL或其他仿真模型,以便设计工程师可以在原型构建过程之前仿真完整的行为。SaberRD支持VHDL-AMS语言,它是VHDL语言的混合信号扩展。因此,这些模型可以很容易地用于仿真使用这些FPGA或其他数字系统的系统。

2、 VGA显示系统

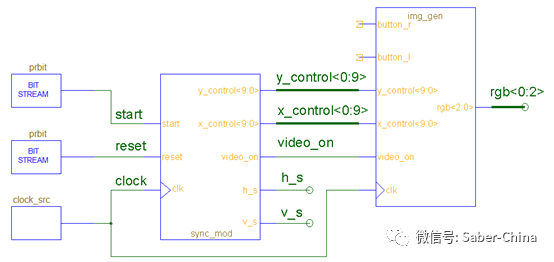

在本设计示例中,VGA 显示由 FPGA的三位数字输出构成。数字输出由两个模块实现,如图 1所示。第一个产生水平和垂直同步信号的模块定义为同步模块(sync_mod),第一个模块还产生第二个模块图像生成模块(img_gen) 所需的信号。

图 1带有两个模块的顶层原理图

img_gen模块的输出是三位输出。这意味着VGA显示器中可以有8种组合,因此可以有8种颜色。位组合的数字输出与VGA颜色输出对应如表 1所示。

表 1数字输出与VGA颜色输出对应表

3、 同步模块

同步模块为VGA显示器生成垂直和水平同步信号。该模块具有三个输入,它们是:

- 开始 --- 这将激活/停用模块

- 时钟 --- 系统时钟

- 重置 --- 重置同步模块

两个输出信号是垂直和水平同步信号,它们直接连接到 VGA 连接器。

除了两个输出之外,还有三个信号输入到图像生成模块。其中两个输出x_control和y_control控制 x 和 y 像素。此设计默认的VGA显示分辨率为640 X 480。因此,x_control 从 0 计数到639,y_control 从 0 计数到479。为了完成此任务,模块中创建了两个计数器模型。一个计数器满足水平分辨率,另一个满足垂直分辨率。第三个信号是 Video_on 信号,用于启用/禁用视频。代表同步模块的符号如图 2所示。

图2同步模块符号图

4、 图像生成模块

该模块为VGA显示器生成RGB输出,该模块具有在显示中生成所需块的部分。如前所述,三个RGB输出是数字信号,可产生八种组合,从而在显示中产生八种颜色。图像生成模块的符号如图 3所示。

图 3图像生成模块符号图

该模块的VHDL模型有几个部分来描述输出数字信号。在VGA显示器上生成的最终图像用于PONG游戏,该游戏具有三个主要组件,如图 4所示。

图 4图像生成模块在输出端的VGA显示

在VGA显示器上看到的PONG游戏中的三个主要组件是:

- Wall - 限制球越过并在屏幕上以黑色显示。

- Ball - 在屏幕中移动并以绿色显示。

- Bar – bar由img_gen模块上的button_r和button_l输入控制,并以蓝色显示。

图像生成模块生成数字输出以显示三种颜色,屏幕的其余部分为红色。以下是 RGB 数字引脚上预期的输出:

表2图像生成模块期望的输出

图像生成模块的输入x_control和y_control定义了显示器上的像素,x_control和 y_control给定值下的颜色输出由图 4决定。对于y_control的每个值,x_control的值从0扫描到639,,y_control的值从0扫到469。这样就形成了一个640X480分辨率的视频,完成了一个显示周期。这是由图像生成模块的video_on输入决定的。

SaberRD中仿真与分析

SaberRD仿真平台中主要进行瞬态分析,它根据时间仿真系统性能。SaberRD运行关于时间的模拟,并绘制各种信号以检查系统输出。在SaberRD中运行仿真有几个选项可用于可视化电路中不同部分的操作。用于运行各种分析、绘制结果、测量各种参数等的自动化工具对于提高设计工程师的生产力非常有用。

该设计还附带一个运行瞬态分析并绘制rgb输出信号的实验。除此之外,video_on信号以及指定显示器上像素的 x 和 y 值。

1、 如何运行实验Experiment

a、下载设计文件中,打开设计vhdl_fpga_demo.ai_dsn。

b、转到Simulate选项卡,在Analysis列表中选择Experiment,在屏幕右边的Experiments列表中选择transient_analysis。开始仿真。

c、仿真完成后,results窗格将显示图表和实验报告。

d、双击实验报告,在报告中可以看到Ball和Bar宽度的测量值。

e、双击图表“key_outputs”,如图 5所示的波形图显示出来。

2、 结果和观察

了解设计的预期结果以了解仿真结果是否符合预期非常重要。设计的期望已经在上面的部分中解释过。运行实验后,结果窗格中会显示图表和实验报告。双击图表“key_outputs”结果如下图 5。

图5瞬态仿真波形图

如前所述,对于变量“y”的每个值,变量“x”从 0变为639。‘y’ 的值从0到479以完成一个显示周期。这是640X480分辨率VGA显示器的定义。

如图 4所示,显示和背景中有三个项目。这会在输出引脚上产生rgb(0)、rgb(1)和rgb(2)的四种组合,如表1中所述。图 5中提到了在一个显示周期中的四个区域。

当图表放大到区域1时,信号如图 6所示。可以看出 rgb 输出为 0、0 和 0,这表示黑色表示墙壁。

图6黑色墙壁的RGB输出状态

区域2被缩放以查看屏幕上显示的球。球是绿色的,输出应该是010。图 7中显示的放大区域也证实了这一点。

图7绿色球的RGB输出状态

区域3表示背景,颜色为红色。红色的代码是100,如下图 8所示。

图8红色背景的RGB输出

显示器上的最后一个对象是蓝色的Bar,RGB输出应为001,如下图 9所示。

图9蓝色Bar的RGB输出

除此之外,图表上还有两个测量值。这些测量以像素为单位显示宽度,其中Ball的宽度为20,Bar 的宽度为120像素。这可以通过打开img_gen.vhd模型来验证,如下图 10所示。

图10图像生成模块代码

按比例,Ball和Bar的宽度可以在实验报告中验证,如图 11所示。

图11测量显示Ball和Bar的宽度

这里描述了图 10中红框中显示的Bar和Ball宽度如何与图 11中的脉冲宽度测量相关。一个video_on脉冲宽度,对于给定的“y”,在此期间,“x”像素从0变为639 ,如图 12所示,为1.28ms。在此期间 x 像素为蓝色的时间为240us。

图12以像素为单位计算Bar的宽度

因此,以像素为单位的Bar宽度为

同样,以像素为单位的 Ball 的宽度为

结论

该设计示例表明 FPGA 的仿真可以在SaberRD 中执行,并且自动化方法有助于获得易于阅读的结果。在仿真工具中执行的详细分析表明,电路的输出符合设计要求和所需的输出。因此,SaberRD 被证明是用于仿真涉及到 FPGA 的设计的有前途的解决方案。

-

在Matlab/Simulink中进行永磁同步电机流频比I/F控制系统的仿真分析2023-06-08 3086

-

在Quartus ii 13.1中进行波形仿真时出现错误,求大神解答2014-12-21 20225

-

基于FPGA的数据采集系统求助2015-04-28 2461

-

如何在ADS中进行EM仿真2018-12-27 8145

-

在stmcubeMX中进行配置使用freertos系统2021-08-10 1126

-

如何在ROBOGUIDE环境中进行离线编程和仿真?2021-09-18 2307

-

在Altium Designer的Protel中进行混合信号2009-09-25 1029

-

在调制数字系统中进行精确的非线性测量2010-04-08 1079

-

在Protel DXP中进行FPGA设计和仿真2015-12-25 1133

-

大型交直流系统的PSCAD建模与仿真2016-05-11 1244

-

在NI VeriStand环境中进行FPGA相关配置2017-11-18 5611

-

如何使用FPGA进行仿真系统数据采集控制器IP核设计的资料概述2018-11-07 1049

-

在SDAccel中进行调试2018-11-29 2440

-

在PSIM中进行VHDL的联合仿真2023-05-23 5738

-

fpga仿真器是什么?它有哪些优势?2024-03-15 3393

全部0条评论

快来发表一下你的评论吧 !