AMD Versal系列CIPS IP核建立示例工程

描述

接着上一篇“AMD Versal系列CIPS IP核介绍”文章来进一步讲解如何来建立CIPS IP核示例工程。

利用CIPS IP核的板卡自动化以及预置功能,生成VCK180 DDRMC基于GUI界面的调试工程。当然该工程亦可以根据AMD官网例程TCL文件来完成。

本文是基于Vivado 2022.1版本进行演示,其他版本界面可能会有细小差异。

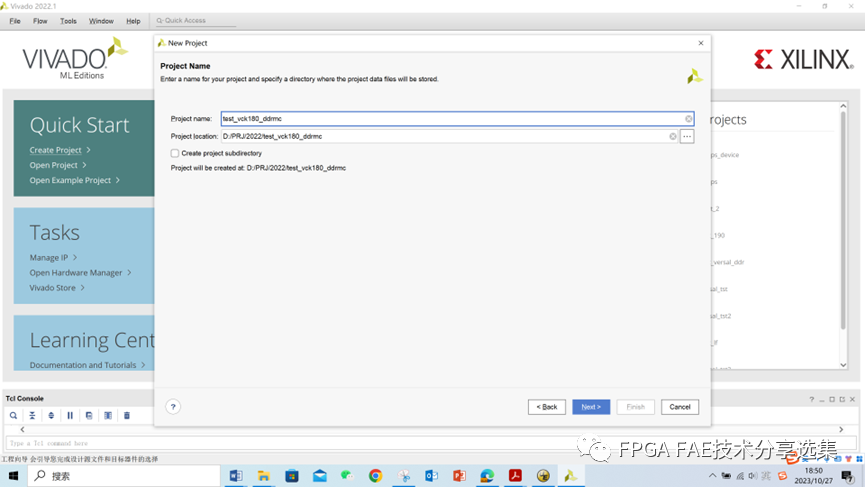

Step1 新建工程

工程名字和路径需要字符形式出现,同时路径不能太长。

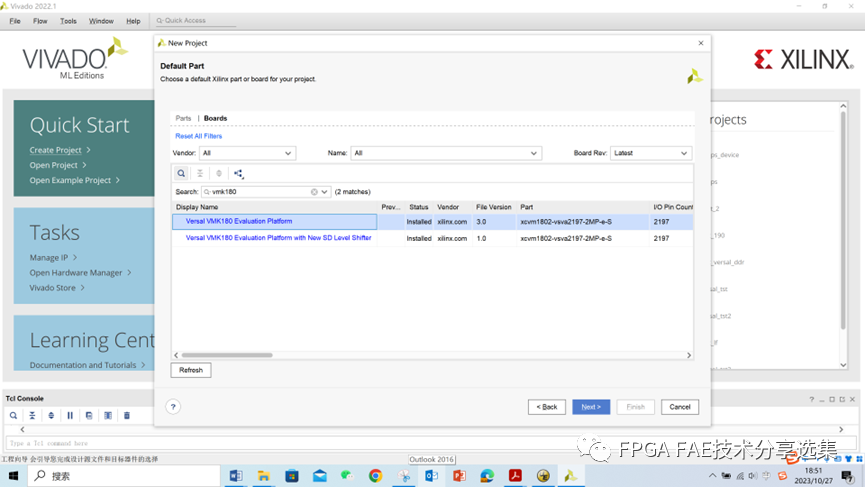

Step2 选定工程板卡

由于我们是做DEMO目的,所以板卡选择Versal Prime系列的VMK180;当然也可以选择其他Versal系列的开发板,或者客户自定义。

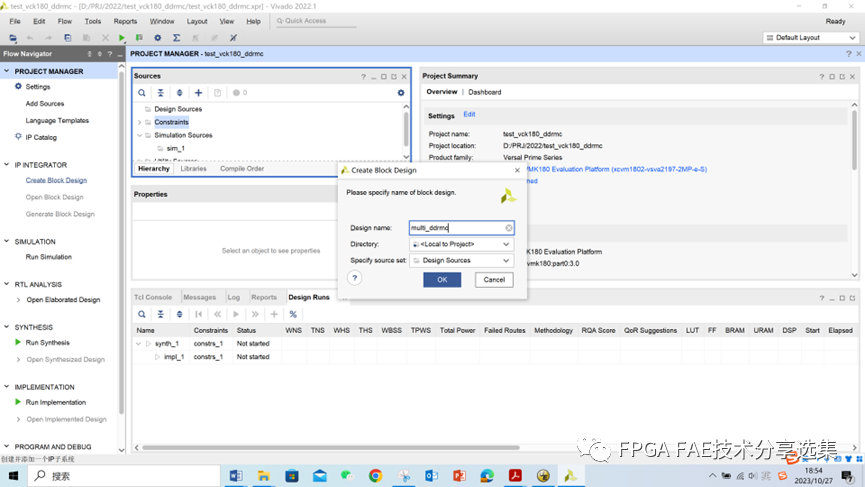

Step3 创建Block Design工程

使用Block Design流程可以很方面的增减IP,给设计带来很高的灵活性并节约写代码时间。

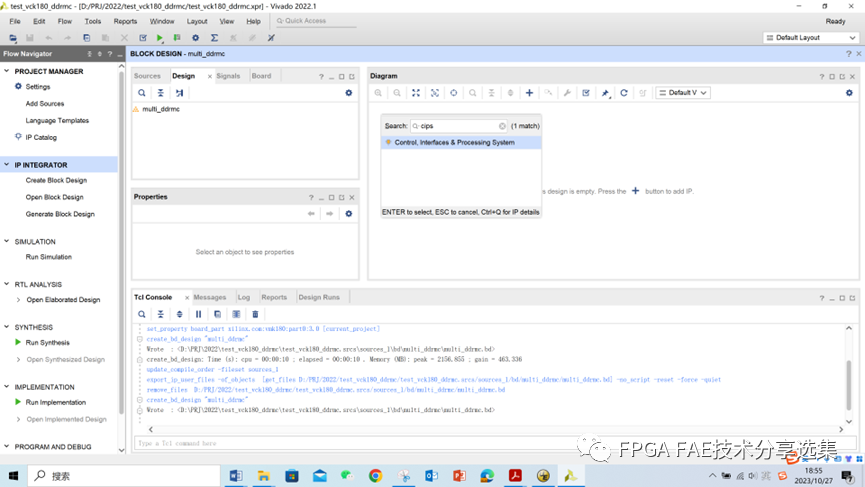

Step4 加入CIPS IP核

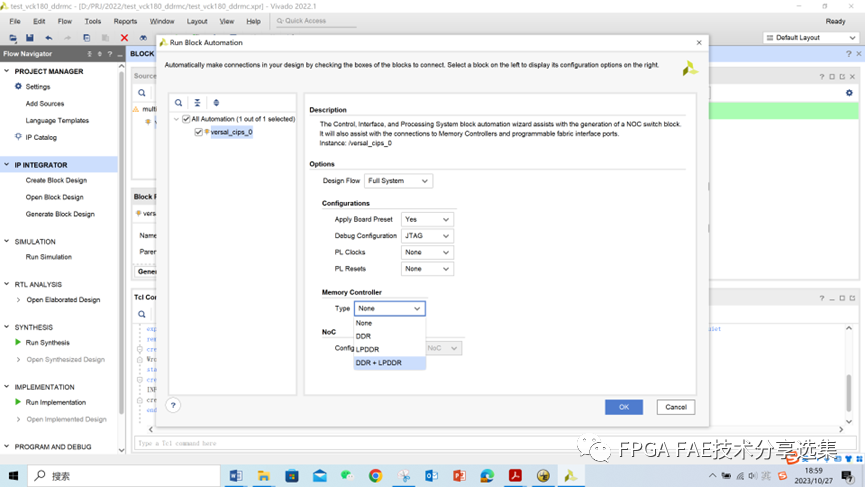

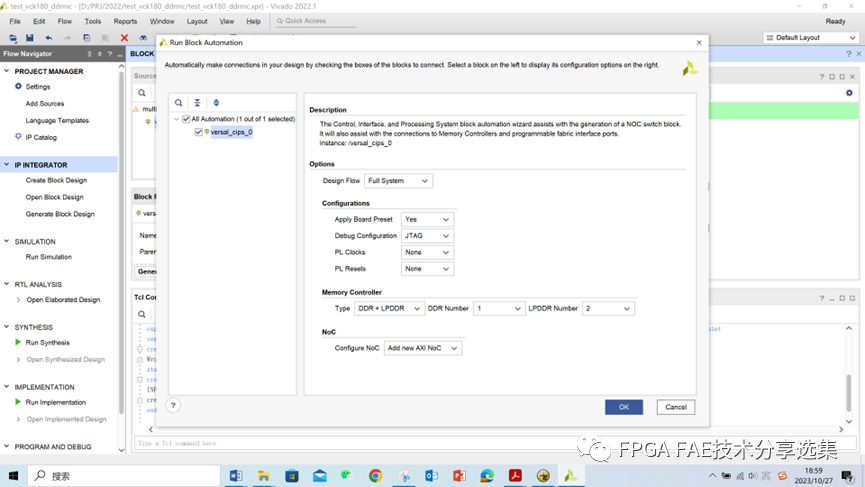

Step5 运行Automation与预置功能

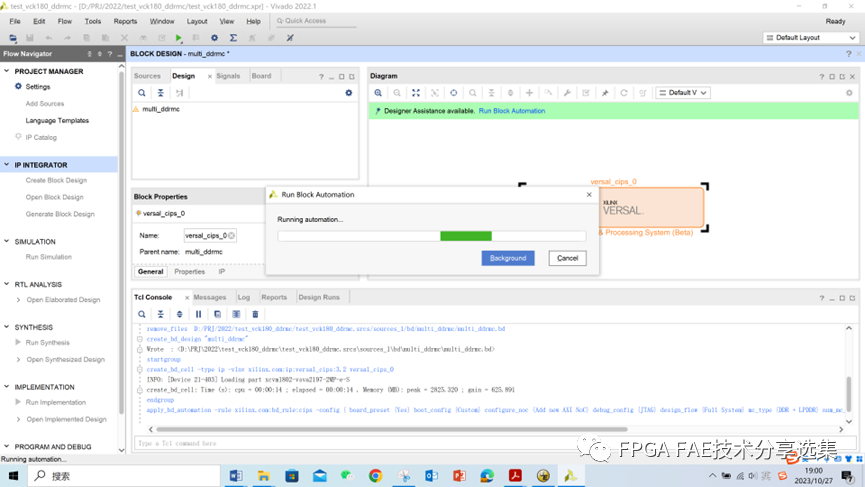

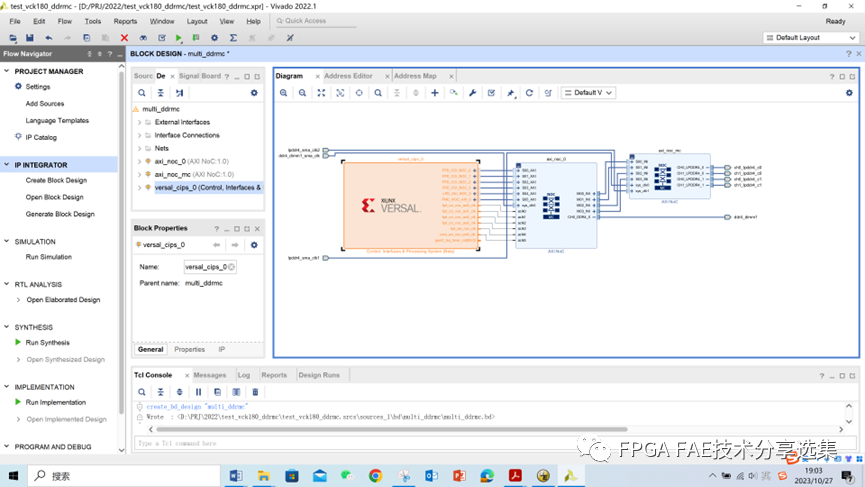

Step6 生成工程Diagram

Runing Automation可以自动生成CIPS的已定义的接口,同时可以跟其他IP进行互连,避免人工操作。

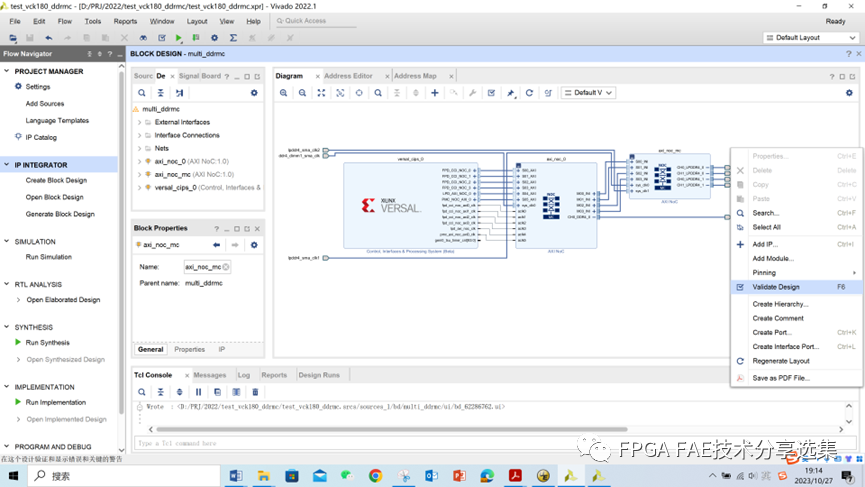

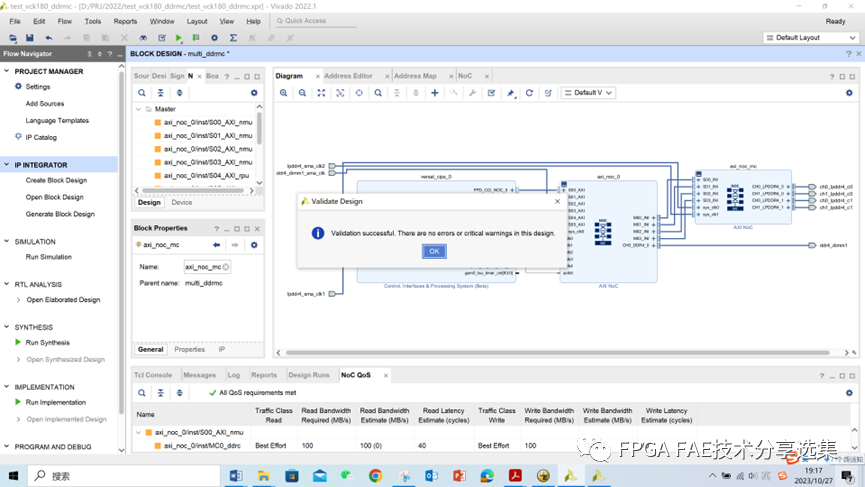

Step7 设计验证

运行Vaildate Design功能可以检查Block Design设计是否有误;需要把错误全部消除掉才可以进入下面流程。

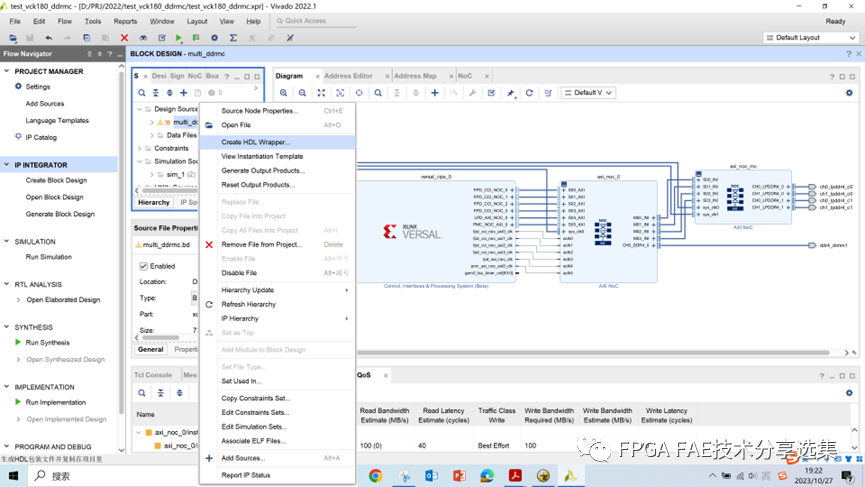

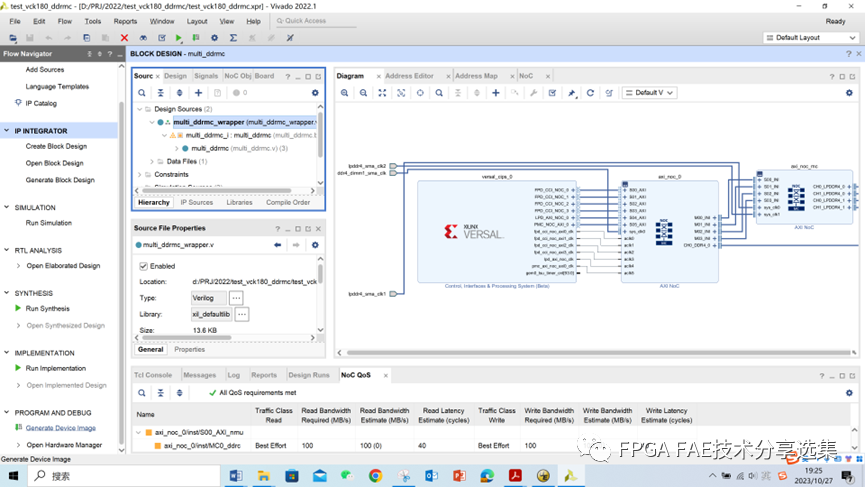

Step8 生成HDL Wrapper

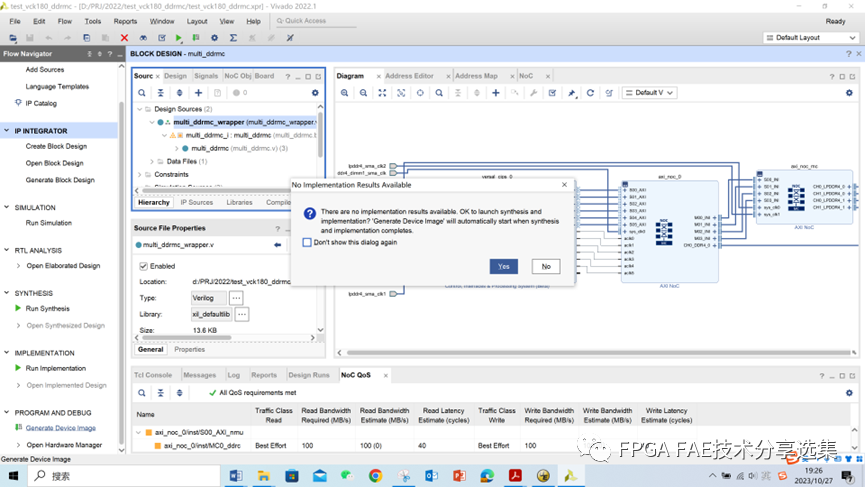

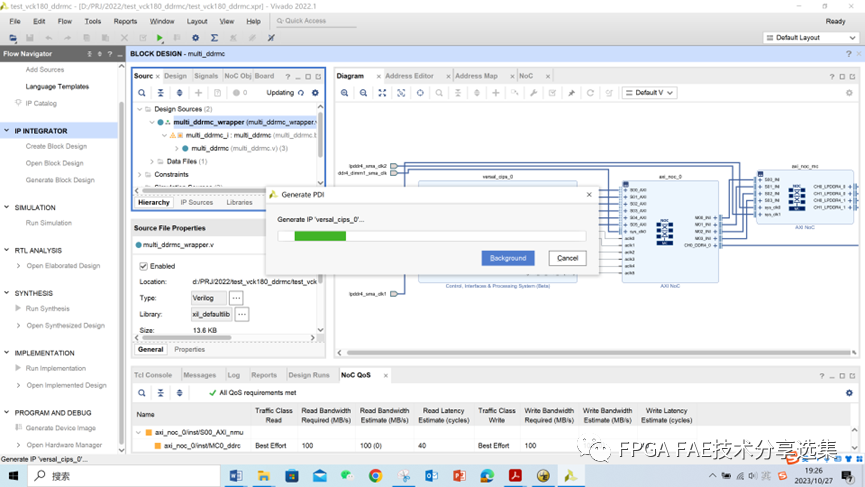

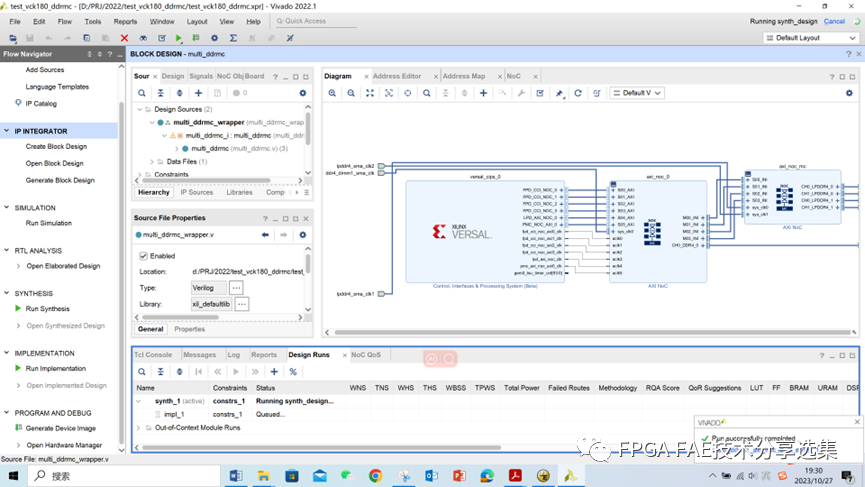

Step9 生成Device Image

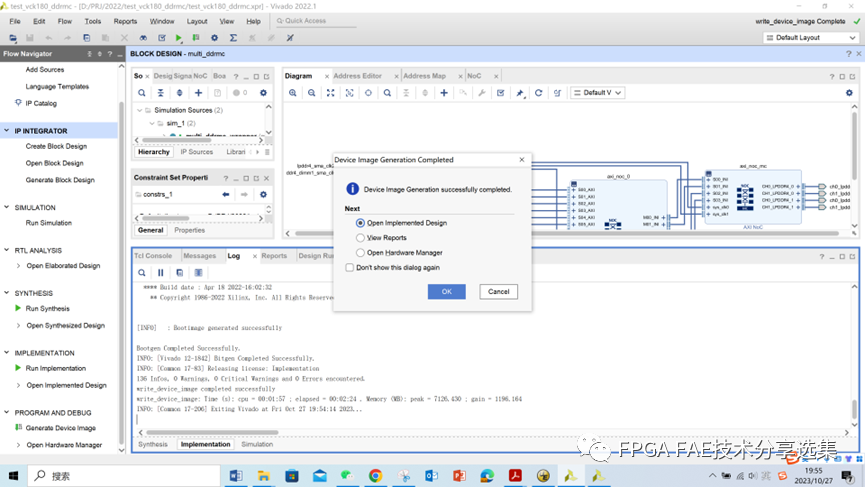

Step10 成功生成Device Image

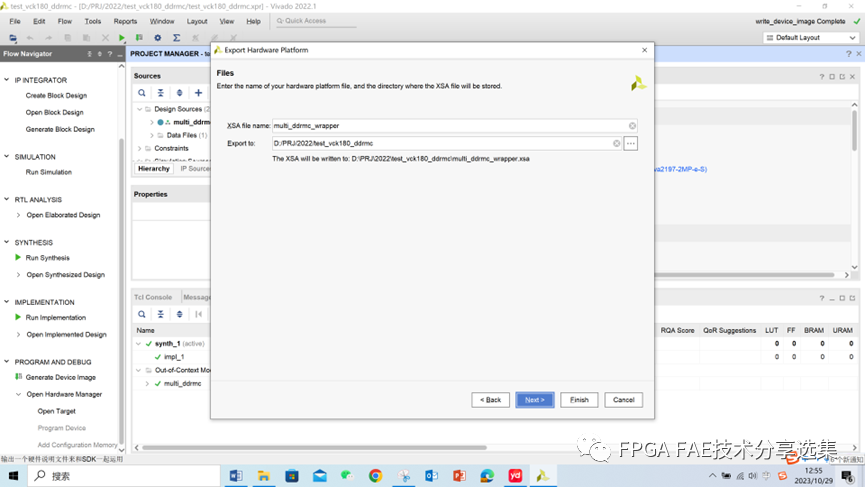

Step11 导出硬件平台

成功生成xsa文件后,软件工程师就可以使用xsa进行后续软件开发工作。

审核编辑:汤梓红

-

在AMD Versal自适应SoC上使用QEMU+协同仿真示例2025-08-06 2171

-

AMD Versal系列CIPS IP核介绍2023-11-27 3321

-

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)2024-03-07 2936

-

VIP系列IP核使用2015-04-13 2833

-

利用设计网关的 IP 内核在 Xilinx VCK190 评估套件上加速人工智能应用2022-11-25 2749

-

建立用户自己的IP核2018-04-03 824

-

CIPS 3.0变更日志和移植信息解决方案2022-08-02 1799

-

Versal CPM AXI Bridge模式的地址转换2023-05-10 3614

-

Versal HBM系列外部参考时钟设计指南文章2023-06-05 1911

-

Versal System Monitor(Sysmon):过热告警行为2023-07-10 1287

-

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例2024-05-10 1930

-

AMD推出第二代Versal Premium系列2024-11-13 1781

-

AMD Versal自适应SoC器件Advanced Flow概览(下)2025-01-23 1802

-

AMD第二代Versal AI Edge和Versal Prime系列加速量产 为嵌入式系统实现单芯片智能2025-06-11 2049

全部0条评论

快来发表一下你的评论吧 !