FPGA实现基于Vivado的BRAM IP核的使用

描述

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。

BRAM是FPGA定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM。

本片文章是基于Vivado的 2017.1的版本,其他版本都大同小异。

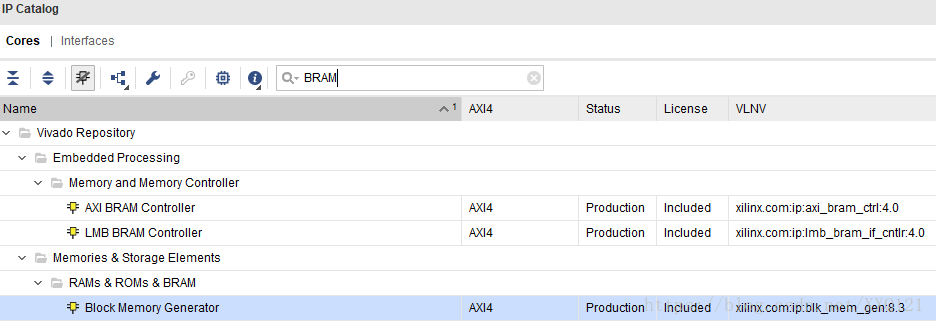

首先在Vivado界面的右侧选择IP Catalog 选项。

然后就可以在IP 目录中,选择想要的IP核,此处在搜索框输入BRAM,选择我们要使用的BRAM IP核。

即最下方的Block Memory Generator,顾名思义,块状RAM。

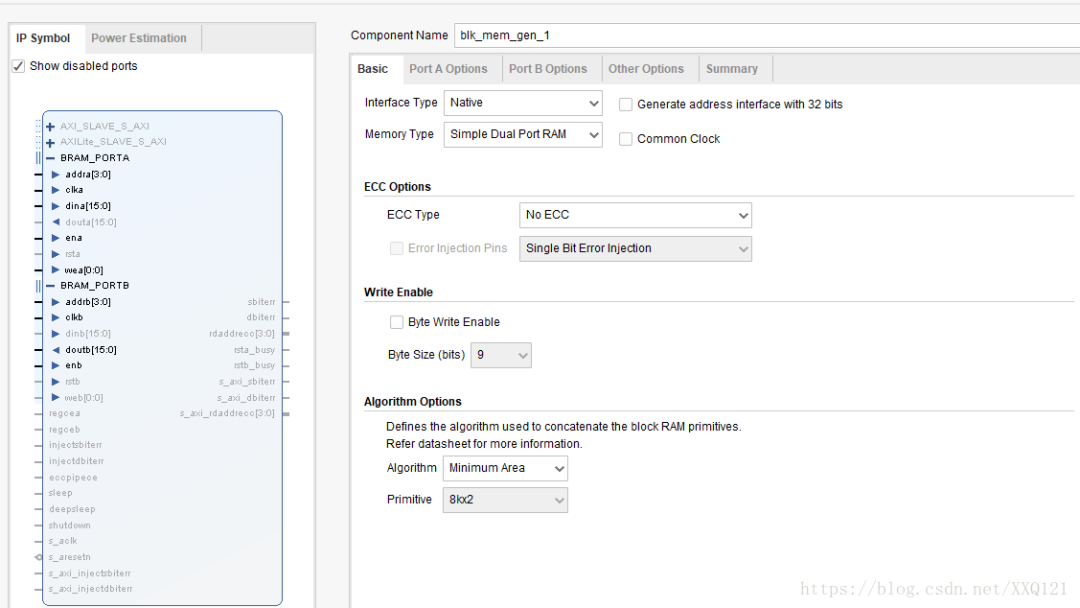

我们常用的是单口BRAM,单口写,单口读。可配置Memory Type 为Simple Dual Port RAM。如下图所示:

其中Component Name 可以自定义自己所需要的模块名称。类型定义完成后,可以看到左侧显示的模块端口,端口的使用后面再细说。

设置完成后,开始设置端口的位宽以及深度,选择Port A Options选项,可以看到下面的界面。

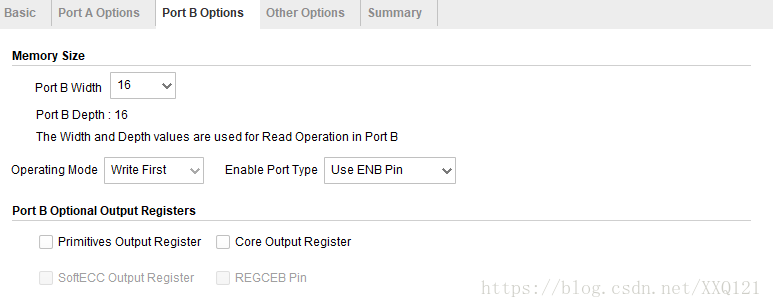

Port A Width即位宽,也就是你存储数据的有多少位,Port A Depth即深度,也就是你要存多少个数据。端口A设置好后,还需要点击Port B Options,点击完进入Port B Options选项后,系统会帮你自动设置好端口B的宽度和深度,因为B肯定是和A一样的。

可以看到端口B也设置完成,同时在Port B Optional Output Registers有一个Primitives OutputRegisters选项。如果这个选项不勾上,那么正常的情况下,当第一个时钟时候,送来地址,那么数据会在第二个时钟取好送出RAM。但是当勾上这个选项后,那么数据就会延迟两个时钟,在第三个时钟送出。这是取数据情况下的时序。当存数据时候,那么只需要地址和数据在同一个时钟下即可。

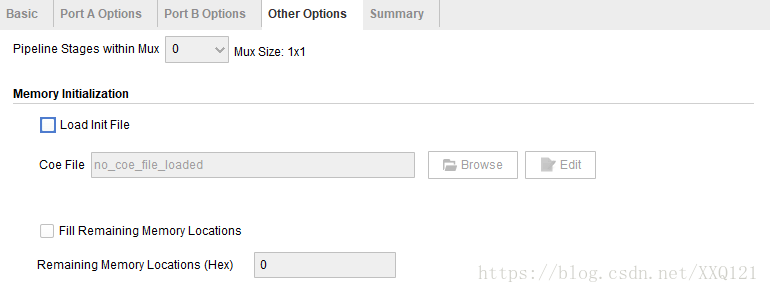

当我们在一般使用RAM时候,如果需要事先存到RAM里的数据量不大,我们可以在Testbench里面写一下即可。但是如果数据量较大时,那么我们可以使用.coe文件事先将数据导入到RAM 之中,如下图所示。

在Other Options选项中,有一个Load Init File选项,即加载初始化文件,在这里勾上后,即可加载已存储好数据的.coe文件。关于.coe文件的制作,网上有很多教程,在此不再赘述。然后点击下方OK,然后再点击弹出来的窗口的Generate即可生成BRAM 的IP核。

至此,常用情况下的BRAM的配置选项以及设置介绍完成。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA实现基于Vivado的BRAM IP核的使用

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- FPGA

-

怎么在Vivado HLS中生成IP核?2020-03-24 3913

-

BRAM IP核包括哪几种类型?怎么使用?2021-03-08 12783

-

Vivado生成IP核2023-04-24 3496

-

基于Xilinx_FPGA_IP核的FFT算法的设计与实现2016-05-24 955

-

Vivado中用HDL定义BRAM存储器并用updatemem合成bit文件2017-02-08 5910

-

了解Vivado中IP核的原理与应用2017-11-15 11302

-

vivado调用IP核详细介绍2018-05-28 38840

-

FPGA实现基于Vivado的BRAM IP核的使用2020-12-29 13600

-

Vivado中xilinx_BRAM IP核使用2021-03-10 2230

-

FPGA应用之vivado三种常用IP核的调用2023-02-02 5170

-

VCS独立仿真Vivado IP核的问题补充2023-06-06 3133

-

如何在Vivado中配置FIFO IP核2023-08-07 7710

-

Vivado中BRAM IP的配置方式和使用技巧2023-08-29 10873

-

Vivado IP核Shared Logic选项配置2023-09-06 3274

-

Vivado中IP核被锁定的解决办法2026-02-25 491

全部0条评论

快来发表一下你的评论吧 !