大算力芯片里的HBM,你了解多少?

描述

最近,随着人工智能行业的高速崛起,大算力芯片业成为半导体行业为数不多的热门领域

HBM (高宽带内存:High-bandwidth memory)作为大算力芯片里不可或缺的组成部分,也因此走入了行业内外人士的视野

和传统的GDDR相比,HBM不仅仅提供了更大的位数宽度,而且通过TSV和Interposer的连接方式,大幅降低了数据通讯上的能量损耗。这对于大算力芯片的性能效率提升是起到决定性作用的

如果GPU通过PCB板和传统GDDR内存交换数据,那在高速运算时其大多数的能耗都会消耗在数据通讯本身而非计算上。这对于能耗成本高企的AI模型训练来说是几乎不可接受的

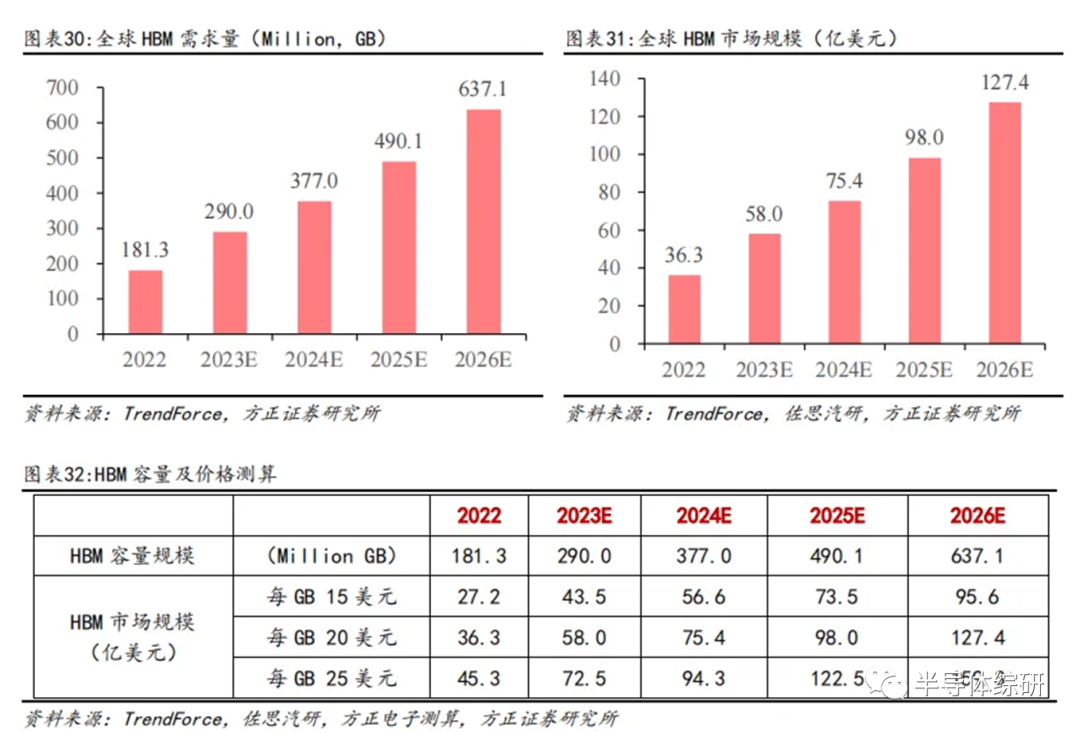

而采用HBM以后,通讯相关的能耗可以成倍降低,甚至有可能把能耗占比降到20%,甚至更低。所以目前AI相关的算力芯片都几乎采用了HBM的技术方案。HBM的市场也随之爆发(见下图)

我趁这个热度,也收集了不少资料好好学习了一下HBM相关的知识

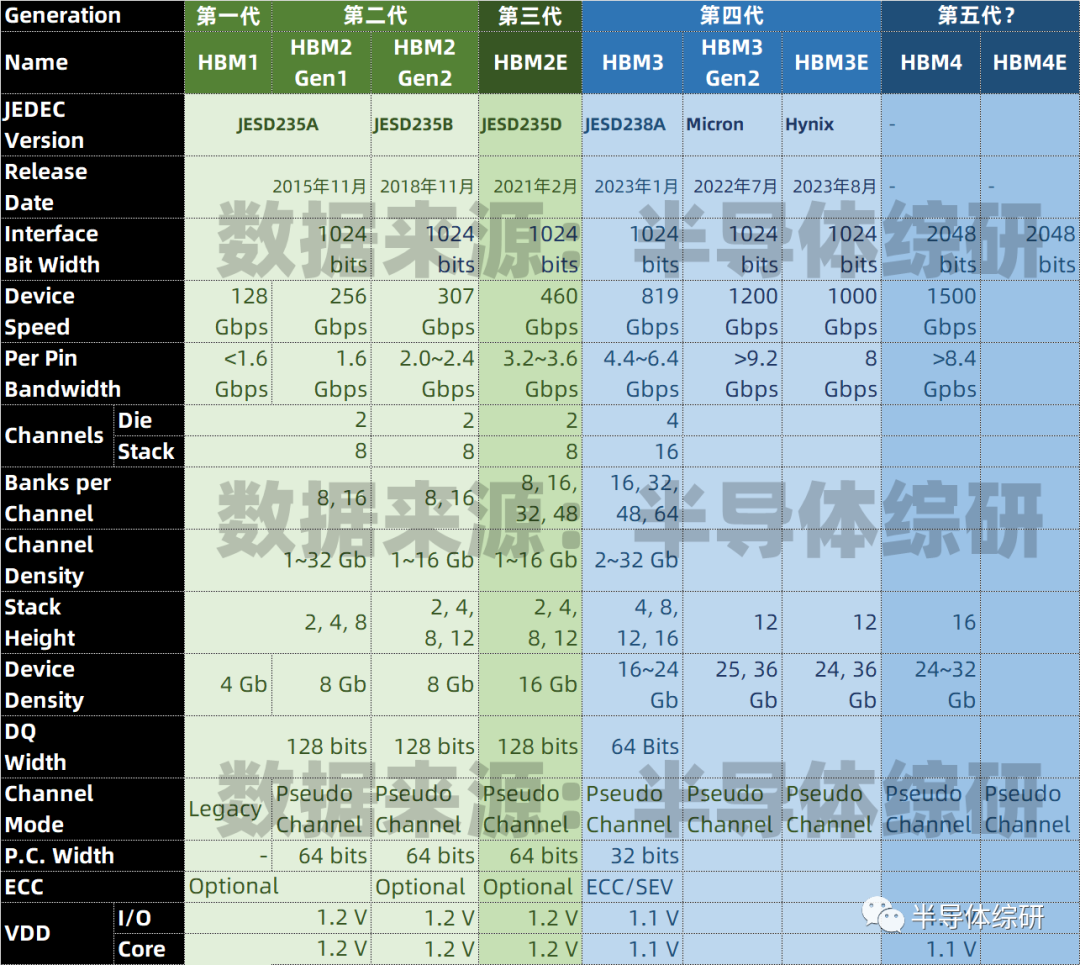

HBM到目前为止基本发展了四代:

第一代和第二代的技术规范标准被定义在了JEDEC的JESD235里,后更新为JESD235A。HBM2相对于HBM1的区别是通道模式由原来的Legacy变成了Pseudo Channel:用两个虚拟的64位通道等效成一个128位通道

后来在JESD235C和JESD235D里定义了HBM2E,较大幅度地提升了数据通讯能力等参数。行业里习惯把这个称为第三代HBM

而JESD238开始定义的HBM3则被顺延地称为了第四代HBM。需要注意的是,这次JEDEC标准文档的编号也从235改成了238

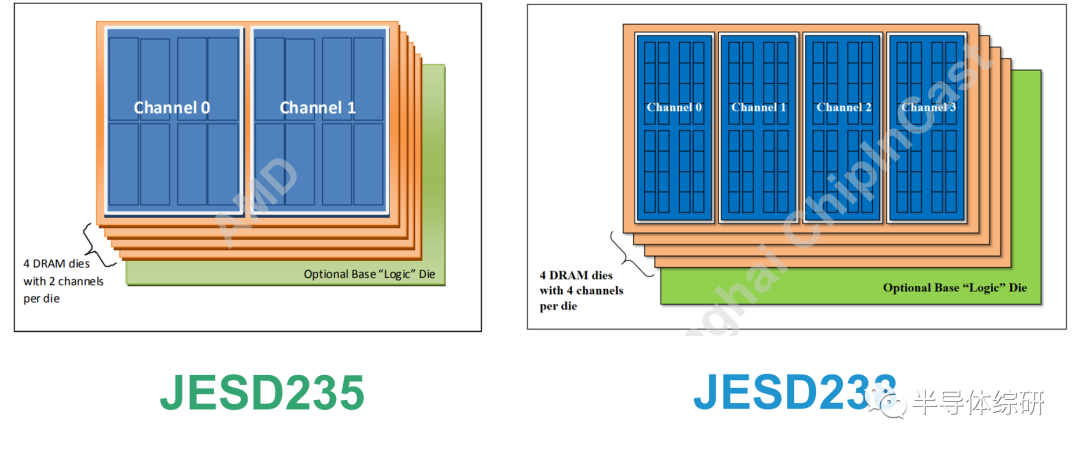

和之前的版本相比,HBM3的最大变化是每个Stack的通道(Channel)数量从2个增加到了4个,从而使得数据容量翻倍

后来在JEDEC的标准上,Micron、Hynix等制造商也分别推出了自己的增强型版本至于第五代的HBM4,目前JEDEC的标准还没有正式推出。我在网上也只能找到一些简单的指标数据作为参考

为了整理各个版本HBM的具体指标参数和相关信息,我不仅下载了JEDEC的各个版本文档,也参考不少其它的资料,然后收集整理了下面这个表格供大家参考欢迎大家帮忙确认,如果发现任何问题,请和我沟通或者在公众号给我留言,谢谢了

注:转载至 半导体综研 文中观点仅供分享交流,不代表贞光科技立场,如涉及版权等问题,请您告知,我们将及时处理!

-

算力需求催生存力风口,HBM竞争从先进封装开始2023-12-03 3185

-

【「算力芯片 | 高性能 CPU/GPU/NPU 微架构分析」阅读体验】--全书概览2024-10-15 2251

-

AI算力需求的暴增,HBM和GDDR SDRAM成为AI芯片新的内存方案2020-11-09 3666

-

ChatGPT背后的算力芯片2023-05-21 4984

-

算力系列基础篇——算力101:从零开始了解算力2024-04-24 1002

-

揭秘芯片算力:为何它如此关键?2024-05-09 4007

-

亿铸科技熊大鹏探讨AI大算力芯片的挑战与解决策略2024-10-25 1831

-

算力基础篇:从零开始了解算力2024-11-15 5719

-

DeepSeek对芯片算力的影响2025-02-07 2017

-

大算力芯片的生态突围与算力革命2025-04-13 3578

全部0条评论

快来发表一下你的评论吧 !