ESD防护应用:GGNMOS和GCNMOS对比分析

EMC/EMI设计

描述

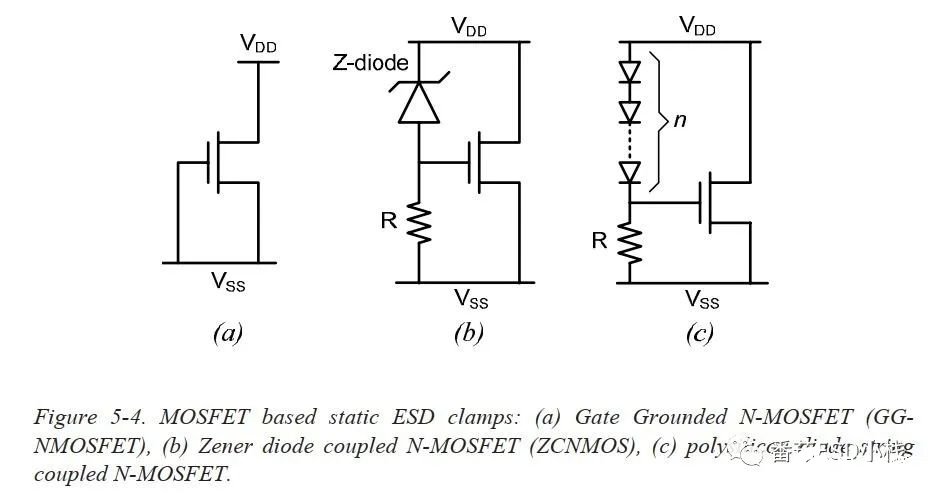

NMOS主要有两种ESD防护应用:一种是之前讲的GGNMOS,另一种是GCNMOS(Gate Coupling NMOS)。现阶段也已经出现了(Bulk Coupling NMOS),接下来这两种ESD防护器件都会进行讲解。

GCNMOS的工作原理与GGNMOS不同,GGNMOS是利用体寄生三极管的开启进行ESD静电流的泄放通路,而GCNMOS则利用了NMOS器件的沟道作为泄放通道。GCNMOS开启NMOS管的途径有两种:一种是利用静电频率作为触发条件,一种是利用静电压作为触发条件,如图所示。

图一.电压触发GCNMOS。

图二.频率触发GCNMOS。

针对component的ESD设计是关注芯片在非正常工作状态下的防护能力。所以片上ESD设计是防止ESD器件对正常工作产生干扰的同时确保在静电来临时能产生ESD静电泄放通道,基于这个核心思想产生了两者耦合方式。

电压触发:

正常工作情况下VDD—VSS的压差小于齐纳或二极管串的导通电压,此时NMOS的栅压为低压,NMOS关断。而当VDD上有ESD电流产生后,这部分电流会集聚在二极管串的阳极或齐纳管的阴极,直到电压足够导通器件。可以把ESD电流类比为水流,ESD电流始终要完成泄流,在泄流前会一直聚集产生电压,直到内部器件击穿产生通路或者ESD防护器件开启产生通路。利用这一特性调整齐纳管或二极管串的导通电压Von,使得VDD

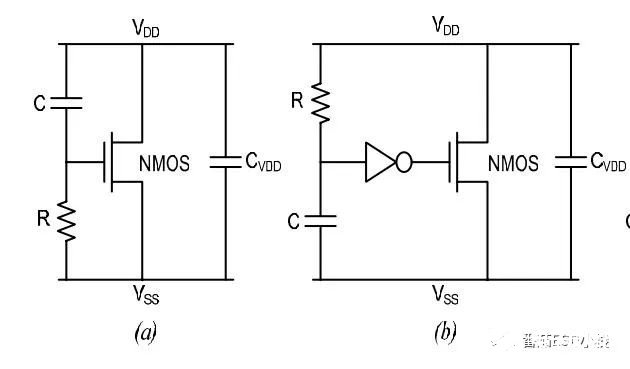

频率触发:

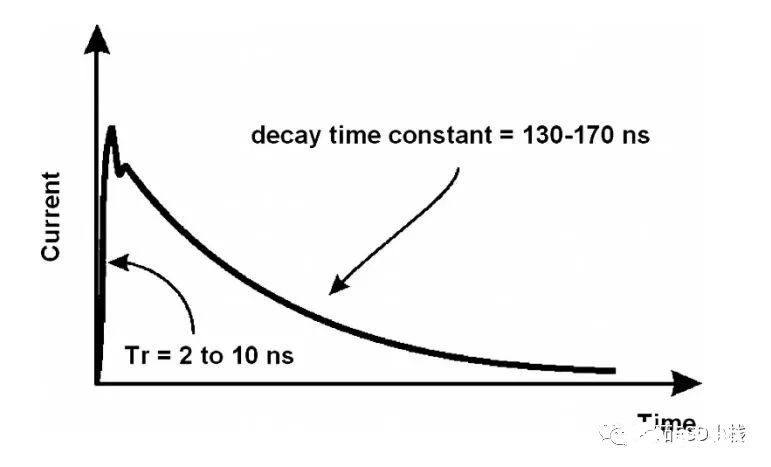

通过RC电路的频率特性,将高频的ESD电流与普通上电的波形进行区分。ESD的波形如图所示,

图三.HBM波形。

HBM的波形中0~10nm内会存在一个上升沿,到达峰值后,在150ns的时间内衰减至峰值的20%左右,整个ESD脉冲的持续时间大概为1us。为了便于理解及方便系统化设计,将HBM的时域波形转化为频域波形,如图四所示。

图四.HBM波形的频域。

(这里只是为了便于下文叙述举个例子,真正的变换远比这复杂得多)。HBM波形中能量主要集中在前20ns内,在这个频域范围内变换的正弦波也是我们需要重点关注的,设这个频率范围为ωESD。频率触发的GCNMOS的工作原理是利用RC电路的频率响应特性对ESD波形产生响应。当VDD轨上产生静电波形后,RC部分的等效电路如图五。

图五.ESD-RC等效电路。

电容的阻抗为1/jωC,则HBM的主要能量集中在高频部分,其等效阻抗较小,电压降主要集中在电阻上,A点电位为高,当电压大于NMOS的阈值电压后,沟道开启,出现从VDD到GND的静电流泄放通道。而当ESD主频结束后,RC的固有响应也会使得NMOS持续开启一段时间,确保NMOS在整个ESD事件中维持开启状态。而当正常上电时,等效电路如图六。

图六.POWER-ON-RC等效电路。

一般电路的上电速度远低于ESD放电频率,此时电容阻抗较大,电压集中在电容上,A点电位为低,NMOS关断,不会对正常工作产生影响。 目前的设计也有如图二(b)中所示将电容电阻位置对调的,其基本原理与CR相同,不过需要在电路中加一个反相器,而这个反相器不仅能改变电位,同时还能通过改变其结构,提高后一级NMOS的栅压,缩减R和C的面积。

举个例子:

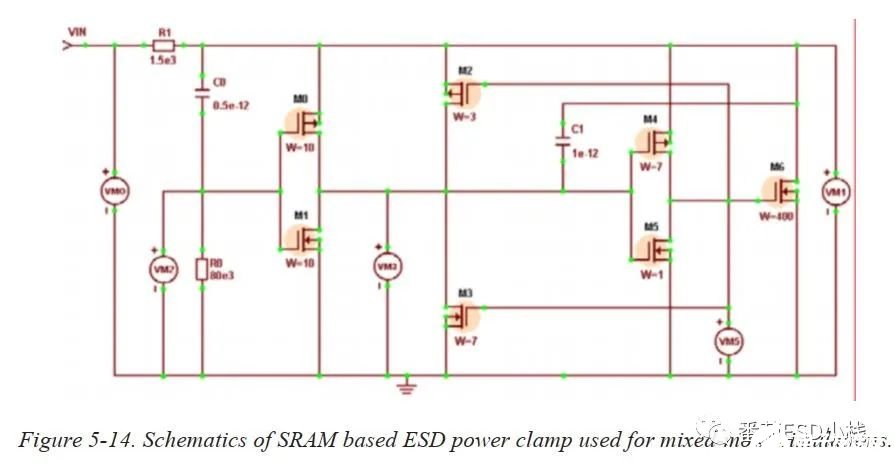

图七. SRAM ESD power clamp电路图

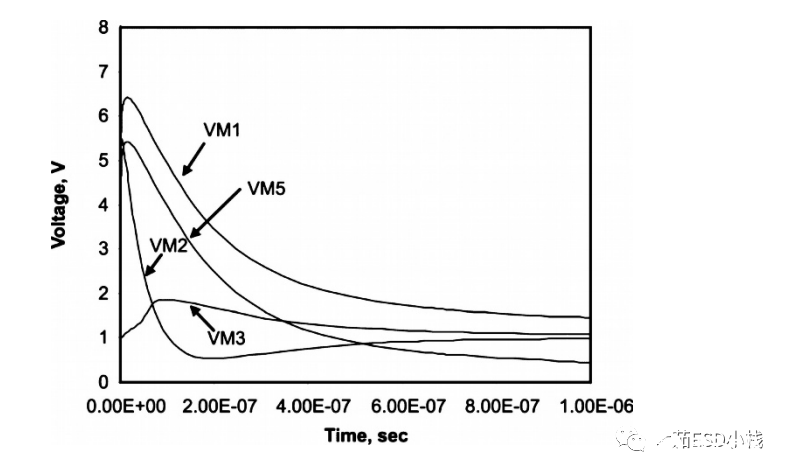

图八. SRAM ESD power clamp仿真结果。

这是一种通过SRAM结果实现CR电压修调的例子,其电路图和仿真结果如图7,8所示。可以看出因为SRAM结果的存在,VM2不需要一直维持很高,CR的时间常数τ很低,说明C与R的面积也不需要很大。

目前的GCNMOS电路中也会添加一个shut-down control电路,实现芯片上电后断路或短路GCNMOS的作用。这也是和component ESD的设计思路相关,component ESD的防护场景也只是针对芯片在非使用下的静电。而没有shut-down control可能存在芯片上电后面对system ESD时GCNMOS开启的误触发情况。

GCNMOS相较于GGNMOS的优点是可以有效减低寄生参数的影响,广泛应用于高速场合,但是其面积需求也大,并且不能应用于高压,负压等复杂场合。同时关于GCNMOS的布局布线也有相对应的要求,其实ESD电路的关键点还是在版图上(有机会了再展开讲讲)。

这期也只是讲解了GCNMOS的基本原理,现阶段GCNMOS已经开始利用栅体双耦合的效应以实现面积最大利用率,甚至出现了多米诺链式ESD防护结构(有机会了可以讲讲(✺ω✺))。

上期讲了最基本的GCNMOS的工作原理,这期作为一个补充,拓展一下现阶段一些先进的GCNMOS设计和GCNMOS在设计中需要注意的地方。

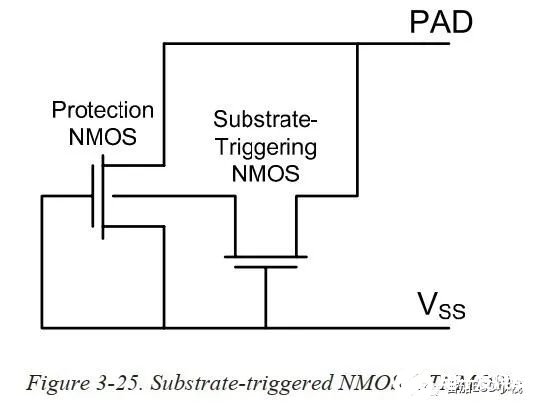

上期讲解的主要是栅触发GCNMOS,还可以通过体触发实现ESD防护。这类NMOS被称为STNMOS(Sub-strate triggering NMOS),如图一所示。

图一.STNMOS示意图。

这类NMOS是将部分电流注入到Protection NMOS的衬底中,协助开启Protection NMOS中的寄生NPN三极管(前面的章节已经讲过NMOS中存在的NPN三极管)。体触发便是将维持电流Ih注入寄生三极管的基级,这样不需要Drain与substrate间形成雪崩击穿便可将三极管导通,同样能降低trigger voltage 同时因为其还是利用三极管形成泄放通道,STNMOS的TLP曲线还是会表现出微弱的snap-back特性。又因为不需要从沟道泄放ESD电流,STNMOS本身的鲁棒性要强于GCNMOS。

相对于Protection NMOS而言,Substrate Triggering NMOS的尺寸要小很多,这样确保了两者的开启先后顺序。两者的一次击穿电压相同,但是Substrate Triggering NMOS的trigger voltage要小于Protection NMOS的trigger voltage,确保先于Protection NMOS开启。然后进入holding状态将维持电流Ih注入Protection NMOS的衬底中,促使其直接进入导通状态。Substrate Triggering NMOS的TLP特性决定了Protection NMOS的TLP特性。

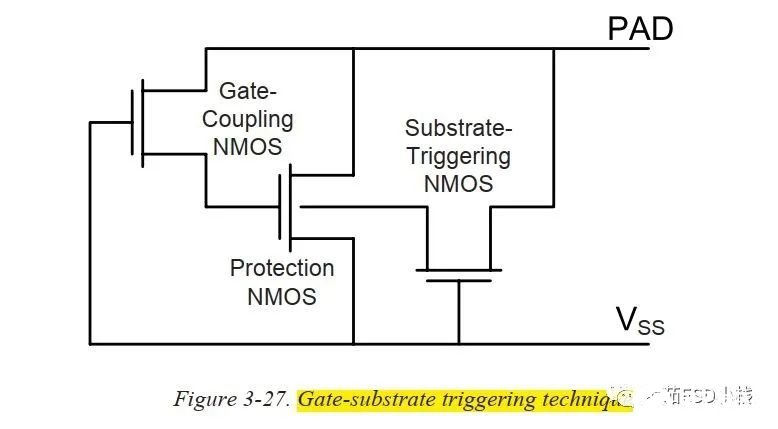

因为体寄生三极管与沟道并不冲突,将体触发与沟道导通进行结合。便有了Gate substrate triggering NMOS,如图二所示。

图二.Gate-Substrate triggering NMOS

这种ESD保护电路的原理便是同时利用了沟道与寄生三极管作为泄放通道。GCNMOS的维持电压Vh开启Protection NMOS的沟道,Substrate Triggering NMOS将维持电流Ih,注入衬底开启三极管。这样能大大提高Protection NMOS的导通效率。相当于一个NMOS与一个NPN同时进行ESD泄放。同时衬底的电位还能降低NMOS的阈值电压,更利于开启。

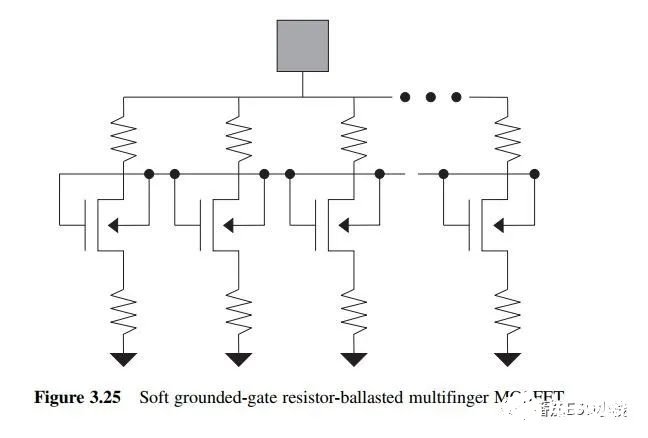

图三.多指“软”镇流电阻GGNMOS。

该结构是利用了GGNMOS发生snap-back后的维持电压vh作为下一级NMOS的沟道开启电压。当最外侧的GGNMOS优先开启后,维持电压开启后一极的NMOS沟道,以此类推形成链式ESD防护结构,而该结构中的电阻为镇流电阻,能使得电流均匀分布(这里面的技术细节有机会再讲 (*╹▽╹*))。

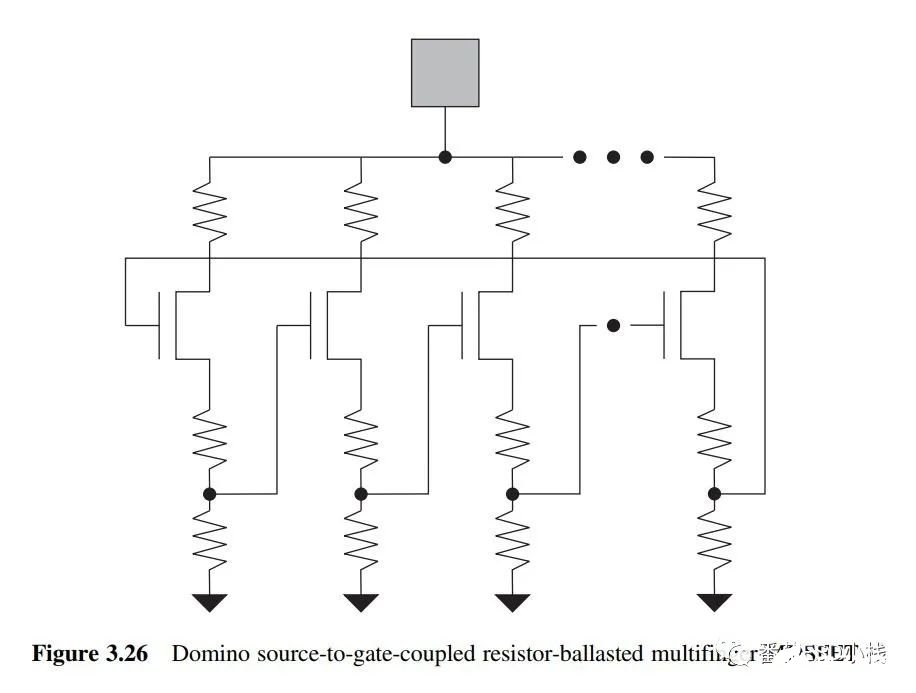

图四.多米诺ESD防护结构。

该结构也是链式ESD防护中的一种,利用source的压差开启下一级的GCNMOS。因为电路的趋肤效应,这种链式结构一定是最外侧的NMOS先开启,然后最外侧NMOS产生电压,由外及内链式开启,就和多米洛骨牌一样,被开启后继续开启下一个。而source端的电阻起到了分压的作用,将ESD电流转换为电压,形成GCNMOS。

虽然GCNMOS的电路结构比较简单,但是针对不同的应用场合会有不同的lay out方式,而且针对ESD防护的布轨问题也要针对不同应用场景进行单独设计。

审核编辑:黄飞

-

ESD保护方法的对比分析2011-07-05 5482

-

步进电机与伺服电机对比分析2021-02-05 2006

-

LTE与WiMAX对比分析哪个好?2021-05-31 1951

-

CPLD与FPGA对比分析哪个好?2021-06-21 2818

-

STM32和Arduino对比分析哪个好?2021-11-04 6020

-

CPLD与FPGA的对比分析哪个好?2021-11-05 2509

-

异步通信与同步通信对比分析哪个好?2021-12-16 1065

-

DRAM和SRAM对比分析哪个好?2022-01-20 2195

-

深亚微米ESD保护器件GGNMOS性能分析与设计2009-12-14 796

-

SPWM调制方法对比分析2009-07-06 14299

-

WLAN与WPAN的QoS机制对比分析2009-08-04 1161

-

ESD保护元件的对比分析及大电流性能鉴定2009-12-30 3255

-

小型PLC对比分析2012-04-27 1021

-

ESD静电保护元件对比(压敏电阻/TVS/ESD静电二极管)2022-07-05 5486

-

浅谈ESD防护设计—NMOS的妙用(一)2023-05-16 20405

全部0条评论

快来发表一下你的评论吧 !