Cortex-M内核的软件复位方式

描述

这里只讨论内核的软件复位方式。像STM32的备份域复位里面也有软件复位,则不在本文讨论范围。额外提一句,上电复位是完整复位芯片所有东西,包括内核、debug部分、外设、中间逻辑电路状态(模块外部的逻辑电路状态,如果没有复位,也会影响到下次运行),因此需要确保做完全复位时候,应该使用上电复位。

一、cortex-m3

图1来自cortex m3编程手册

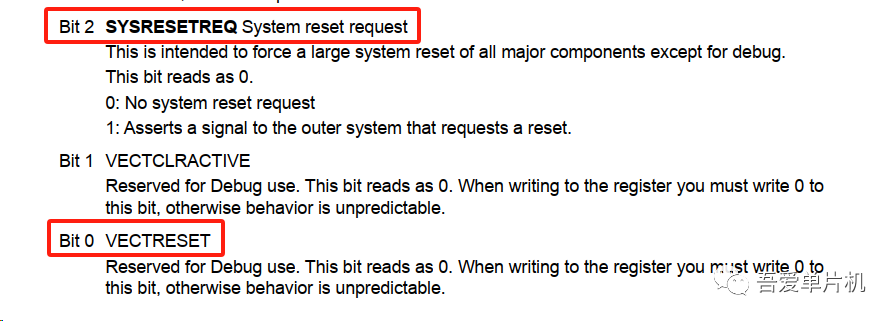

(1)SCB_AIRCR寄存器,VECTRESET位

该位只复位内核,不复位debug部分

(2)SCB_AIRCR寄存器,SYSRESETREQ位

该位一般叫做系统复位,该位定义为会复位内核,不复位debug部分,至于是否复位其他部分,比如外设,则由具体的芯片来实现

图1

二、cortex-m0

图2来自cortex m0编程手册

(1)SCB_AIRCR寄存器,VECTRESET位

cortex-m0没有提供这个位,也即cortex-m0没有提供单独复位内核的定义

(2)SCB_AIRCR寄存器,SYSRESETREQ位

参考cortex-m3

图2

三、其他参考

以下图3 图4来自 Cortex-M3-Definitive-Guide-EN.pdf

图3

图4

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Cortex-M 内核中断/异常系统、中断优先级/嵌套 详解2023-09-27 4040

-

Cortex-M内核使用FreeRTOS特别注意事项2023-09-19 1720

-

瑞萨Cortex-M内核RA MCU的RT-Thread BSP制作教程发布2023-09-18 1730

-

stm32软复位 内核复位和系统复位2023-08-01 7047

-

基于32位Arm Cortex-M内核N32系列MCU应用2023-03-28 1971

-

分析ARM Cortex-M内核复位启动过程2023-03-20 3996

-

软复位操作《Cortex®-M0+等内核通用》2022-01-12 1019

-

ARM Cortex-M内核的相关资料推荐2021-12-27 1763

-

怎样去使用Cortex-M内核中的精确延时方法呢2021-11-30 1479

-

Cortex-M内核的GCC编译器2021-08-24 1508

-

Cortex-M内核的MPU内存保护单元2020-03-04 4915

-

关于STM32与Cortex-M内核系列的介绍(2)2018-07-05 5507

-

Atmel Studio 6软件中如何调试ARM Cortex-M2018-07-04 4903

全部0条评论

快来发表一下你的评论吧 !