常用的ESD保护器件及原理

EMC/EMI设计

描述

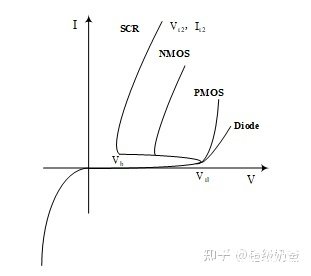

常用的ESD保护器件主要有Diode、Resistor、P/NMOS、BJT、SCR等,因其具有雪崩击穿、雪崩与注入等特性,能够瞬间进入低阻态,故具有良好的电流泄放能力,可以作为ESD防护器件。这类器件在电应力下的I-V特性示意图见图1。

图1 常用ESD器件的I-V曲线示意图

1. Diode

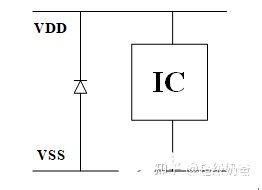

在ESD设计中,Diode是一种常见的器件。图2为Diode的一种典型应用情况,在VDD相对于VSS发生Positive ESD Pulse时,Diode发生雪崩击穿并释放ESD电流,从而保护内部电路不受ESD影响。但由于二极管完全通过雪崩击穿释放ESD电流,在大电流下器件的功耗很大,因此这种模式下二极管的抗ESD能力往往很低,器件的微分电阻也较大;而在VDD相对于VSS发生Negative ESD Pulse时,该Diode为正偏并释放ESD电流,由于二极管的正向导通电压很小,此模式下器件的功耗很小,因此其抗ESD能力非常强。

图2 Diode保护电路图

由于Diode在正偏和反偏两种状态下的ESD能力差别非常大,因此目前在使用二极管作ESD保护器件时往往会采用非常大的器件面积提升二极管反偏状态下的ESD能力,如此一来,缺点是非常明显的,它增大了ESD器件的面积占用,更为严重的是,对于高频引脚而言,此方式会带来较大的寄生电容,使引脚的频率特性变差。

2. MOS & BJT

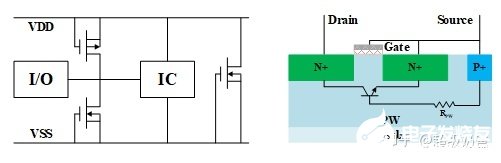

图3 MOS器件作为ESD防护器件电路图 图4 GG-NMOS结构及等效线路图

MOS与BJT用于ESD放电保护原理基本上是一样的,均是通过寄生的BJT来释放ESD电流。因CMOS使用最为广泛的工艺之一,所以MOS器件成使用最为普遍的ESD保护器件。采用MOS器件作为芯片的ESD防护架构示例如图3所示。为防止ESD器件在芯片正常工作时导通,MOS的栅极总是采用关断的连接方式,即栅接地的NMOS(Gate-Grounded NMOS,GG-NMOS)和栅接电源的PMOS(Gate-VDD PMOS,GD-PMOS)。GG-NMOS的等效电路如图4所示,其ESD应力下的I-V曲线示意图如图1所示。

当漏端相对于源端发生Positive ESD Pulse时,漏端N+/Pwell结雪崩击穿,击穿产生的空穴电流将通过Pwell流至P+,并在Pwell的等效电阻Rpw上产生压降,当该压降大于寄生NPN器件的BE结正向导通电压时,寄生的NPN器件即可导通,此时的电压即为器件的触发电压Vt1,在此之后,由于寄生NPN器件的导通及其放大作用,使器件漏端电压不需要很高的电压即可维持大的电流,因此I-V曲线会出现折回(snapback)现象和负微分电阻现象,即在某段电流范围内,器件两端电压随着电流的增大反而减小。

当电流增大到某一值时,由于器件两端的电压不可能无限下降,以及器件内部的寄生电阻作用,负阻现象转变为正阻,这一转变过程中器件两端的最低电压即为器件的维持电压Vh,它表征器件能将ESD Pulse钳位的最低电压。在电流非常大时,器件内部产生的热量将使器件内部由热产生的载流子数远大于雪崩击穿和注入的载流子数,并且温度越高,热产生的载流子数量越大,进而形成正反馈,因此曲线会再次出现折回,该点的电压和电流分别为器件的二次击穿(热击穿)电压Vt2和二次击穿电流lt2,它们分别表征器件发生损毁时的电压和器件最大耐受电流。最终,器件将由于温度过高而导致永久性损坏。而在漏端相对于源端发生Negative ESD Pulse时,电流可通过正偏的源端P+/Pwell/漏端N+二极管释放。

与NMOS相比,PMOS通过体内寄生的PNP型BJT器件进行电流泄放,其电流放大系数远低于NMOS中寄生的NPN型器件。因此,如图所示,PMOS器件可能没有折回现象,考虑到器件的防护效率,PMOS的使用远没有NMOS普及,一般只作为电源VDD与I/O引脚之间的防护。

3. Resistor

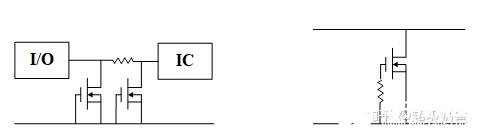

图5 保护方案中的限流电阻 图6 GG-NMOS结构中的栅极电阻

Resistor不单独用于芯片的ESD保护,它往往用于辅助的ESD保护,如芯片Input第一级保护和第二级保护之间的限流电阻。如图5,当ESD电流过大,第一级ESD器件难以将电压钳位至安全区域时,第二级ESD器件的导通将使其与电阻分压,从而进一步降低进入内部电路的电压。又如用于GG-NMOS的栅电阻,如图6所示,NMOS的栅极通过一电阻接地,而非直接接地。如此一来,在NMOS漏端发生正向的ESD脉冲时,由于NMOS的漏一栅电容,会使得器件的栅极耦合出一正的电势,该电势会促使NMOS的沟道开启,从而起到降低NMOS在ESD应力下触发电压的目的。

4. SCR

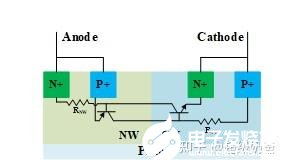

图7 SCR结构及等效线路图

SCR器件是除正向Diode外抗ESD能力最强的器件。它的结构如图7所示,当阳极出现Positive ESD Pulse时,Nwell/Pwell结发生雪崩击穿,击穿产生的电子电流和空穴电流分别流过电阻RNw和Rpw,使PNP器件和NPN器件开启,阳极的P+注入大量空穴,阴极的N+注入大量电子,注入的空穴成为NPN器件的基极电流,注入的电子成为PNP器件的基极电流,正反馈过程得以形成,使Nwell和Pwell均出现强烈的电导调制效应,继而降低器件两端的压降。因此,SCR器件的维持电压往往很低,并由此导致其抗ESD能力非常强,微分电阻也非常小。在阳极出现Negative ESD Pulse时,电流可通过正偏的阴极P+/阳极N+释放。

由于这种SCR的触发要靠Nwell和Pwell结的击穿来实现,在CMOS工艺中,其击穿电压大约有几十伏,远高于一般器件的栅氧击穿电压,达不到ESD防护的效果。因此对于低压CMOS芯片而言,SCR的触发电压需要通过一些方法降低,以满足芯片的保护要求。

SCR的高It2使得器件可以以很小的宽度达到芯片的抗ESD要求,因此使用SCR器件可以有效的降低由ESD器件带来的寄生电容,这一点对于RF芯片的ESD设计非常有利。

5. 各种器件的ESD性能比较

基于普及度较高的CMOS/BCD工艺,无论是低压或者高压应用来说,单位面积的ESD防护能力大致如下:SCR>MOS>Diode(反向击穿)

审核编辑:黄飞

-

ESD保护器件ESDAxxL系列规格书2025-03-24 366

-

ESD保护器件的工作原理2024-11-14 4579

-

ESD静电保护器件的特点及选型2024-01-03 1706

-

静电保护器件ESD是什么?如何选型?2023-02-27 7869

-

ESD保护器件 的应用与选型2022-06-06 25813

-

ESD保护器件的应用与选型2022-05-04 38388

-

ESD保护器件的选型与应用2022-03-12 2641

-

ESD保护器件的种类及应用2021-04-02 2730

-

一种常见的ESD静电保护器件2021-03-11 3271

-

新型TVS ESD 系列保护器件2020-07-22 1125

-

ESD静电保护器件的特点2018-01-26 4904

-

如何正确的选择ESD静电保护器件?2017-06-27 5714

-

常用四大类过压保护器件选型攻略2012-05-18 6569

-

USB接口的ESD保护器件要求2008-07-22 5775

全部0条评论

快来发表一下你的评论吧 !