什么是电平转化电路 电平转换器原理分析

描述

最近做PD电路时,需要将数字的PD信号(数字电平0.9V)转化为模拟的VDD(1.2V至1.8V)信号,所以需要用到一个电平转化电路,所以看看学习了一下什么是电平转化电路。

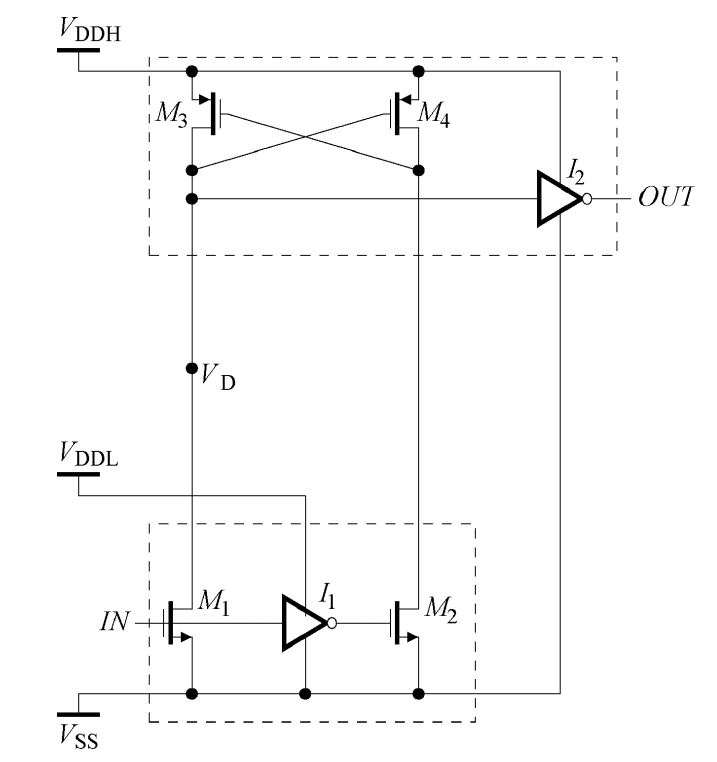

上图是简单的Level Shifter,其作用是将电平从0~Vin转换到0~VDDH。具体工作原理如下:

当Vin为0时,Vg2为1,M2导通,将M2的D端电压拉低至0,然后M3导通,将VD充至VDDH,通过反向器最终输出0。

当Vin为1时,M1导通,VD被拉至0,通过反相器最终输出VDDH。

但是你管子尺寸设置得不够好,该电路是没法正常工作的。

在刚刚Vin为0时,给我们的初态是VD=VDDH,VDM2=0。不妨从这个状态开始分析,假设此时来了一个高电平Vin:

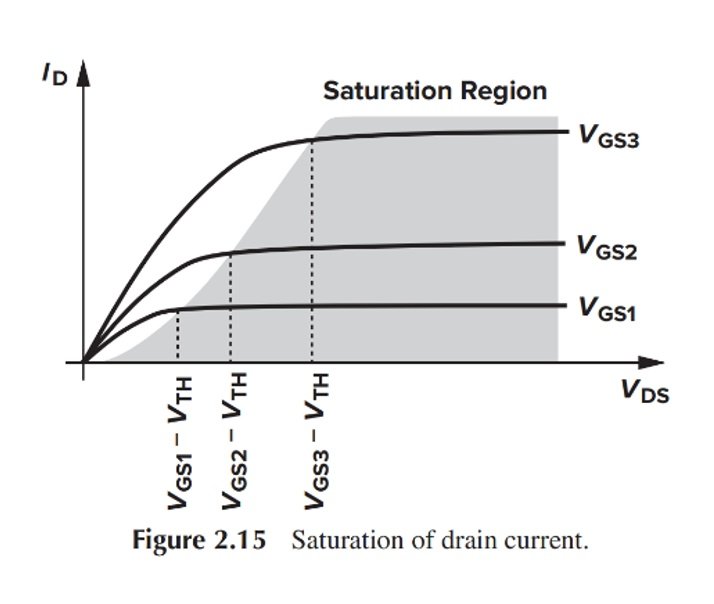

那么M1导通,VD拉到0。让我们把这个过程放大一万倍,最关键的地方就在VD被拉到0这个过程。事实上,M1导通以后,M3也会立马跟着导通,也会有电流的。如果那这俩都导通都有电流,VD电压怎么办?M3的Vgs此时可一直都很大,一直都是VDDH,之前关断是因为VDS为0,现在你M1一导通,但凡把VD往下拉一点,使得M3的VDS从0开始增大了,他马上进入线性区。

看mos管关于vds和id的图;由图中可以看出,此时M3在深线性区,电流很小;而M1处于饱和区,电流比较大。正是这两个电流的差值,让VD这个点的节点电容放电,才使得该点电压能够继续降低的。随着这个放电的继续,VD会越来越低,根据上面那个图,考虑沟道长度调制效应,M1的Vds越来越小,M3的Vds越来越大。这就导致M1电流会越来越小,M3电流会越来越大,但是M1的电流始终比M3大,这保证了VD这个点的寄生电容能持续被放电。

系统会一直保持这个状态。第二种情况,如果他俩电流还未相等,VD电压就已经比VDDH低了一个VTHP,那么M4导通,M2漏端拉高,M3关闭,VD只放不充,很快放到0,然后经过反相器输出VDDH。

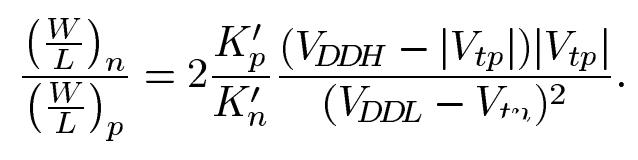

按照常规理解分析:只要n管的宽长比比p管大得多,使得n管的VDS足够小,就能满足VD的电位越来越低,使得m4管导通,使得VD电位到达地。

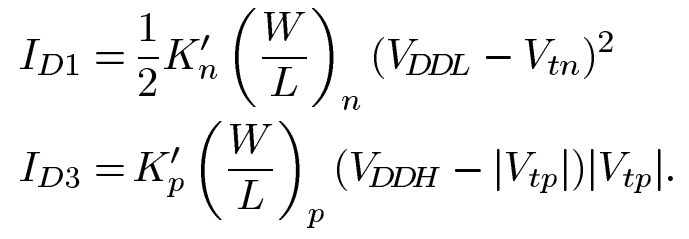

临界的宽长比分析:当VD下降到VDDH-VTHP时;m1的饱和区电流与m3管在深度线性区的电流相等;

得到的尺寸比,正好就是我们保证电路能正常工作的最小尺寸比

只要n管的宽长比比最小尺寸比大,就可以保证VD的电位正常拉低。

审核编辑:黄飞

-

国产电平转换器双雄登场!GS0104/GS0108 如何破解多场景电压适配难题?聚洵半导体科技 2025-12-22

-

SIM卡接口电平转换器2025-02-18 219

-

双向逻辑电平转换器电路图分享2024-02-19 6152

-

电平转换电路原理分析2023-12-11 2425

-

SIM卡接口电平转换器-NXT45562023-02-09 457

-

如何将MAX13030E–MAX13035E逻辑电平转换器用作存储卡电平转换器2023-01-23 1601

-

电平转换电路原理分析#电路设计学习电子知识 2022-09-23

-

mos管电平转换电路原理与mos电平转换电路分析2021-04-09 57619

-

digilent逻辑电平转换器介绍2019-11-29 2695

-

新唐科技I²C系列电平转换器介绍2019-11-19 2441

-

电平转换电路解析2017-11-28 1866

-

电平转换器,电平转换器原理和相关电路分析2010-03-24 8653

-

具有多种电平输出的DCDC转换器2009-12-13 1765

-

负-正电源逻辑电平转换器电路图2009-04-02 1631

全部0条评论

快来发表一下你的评论吧 !