基于0.18μm CMOS工艺的高响应度太赫兹探测器线阵

RF/无线

描述

据麦姆斯咨询报道,近期,江苏大学和中国电子科技集团公司第五十五研究所的科研团队在《红外与毫米波学报》期刊上发表了以“基于CMOS的高响应度太赫兹探测器线阵”为主题的文章。该文章第一作者为白雪副教授,通讯作者为徐雷钧教授。

本文将太赫兹自混频功率探测电路、片上电压放大电路和片上天线相结合,采用电磁场与电路联合仿真方法,在不改变制造工艺情况下,通过标准CMOS工艺完成太赫兹线阵的设计。经过设计、仿真、优化及流片,实现了1 × 3探测器线阵。

太赫兹探测器基本原理和设计考虑

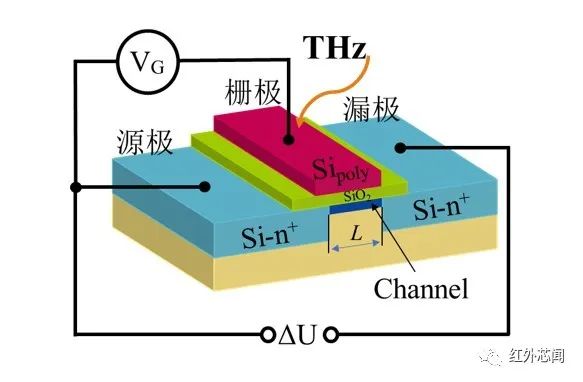

M. Dyakonov和M. Shur提出场效应管借助二维电子气沟道的分布效应,能够实现对超出晶体管自身截止频率的太赫兹波信号进行有效平方率检波,输出与输入功率成比例的响应电流或电压。可利用非准静态模型对太赫兹信号在场效应晶体管中的作用原理进行分析,如图1中金属氧化物半导体场效应管(MOSFET)模型所示。

图1 NMOS晶体管的太赫兹辐射分析模型

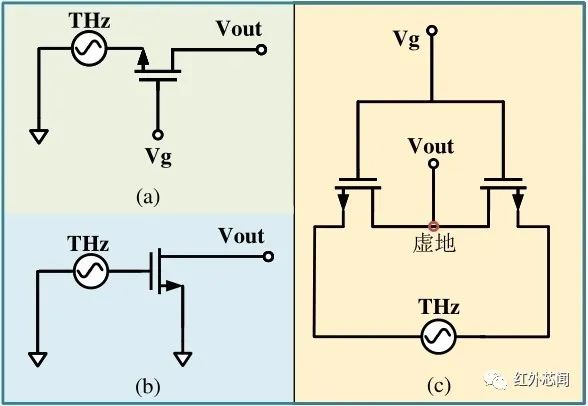

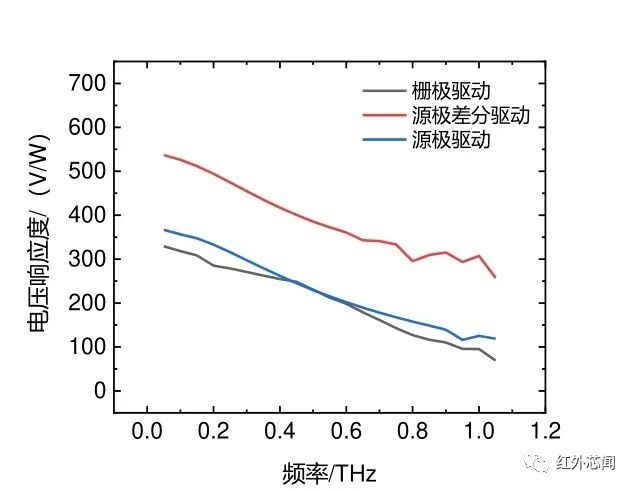

目前,最受追捧的三种自混频功率探测电路结构主要包括:源极驱动电路(a),栅极驱动电路(b)和源极差分驱动电路(c)(如图2)。电路(b)原理图中的栅极驱动省略了栅极的偏置电压。其中,源极驱动电路和栅极驱动电路都是从MOSFET的单端输入,在沟道内发生自混频后在漏极输出混频信号。三种电路结构的响应度仿真对比如图3所示,从仿真结果可知源极差分驱动的配置在同等的条件下获得的电压响应度最高。

图2 自混频功率探测器电路结构(a)源极驱动;(b)栅极驱动;(c)源极差分驱动

图3 三种自混频探测电路结构的响应度仿真对比

探测器阵列实现

电路整体结构

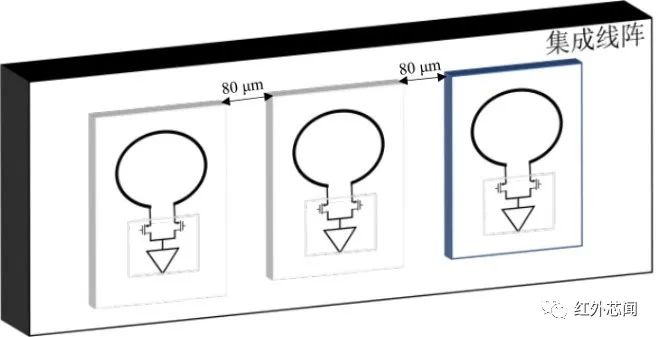

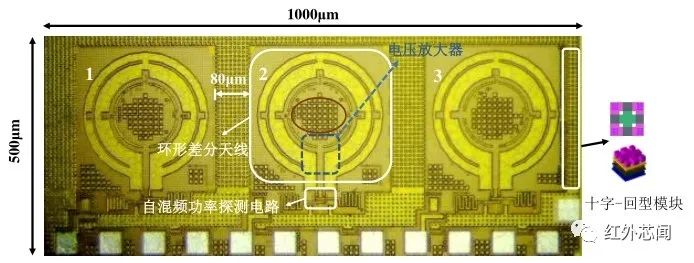

探测器阵列由3个太赫兹像素线性排列,每个像素由带交叉耦合电容的源极差分驱动自混频功率探测电路、高增益片上环形差分天线和集成电压放大器组成。各像素单元的输出相互独立,阵列规模的设计提高探测器中的像素点个数,实现高效率和高精度成像。3个太赫兹像素以80 μm的间距等间隔排列成行,共享同一栅极偏置电压和电源电压。像素之间通过地平面隔离减少像素之间天线的相互耦合。此外,差分环形天线的轴心位置需要进行接地处理,为差分MOSFET提供直流回路。

图4 太赫兹探测器线阵布局结构

片上天线设计

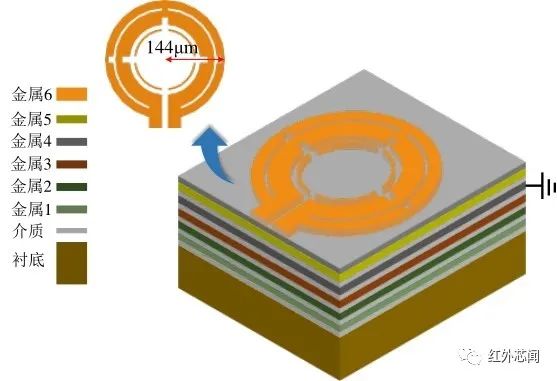

片上天线是探测器中的关键模块,需要高增益的天线接收微弱的太赫兹辐射信号。图5所示为基于0.18 μm CMOS工艺的片上天线模型。CMOS工艺包含金属层、介质层和硅衬底等物理层结构,其中金属层嵌入在介质层中。利用HFSS软件对双圆环差分结构的天线进行建模、仿真、优化。天线的辐射面选用顶层厚金属层(M6),开窗处理后的顶层金属有更好的辐射效率,其次,顶层与硅衬底距离最远,可减少信号在衬底中损耗。

图5 0.18 μm CMOS工艺物理结构和天线模型

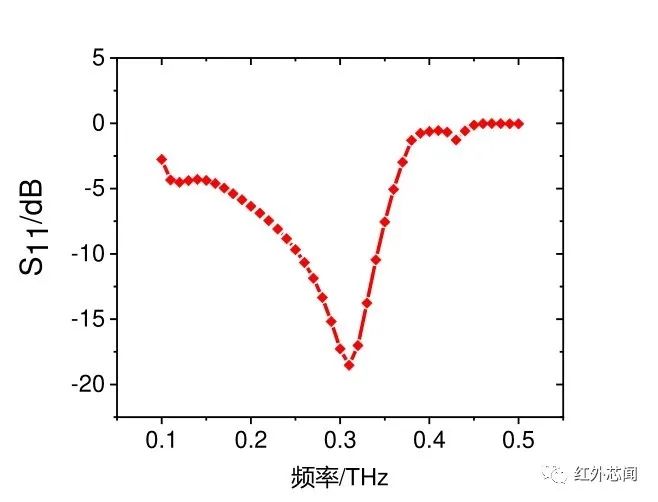

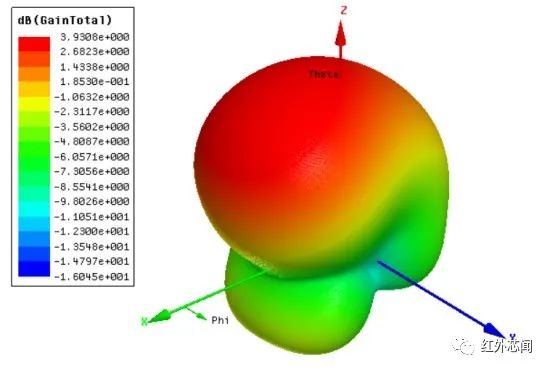

图6为天线反射系数仿真结果,在集总端口的差分激励输入下,反射系数S11的仿真结果曲线表明天线的-10 dB带宽在0.25 THz至0.34 THz范围内。图7为天线在0.3 THz的3D辐射方向图,顶向辐射的最大增益为3.9 dBi。天线的高增益性能可以为探测器的高响应度提供有力保障。

图6 天线的S11仿真结果

图7 天线的3D辐射方向仿真结果

电路设计

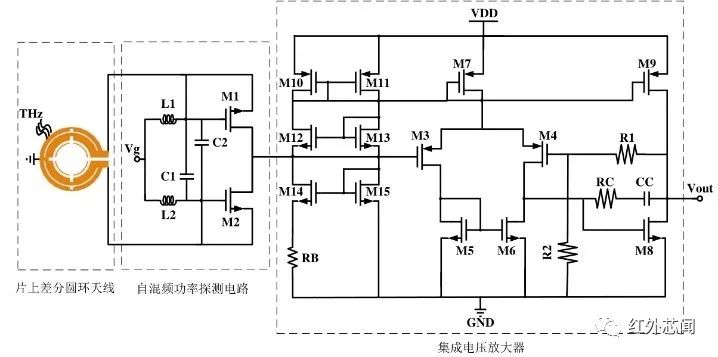

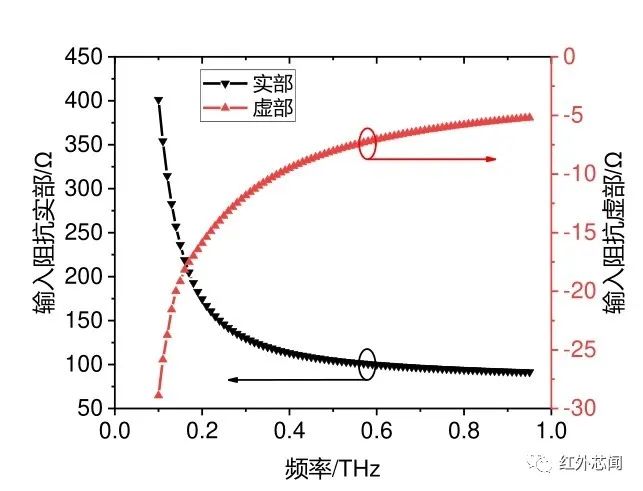

本文采用的探测器像素单元电路如图8所示,改进的源极差分驱动结构作为太赫兹自混频的核心结构。太赫兹信号在NMOS晶体管沟道内呈指数衰减混频,即使在最小的栅极长度的沟道中,诱导电子密度振荡的整流也只发生在沟道的开始处,剩余的通道长度仅作为寄生电阻和电容,会降低探测器的响应。本文中自混频MOSFET使用工艺所能达到的最小长度0.18 μm。电路的阻抗仿真结果如图9所示,在0.3 THz时阻抗为(125~11.83 j)Ω,可实现天线与电路之间的阻抗匹配。

图8 单像素电路原理图

图9 自混频功率探测电路的输入阻抗仿真结果

集成电压放大器对自混频探测电路的输出信号进行放大处理,提高探测系统的响应度,增强系统的驱动能力。低噪声、高输入阻抗是集成电压放大器要具备的性能,因为自混频功率探测电路的输出是微弱的直流信号,低噪声和高输入阻抗才能保证精确捕获输出的电压响应信号。

图10所示为基于0.18 μm工艺的探测器芯片显微照片,图中显示了阵列的整体布局,对各模块进行了标注。放大器的版图采用M1-M3层的金属走线,位置在天线地平面下方,图示中用蓝色区域标识出其相应物理位置。

图10 太赫兹探测器阵列版图

实验测试结果

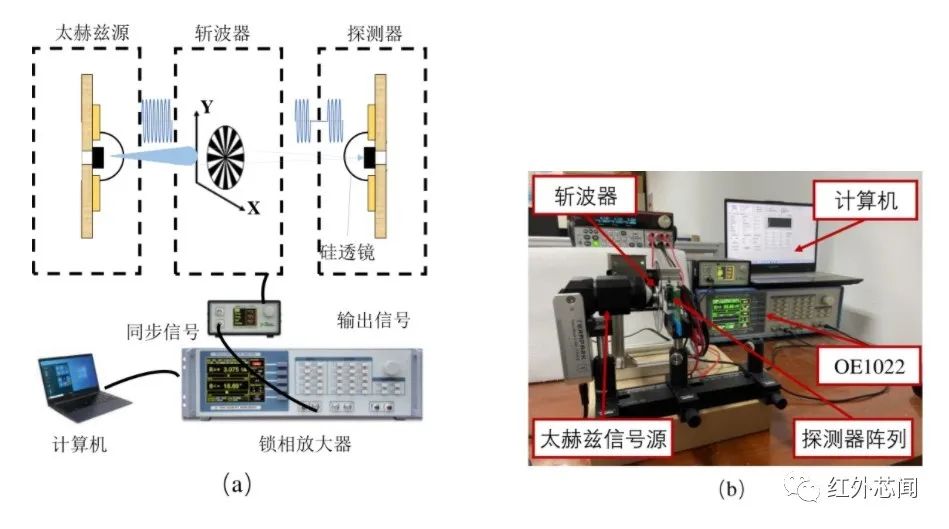

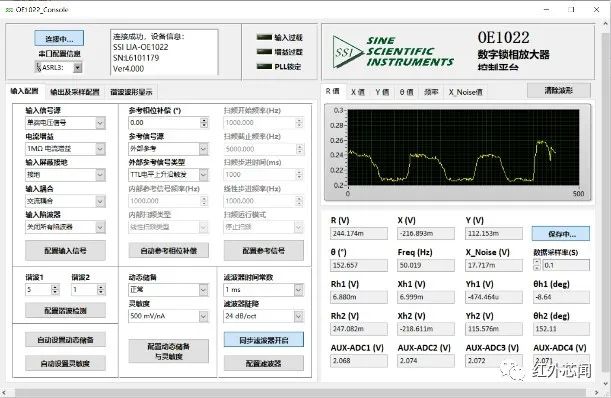

首先将探测器芯片绑定到芯片外围扩展电路板上,然后利用斩波-锁相技术测量探测器阵列。由太赫兹信号源、斩波器、锁相放大器和计算机搭建如图11所示的太赫兹探测器测试环境。测试内容分为静态测试和动态测试。静态测试为寻找自混频功率探测电路的最佳栅极偏置点,保证探测器工作在最大效率状态。然后在最佳状态下进行响应度和噪声等效功率的测试,对探测器的性能进行表征。动态测试为测试探测器对不同材质物体隔挡时的输出响应变化。测试中所使用的太赫兹信号源为某公司所设计的300 GHz的集成太赫兹源。在测试之前使用以色列的手持式Ophir NOVA II功率计结合3A-P-THz探头进行对太赫兹源的功率测试,测试环境如图12所示。

图11 测试平台的搭建(a)测试系统的框图;(b)测试平台的实际环境

图12 太赫兹信号源的功率测定

对于静态测试,首先将太赫兹信号源频率和功率进行固定,使其保持聚焦状态。固定太赫兹信号源与探测器的相对物理位置后,关闭太赫兹信号源的电源,给探测器阵列芯片上电,在锁相放大器上可观察到0.18 V左右的电压输出。此现象可能为芯片内部或PCB板级电路导致的输出直流偏移。为了继续验证探测器是否存在响应,打开太赫兹信号源,为探测器提供信号辐射,锁相放大器的输出电压会增加,表明探测器是有响应的。后续的实验测量和测量结果均以输出电压的相对值作为探测器的响应输出。

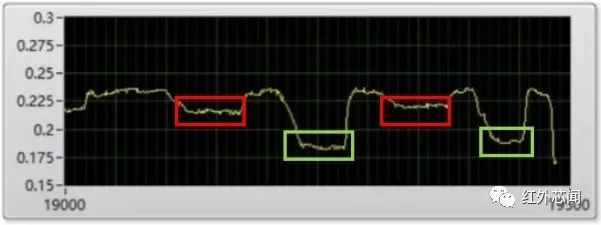

对于动态测试,保证测试平台维持电压响应度的测试配置,在太赫兹信号源和太赫兹探测器之间加入隔挡物,例如金属薄板、A4纸等,观察输出电压的变化。如图13所示,当放置隔挡物之后由于探测器接收的太赫兹功率降低,所以输出电压会降低,图示清晰的反映了这一过程。通过更换不同的隔挡物,可发现探测器对不同隔挡物的响应程度不同,图14反应了动态测试的结果。

图13 锁相放大器显示的太赫兹探测响应波形

图14 对不同隔挡物(A4纸和铜板)的透射结果

结论

本文采用0.18 μm CMOS工艺完成高响应度探测器线阵的制备。通过分析对比了几种常用的自混频功率探测结构的性能,选择源极差分驱动结构作为自混频功率探测结构,改进后的带交叉耦合电容的结构增强太赫兹信号在小尺寸晶体管沟道内的强度,提高晶体管漏极和源极间的输出电压,从而提高探测器的响应度。通过结合电磁仿真与电路仿真,完成高增益片上环形差分天线、源极差分驱动自混频功率探测电路和集成低噪声电压放大器的联合仿真,优化模块间的级联使探测器系统整体性能达到最优。不修改制造工艺情况下,在0.5 mm × 1 mm的面积上实现1 × 3线阵的制备,其中包括焊盘和片上天线。在室温条件下搭建测试平台对探测器阵列芯片进行测试,当栅极偏置电压为0.42 V,晶体管工作在亚阈值区,此时该探测器的最大响应度可达43.8 kV/W,最小NEP为20.5 pW/Hz1/2。探测器阵列芯片的动态测试表明该探测器阵列可区分不同材质的物体。实验测试表明本文提出的探测器可进一步应用到太赫兹探测成像系统中,待完善探测器响应信号数据处理电路和成像算法后,可实现太赫兹探测成像。值得注意的是,采用的多像素探测方法在于提高检测速度,但由于缺少通道间的相位信息,相较于包含响应相位信息的外差混频探测方式,其灵敏度主要依赖于单个天线单元的增益,响应信号中也只包含幅值信息。

审核编辑:黄飞

-

CdZnTe探测器γ射线响应及稳定性研究2010-04-22 2428

-

0.18μm CMOS工艺的2.5GHz环形压控振荡器研究与设计2013-04-11 2232

-

浅析太赫兹技术应用2019-07-03 3000

-

如何利用0.18μm CMOS工艺去设计16:1复用器?2021-04-09 1326

-

如何采用0.18μCMOS工艺模型进行开环跟踪保持电路的设计?2021-04-20 1732

-

CMOS探测器在射线检测中的设计应用2010-03-20 2717

-

超高灵敏度石墨烯太赫兹探测器研究获突破2017-03-22 1826

-

太赫兹频段探测器也已渐成为宇航探测的标配2019-02-25 4771

-

虹科太赫兹实时成像系统正式上线2021-08-10 3205

-

国外团队开发激光脉冲高功率太赫兹发射新模型2023-03-01 1513

-

天津大学构建新型红外-太赫兹宽谱探测器2023-04-14 1670

-

超快太赫兹探测器2023-05-04 639

-

化学水浴法合成PbS光电探测器的红外响应研究2023-07-27 3155

-

InSb焦红外探测器平面芯片的响应率提升研究2023-08-07 1395

-

光电探测器PMT、APD、CCD、CMos、ICCD、EMCCD2025-09-16 2156

全部0条评论

快来发表一下你的评论吧 !