芯片异常漏电几种情况分析

描述

通常在理想状况下,如果mos管关断时是不流过电流的。但漏/源与衬底之间是两个pn结。即使mos管没有沟道,漏源之间还是有反向的饱和电流,这就是所谓的漏电流。由于漏电流的存在,整个电路的静态功耗会有所增加.正常一般都在uA级别吧.

下面时我能想到的异常漏电几种情况:

Ø 门电路的输入端悬空,有可能导致PMOS和NMOS同时导通,存在短路电流,如果MOS管的尺寸越大表现出来的漏电流就越大.

Ø buffer输入高阻态,电位不固定.

Ø 发生了latchup .

Ø 之前遇到foundry rule 不完善,导致添加AA(OD) dummy 不合理导致漏电问题.

Ø 芯片物理性的损坏.

这次芯片回片测试时发现系统进入sleep模式后漏电异常,几个毫安级.不正常!分析发生latchup的可能性不大,大概率时有门级输入悬空或高阻态.

产生输入floating 或高阻,在电路或版图上有哪些场景?

先说floating gate,其实这个地方是有坑的,我们习惯认为这个问题可以在drc 或lvs 验证中cover住.

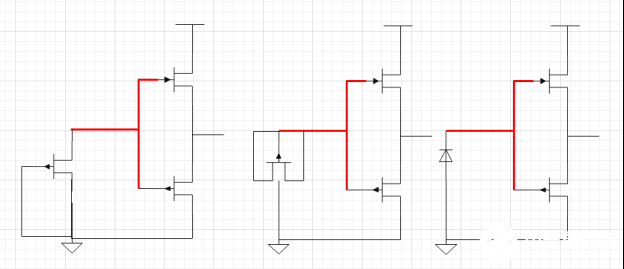

But意外往往都是这么发生的.根据经验教训下面有些场景在drc lvs 中无法检查到.上图画visio图不熟练:

我们认为红色gate 输入端虽然接diode或ggnmos 或mosbase dio但电位还是不固定的,仍然floating的,但是drc lvs 都不会报错.风险越留到后面,修改的代价就越大.设计阶段需要介入排除.

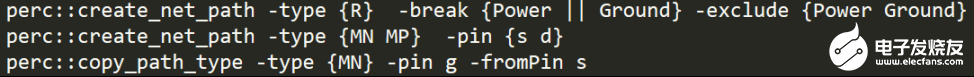

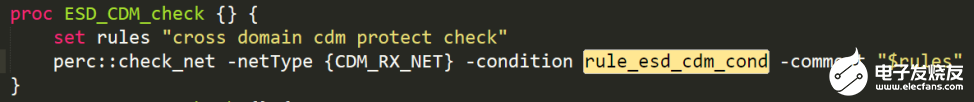

对此问题可以定制perc rule 排除.

我们这个问题有些相似,原因是sleep 模式关掉LDO 输出,但是没有下拉到地.后一级buffer 电压常在不掉电,从而导致漏电发生,检查方式需要检查是否有net 跨不同的电源域,电路设计分析前后级电源上下电关系判断是否有风险.

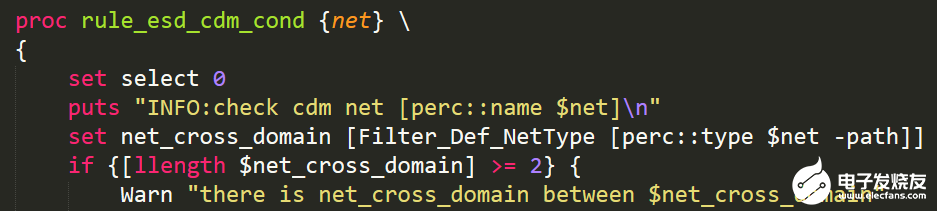

对此问题也可以定制perc rule 排除.

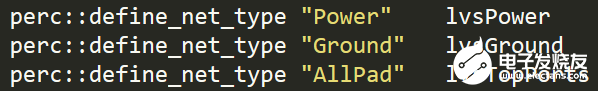

简述下流程:

定义net type

芯片回片后出现漏电,定位常见的方式时EMMI(也就是微光拍照)闳康宜硕等厂家都可以提供服务. 从照片看亮点位置有亮点说明有大的漏电流.

总结:使用第三方IP 时也会遇到相同的问题,都会有输出高阻态.有必要加上预防措施.风险排除越早,代价越小.认为有风险就要指定排除措施,并落实到flow中.

审核编辑:黄飞

-

芯片漏电跟哪些因素有关?2023-09-17 6125

-

几种常见的机器被黑情况2022-08-12 1426

-

STM32中Fault的异常中断有哪几种情况呢2021-10-28 2203

-

芯片漏电点FIB切片分析2021-08-05 3707

-

【经典案例】芯片漏电失效分析-LED芯片失效点分析(OBIRCH+FIB+SEM)2021-02-26 4053

-

新能源汽车SiC MOSFET芯片漏电红外热点定位+FIB解析2018-11-02 7226

-

失效分析OBIRCH热点测试2018-08-27 14124

-

ARM异常中断返回的几种情况2016-03-31 2171

-

如何应对常见的在线烧录异常情况2016-02-24 7868

-

【金鉴预警】用硅胶封装、导电银胶粘贴的垂直倒装芯片易漏电2015-06-19 6035

-

用硅胶封装、导电银胶粘贴的垂直倒装芯片易出现漏电现象2015-05-13 7247

-

光耦的异常情况分析2012-03-14 3867

-

关于配电变压器几种损坏情况的分析2009-12-11 2388

全部0条评论

快来发表一下你的评论吧 !