数模混合芯片scan chain问题解析

描述

前几天回了一位网友的贴子。这位网友的问题很经典。整理一下,也许对其他朋友有点帮助。

Q1:

目前有这样一个设计需求,该IC总体有数字部分和模拟部分组成,现在要求对数字部分插scan chain,实际芯片中数字部分很多输入/输出信号是直接连接到模拟电路,而不是连接到芯片的IO上,因为scan chain要求数字电路输入可控和输出可观察,面对这种情况,实际在插scan chain时数字部分的输入输出一般是怎么处理,欢迎各位大佬指点,小弟不胜感激

Answer:

输入:模拟到数字的信号不可控,需要和数字registered outputs mux一下提高test coverage。关键词是registered output! 这个技巧俗称scan loopback。

输出: scan的时候不希望模拟控制信号频繁上下跳动,要求把数字到模拟的输出置为static low or high。注意:有的模拟模块在scan的时候要求一直enable,对应的enable控制信号在scan时必须mux到static high。例如,部分数字是LDO供电,这部分数字在scan chain里,跑scan的时候LDO自然不能关掉。这个场景在低功耗设计中很常见。

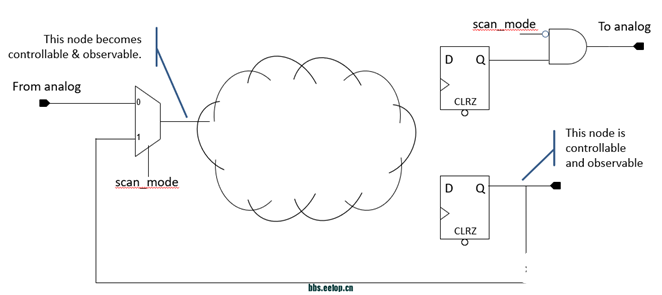

示意图如下。左边是scan loopback mux,右边是 scan tieoff。

Q2:

关于输入信号处理时参与MUX的“registered outputs ” 怎么选取的呢,这里选择哪一个register有什么讲究吗

Answer:

有讲究,首选选离得近的,不然place & route会浪费太多routing resource,还会影响 timing。 参考一下top level layout 给 digital 的 pin location

如果是PLL之类,有些 timing critical 的 output 尽量不要拿来做 scan loopback,选一些不太重要的

Q3:

有几个问题想再追问下:1.按照上述处理,是不是在真实的ATE测试时只需要控制芯片pin上的几个scan信号就能完成scan测试?那是不是可以进一步理解成任何数字电路都可以按照上述思路处理,然后最后只通过pin上的几个scan信号(不用任何PI/PO)完成ATPG测试?

2.上述处理后能保证覆盖率吗,在tmax产生ATPG时需要注意些什么?

3.在设计中有一个负沿的D触发器,在插入DFT是设置了mix_edges,最后这个负沿的D触发器串在了chain的最前面,这时会出现一个“1 Trailing edge port captured data affected by new capture violation”的违例,这种情况需要处理吗?然后又怎么处理?

Answer:

1. 是的。通常 scan 信号可以复用 SPI, I2C,需要小心。减少整个片子 pin 数量,降低 package 成本,整个片子才会有竞争力。大厂的数模混合芯片没有scan专用的pin就是这个道理。

2. 覆盖率 95% 还是可以做到的,虽然加入的 scan mux 上损失一些覆盖率,但是加入后提高了整个设计的覆盖率。

3. 如果没有 timing 问题, 不需要处理。 如果 setup 不能满足,可以降低 scan 频率。

Q4:

产生ATPG的still文件中依然会有对“form analog”和“to analog”这些信号有赋值等操作,感觉此时的still文件中不是应该就只有对scan的几个信号有赋值或其他操作吗?

Answer:

假设数字顶层是 digtop,有一堆 from_analog*, to_analog* 之类的 IO。这个 digtop 是不能直接给 ATPG tool 用的,要在外面加一个 wrapper,姑且称为 digtop_tmax 吧。 这个 digtop_tmax 的 IO 应该只包括 scan pattern 能控制的 digtop input, 以及 scan pattern 能观察到的 digtop output。 from_analog*, to_analog* 都不在 digtop_tmax 的 IO list 里。这样最后的 stil 里就不会出现 from_analog*, to_analog*

Q5:

那这个wrapper是在插scan chain完成后手动修改网表去形成,还是通过设置工具的某些命令去形成?

Answer:

这个 digtop_tmax 实际上相当于 chip_top 去掉其中的模拟部分。

如果 Cadence 里已经有 chip_top 的 symbol view,生成一个 Verilog view, 再手动例化 digtop。

嫌麻烦就完全手动

Q6:

1.这样操作是不是又要重新生成新的spf文件? 设计中from annlog 和 to analog的pin巨多,手动是不是太麻烦了 。

2.我看了下DFTMAX的ug,在第12章节讲了wrapper cores ,我在想是不是我这种类型的设计能不能在RTL阶段不做任何代码处理,在DFT时直接走wrapper cores的流程,这样具有可行性吗?

Answer:

RTL 阶段插入 scan mux, scan loopback。

跑 TetraMAX 的时候写一个 digtop_tmax 或 chip_top,仅仅用于跑 generate spf。

这里有个省时的小窍门。 scan 相关的 port 一般就 5/6 个信号。digtop_tmax 里接上这几个信号就可以了。 其他的像 from_analog*, to_analog*, ATE 根本看不到,也不需要看到。例化 digtop 的时候这些信号可以不出现在 port mapping 里,大大简化 digtop_tmax 的工作量。工具会自动把这些 from_analog*, to_analog* 当成 X 处理,这也正是我们希望的

Q7:

我们的设计数字电路大概有1500个D触发器,从测试成本和测试时间来考虑(scan 的pin可以适当多些),一般插几条chain比较合适?这里chain的条数的定义一般是怎么评估的呢

Answer:

1. 片子的 package 最多能有几个 digital I/O。 数模混合片子大部分 I/O 都是模拟,数字很少,scan pin 数量的上限就在那里,也就限制了 scain chain 的条数。如果允许,当然时多几条 scan chain 更好,减少 test time。 但是 package 也是成本的很大部分,不能随心所欲增加 digital I/O 增加 scan chain 数量。有时 package 是用户使用场景决定的,无法选大的。例如8 pin package, 内部模拟数字一大堆,也蛮常见的。

2. 为了减少 test time, 可以考虑 scan 跑得快一些。 很多时候 scan mode 时钟比 functional mode 时钟快很多倍就是这个道理

Q8:

1.之前几天仅仅是把DFT流程跑通,没有关注测试模式下timing的问题,我想问下在测试模式下,scan的时钟和scan的信号怎么约束,和function 模式结合起来约束又该如何考量(是不是要用set_case_analysis之类的命令)? 实际跑function的频率就几十M,这种测试模式下需要有at-speed的考虑吗?

Answer:

1. Timing 分析可以用 MMMC (multi-mode multi-corner)。Mode 分成两个,func_mode, scan_mode,写两个 SDC。

func_mode SDC 第一句: set_case_analysis 0 [get_port scan_mode*]

scan_mode SDC 第一句: set_case_analysis 1 [get_port scan_mode*]

scan_mode SDC 里 create_clock -name scan_clock 可以跑得快一点。如果 scan_clock 可以超过 functional clock,at-speed test 就不重要了。

很重要的一点,一定要跑 sdf 反标后仿,把所有 vector 跑一遍,确认无误。 很多时候跑 sdf 反标后仿可以发现问题。

审核编辑:黄飞

-

SCAN921025H和SCAN921226H高速LVDS串并转换芯片深度解析2025-12-29 577

-

芯片设计测试中scan和bist的区别2023-10-09 6783

-

射频与数模混合类高速PCB设计2023-09-27 960

-

是否需要补插scan chain的isolation cell?怎么插呢?2023-05-10 2668

-

MCU芯片设计了mbist、scan chain之后,功能仿真失败?2023-02-20 2531

-

知存科技数模混合存算一体AI芯片专利解析2019-12-24 8239

-

一文读懂DC/AC SCAN测试技术2017-10-26 40676

-

帮你理解DFT中的scan technology2016-06-14 26342

-

请教Chipscope和boundary chain问题2014-02-13 2993

-

数模混合SOC芯片的可测性方案的实现2011-12-12 19168

-

我的数模混合设计难点经验2011-12-02 32826

-

数模混合电路设计的难点2010-10-05 3004

-

数模混合仿真在以太网芯片设计中的应用2010-02-24 744

-

DS26522 JTAG Scan Chain Mappin2009-04-18 1095

全部0条评论

快来发表一下你的评论吧 !