异质芯片组装主流化的驱动因素和方法

电子说

描述

摘要

随着芯片复杂度的增高和摩尔定律的放缓,半导体行业正在迅速向先进封装中的异质芯片组装转型。这种转变实现了通过组件的拆分与新的架构配置下的重新集成来持续缩小线距和创新。然而也带来了显著的设计、验证、制造和供应链等方面的挑战。本文探讨了实现异质芯片组装主流化所涉及的驱动因素、方法、权衡取舍和未解决问题。

导言

50多年来,摩尔定律推动了半导体行业的发展,其核心是每两年单片硅晶圆上的晶体管数量就会翻一番。这种坚持不懈的缩小线距使芯片可以更高度地集成,性能更强,成本更低。但是,随着芯片制造技术进入10纳米以下,继续缩小线距的成本高得惊人。此外,单片系统级芯片(SoC)也遇到了***曝光范围限制、良率问题和其他瓶颈。因此,行业正在大力向2.5D和3D堆栈等先进封装中更小的异质芯片组装转变。这种方法通过组合匹配不同工艺节点和来源的组件,可以继续提升芯片的集成度、带宽、功耗和性能。然而,异质集成也给设计、验证、制造和供应链带来了重大的新挑战。工程师现在必须协同设计芯片本体、互连和封装,以实现系统层面的最佳综合。本文将探讨异质芯片组装主流化的驱动因素、方法、挑战和展望。

异质集成的驱动力

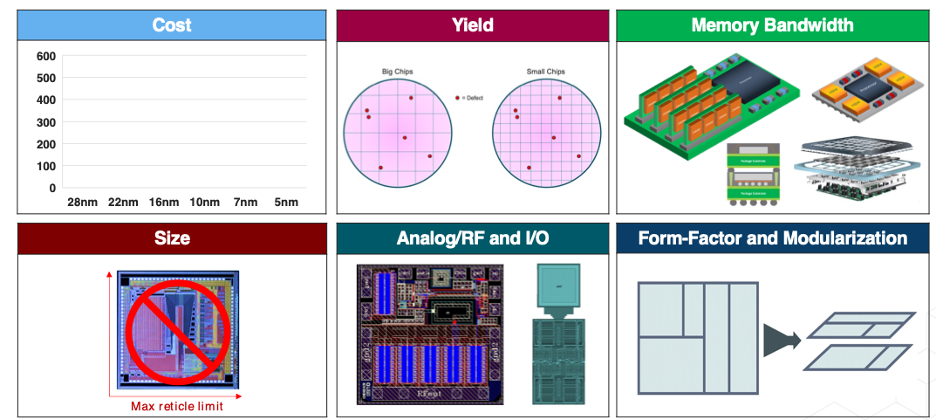

促使行业向多芯片架构转变的几个关键因素:

经济性 - 每一代领先工艺节点的成本呈指数增长,大多数芯片市场难以承受。芯片组装可以混合使用成熟的先进工艺。

良率 - 更小的芯片具有更高的良率,可降低成本。但单个故障芯片可能导致整个封装失效。

带宽 - 在封装上集成高带宽内存可获得巨大的带宽提升。

定制化 - 芯片组装可以混合不同来源的IP,并在不同产品间重复利用。

尺寸 - 新设备需要更小、更定制的封装,而非单片解决方案。

如图1所示,在摩尔定律放缓的情况下,芯片组装可提供更好的技术和经济路径。

图1:采用chiplets的理由。仅依赖摩尔定律不再是最佳路径。来源:Cadence

异质集成方法

连接芯片组装的两种主要方法:

2.5D - 芯片并排放置在interposer或载板上。硅中间器可提供高密度互连,有机载板成本更低。

3D - 芯片垂直堆叠。这节省空间但会带来热问题。

芯片可以通过线键合、微突块、硅通孔(TSV)以及UCIe、BoW等新兴接口标准进行连接。

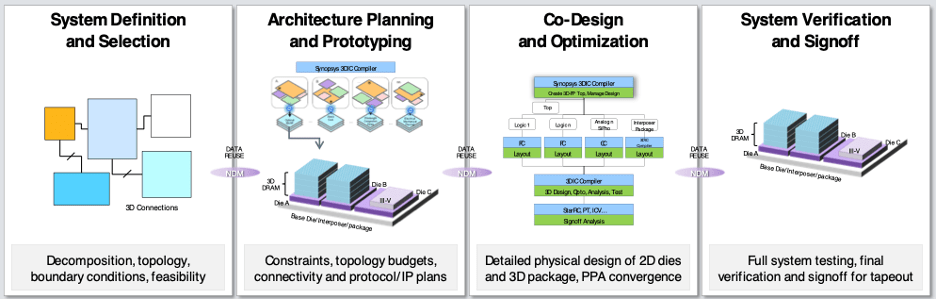

协同设计芯片、封装和互连,以实现热性能、功耗、性能和成本的最佳平衡,难度巨大。工程师必须从整体系统视角出发,而不仅仅是设计单独的ASIC芯片(图2)。

图2:多芯片系统设计。来源:Synopsys

关键挑战

异质集成前景广阔但也带来许多新挑战:

拆分 - 如何在芯片间拆分功能以实现最佳重用性、功耗、性能和良率?这需要新的架构和流程。

互连 - 芯片间通信标准仍在形成。在带宽、功耗和延迟方面存在复杂的权衡。

建模 - 准确建模完整的多芯片系统非常困难。需要Digital twins作为“黄金”参考。

噪声 - 与单片解决方案相比,芯片间会以新方式相互影响。需要广泛的联合仿真。

热特性 - 更多芯片的高密度集成会带来必须建模和处理的新热问题。

应力 - 薄芯片会弯曲变形,键合/去键合也可能损坏脆弱组件。

测试 - 测试封装芯片和裸芯片截然不同。 已知良好芯片(KGD)方法很重要。

供应链 - 芯片组装允许组件重用,但也增加了对第三方IP/芯片的依赖。

许多标准、工具和方法还在演进,以实现可靠的芯片组装、验证和制造。工程师需要广泛的新知识,涵盖多芯片设计、系统级验证、2.5D/3D封装和测试。

展望

尽管异质芯片集成非常复杂,它在摩尔定律时代结束后也可以持续缩小线距、创新和降低成本。业界正在大力开发围绕封装、接口标准、设计工具、建模、自动化和制造的可靠解决方案和生态系统。

大公司已经实现了多芯片设计,但广泛采用将取决于解决方案的成熟和成本降低。最终,基于芯片组装的架构将需要从根本上改变系统的构思、设计、集成、验证、制造和支持,横跨全球化的供应链。这是重大变革,也是半导体行业一个激动人心的新篇章。

总结

过去无止境的推进摩尔定律缩小线距的结束,推动了向异质芯片先进封装的重大转变。这种方法通过组件的混合匹配可以继续获得收益,但也给设计和制造流程带来了重大新挑战。各方正在积极开发标准、工具、方法、测试、供应链等,以实现异质集成的大规模应用,将从根本上改变半导体行业的经济模式和实践方式。

来源:逍遥设计自动化

-

3D IC背后的驱动因素有哪些?2025-03-04 1234

-

如何从生产制造环节减少电机振动因素?2023-11-06 1466

-

刚性电路板的9个成本驱动因素2023-10-15 1616

-

电子灯镇流器IGBT门驱动因素2023-07-24 653

-

了解风门执行器以及汽车HVAC系统中它们的驱动因素2022-11-01 838

-

芯片组与芯片组驱动功能的介绍和发展说明2020-12-09 3392

-

阐述芯片组与芯片组驱动功能和发展2020-10-30 2612

-

快速成熟的智能照明市场有哪些驱动因素2018-12-25 1882

-

芯片组是什么_芯片组驱动是什么2018-05-14 21405

-

TDA11135芯片组装机电视图纸2011-10-13 3986

-

威盛 芯片组HyperionPro驱动5.232010-02-01 445

-

柔性电路板上倒装芯片组装技巧2009-11-19 1711

-

电脑主板芯片组的介绍2008-05-29 5808

全部0条评论

快来发表一下你的评论吧 !