高速电路板设计的十条规则

描述

作者:Edwin Robledo, 译者:紫蔬

在Fusion 360中,我们关注于使电子工程师能够轻松设计具有高速信号元器件的电路板。Fusion 360信号完整性扩展程序有助于提高产品合规性和性能,减少实物电路板测试和原型制作的昂贵花费,并加快高速电路板开发进程。

在使用高速信号元器件布置电路板时,需要遵循许多经验法则。让我们看看其中的一些,探索为什么遵循它们是有意义的,并了解什么时候可以不用。

1.尽可能保持您的布线路径短而直

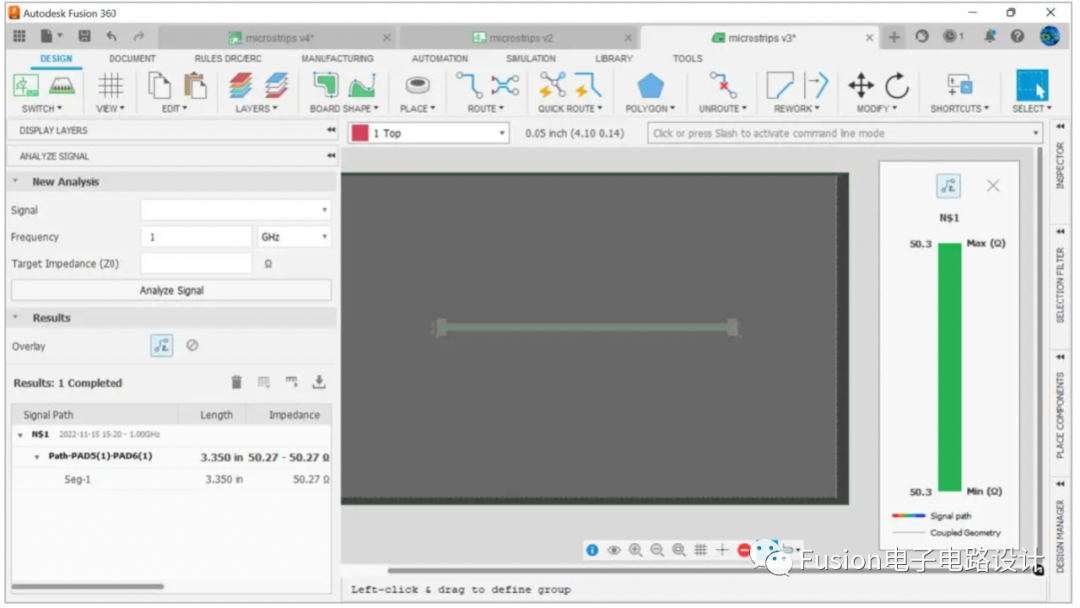

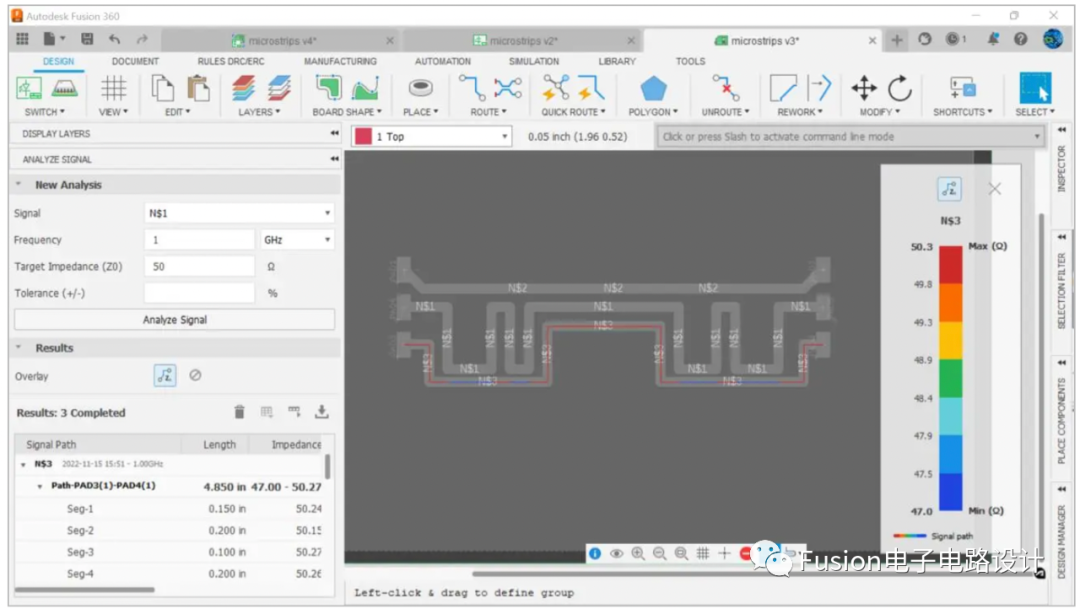

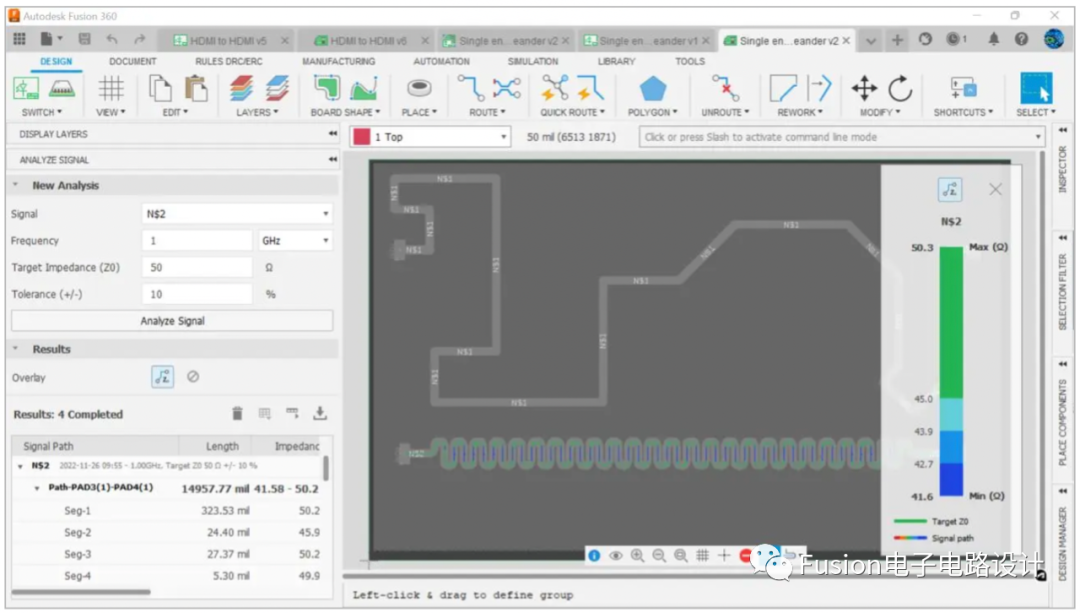

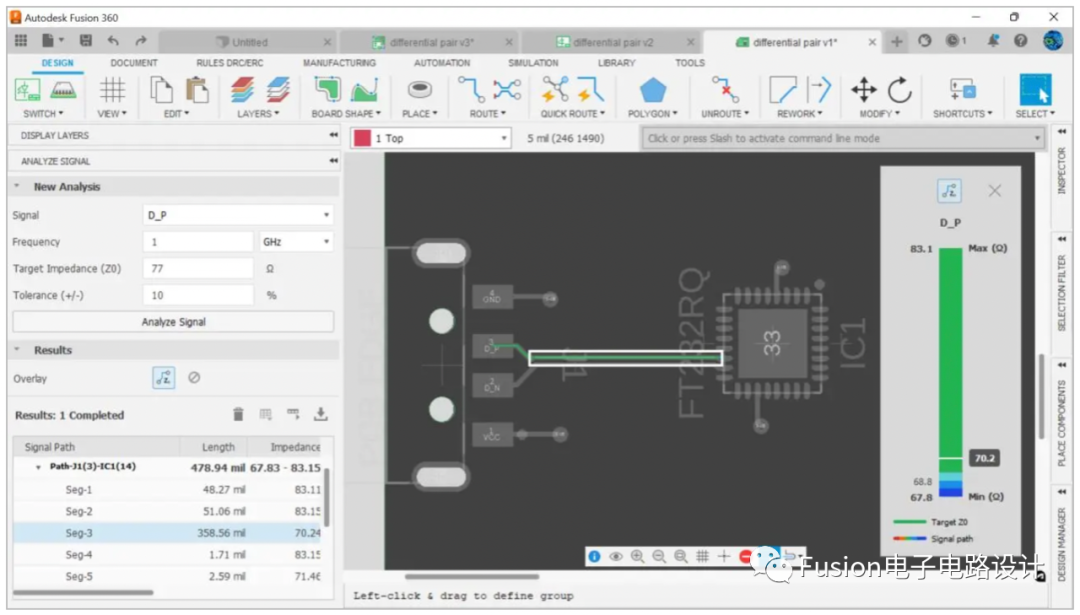

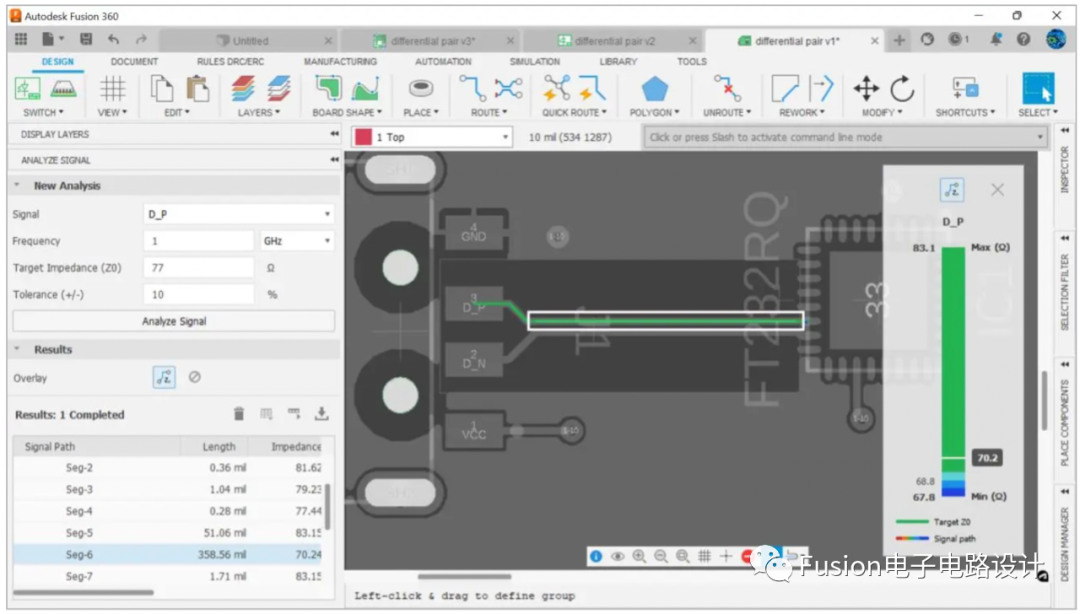

这个经验法则是一个金标准。短直线布线具有最小的时间延迟,并保持一致的阻抗。像Fusion 360 Signal Integrity Extension(信号完整性扩展程序)这样的电路板布局模拟软件可以计算沿着其长度的迹线的阻抗,让您知道不连续性是否存在以及在哪里存在。

使用Fusion 360信号完整性扩展程序,我们可以看到直线布线沿其长度呈现恒定阻抗。

Fusion 360 Electronics的信号完整性扩展程序扩展显示了具有恒定50.3Ω阻抗的布线。

2.不要使用90°角(没关系,你可以使用)

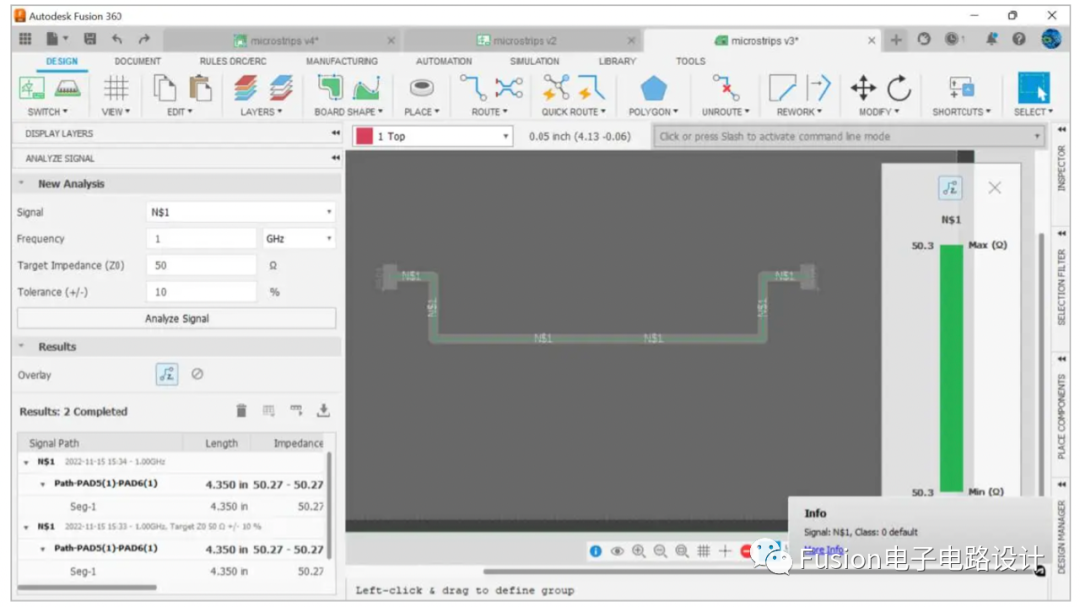

这是一条常见的规则,几乎与被反驳的频率一样频繁。这条规则的共同点是,90°角会导致阻抗不连续,也就是说,当直线轨迹上有90°角时,阻抗会发生变化。除非你在亚毫米波段工作,否则情况并非如此。请注意,使用90°直角布线的该迹线保持恒定阻抗。

90°直角布线不会影响迹线的阻抗。

在高速信号设计中布线时,需要考虑电场重叠的情况,这也是我们在线路下面敷铜的原因。一起看看如果我们把线路来回移动靠近它自己的话,会发生什么吧。

重叠的电场将导致迹线阻抗的变化。

我们看到阻抗现在在变化。是的,虽然变化不是很多,但它仍然在变化,因为电场现在存在重叠的情况。

相邻迹线在确定阻抗方面也起着作用。

相邻布线也会改变线路的阻抗。

请注意,当磁场由于彼此靠近而可能重叠时,会发生阻抗变化。

还要注意,迹线越靠近相邻迹线,阻抗不连续性越大。

迹线越近,阻抗变化越大。

因此,90°角在阻抗不连续性中不起作用。重要的是相邻的电场足够接近而重叠——这将影响阻抗。

那么,有什么理由遵循没有90°直角的规则吗?是的,如果您正在设计高压电路板,任何尖锐的角落都会集中电场,并可能导致发生弧闪(Flashover Arcs)。使用45°角的另一个优点是迹线更短,环路面积更小,从而减少EMI(电磁干扰),信号到达更快。

说到信号到达,让我们来看看长度匹配的重要性。

3.长度匹配高速信号,避免信号到达时间不匹配

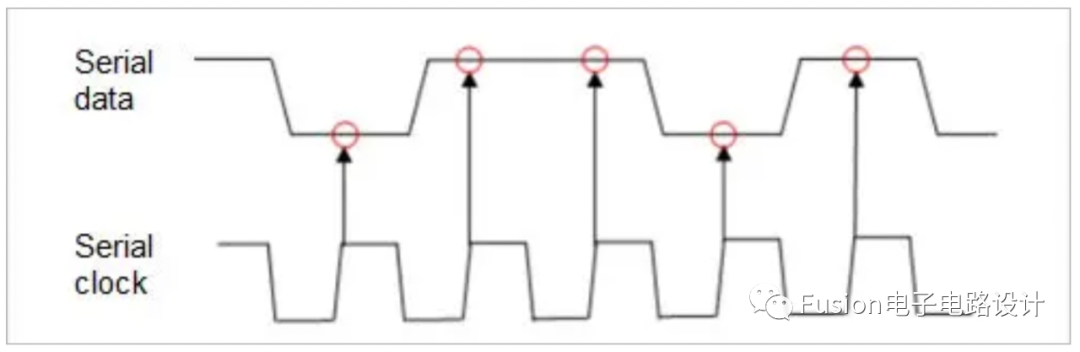

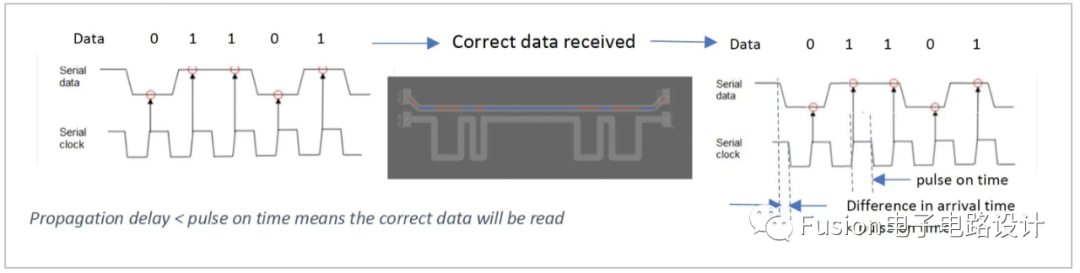

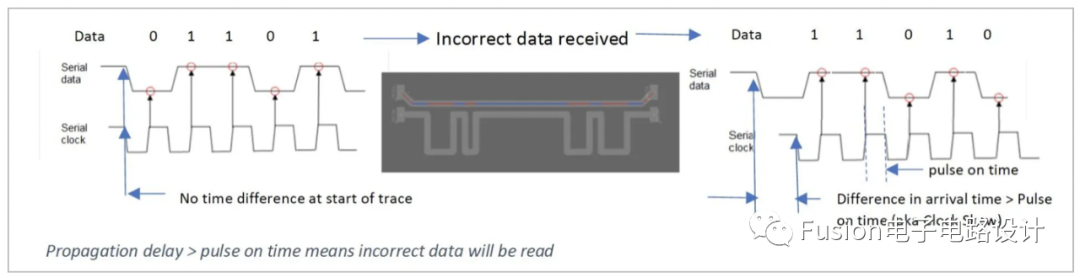

当布线高速信号时,重要的是跟踪长度匹配,因为长度不匹配意味着信号到达时间不匹配。考虑一个高速时钟信号及其相关数据。

来源: Difference Between Serial Communication Function With and Without Clock | Renesas Customer Hub.

https://en-support.renesas.com/knowledgeBase/17943143

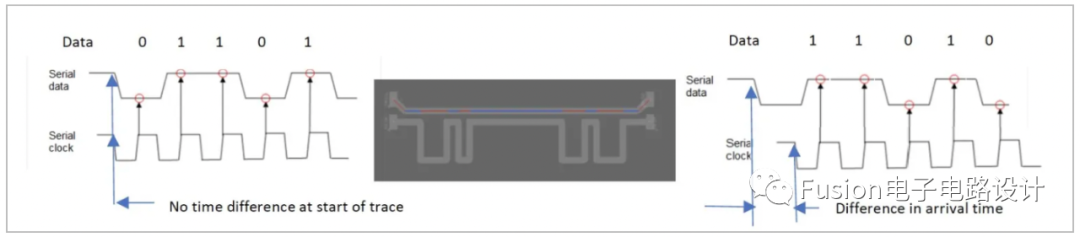

该时钟的上升沿确定要读取的数据是零还是一。对于高速信号,信号沿轨迹传播所需的时间(称为传播延迟)可以在信号是否被正确读取方面发挥作用。检查下面的情况,底部时钟迹线比顶部数据迹线长。

不相等迹线长度导致的脉冲到达时间有所差异(也称为传播延迟或时间延迟)。

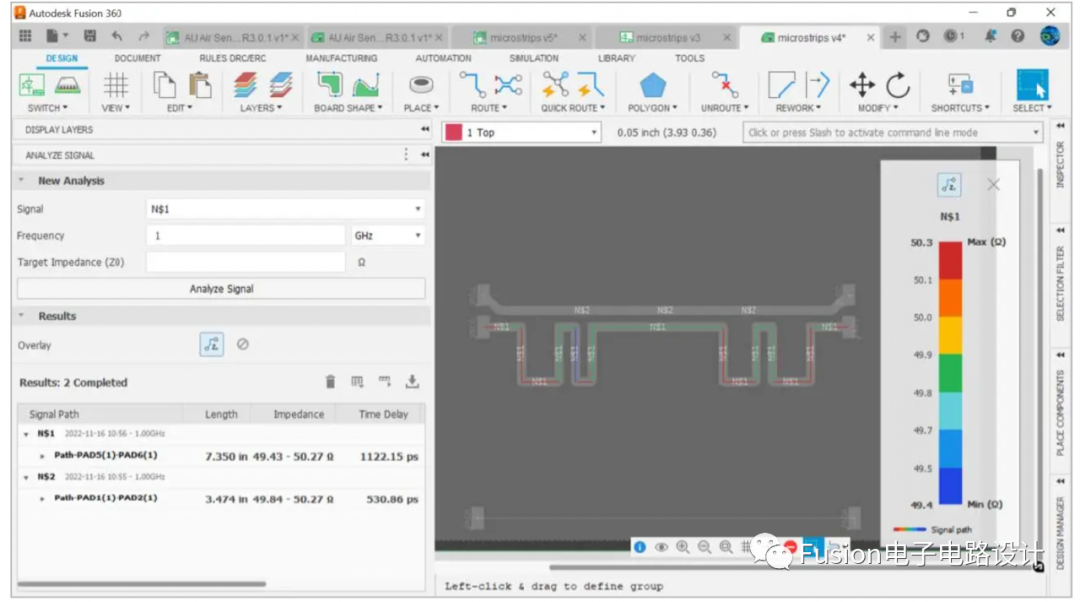

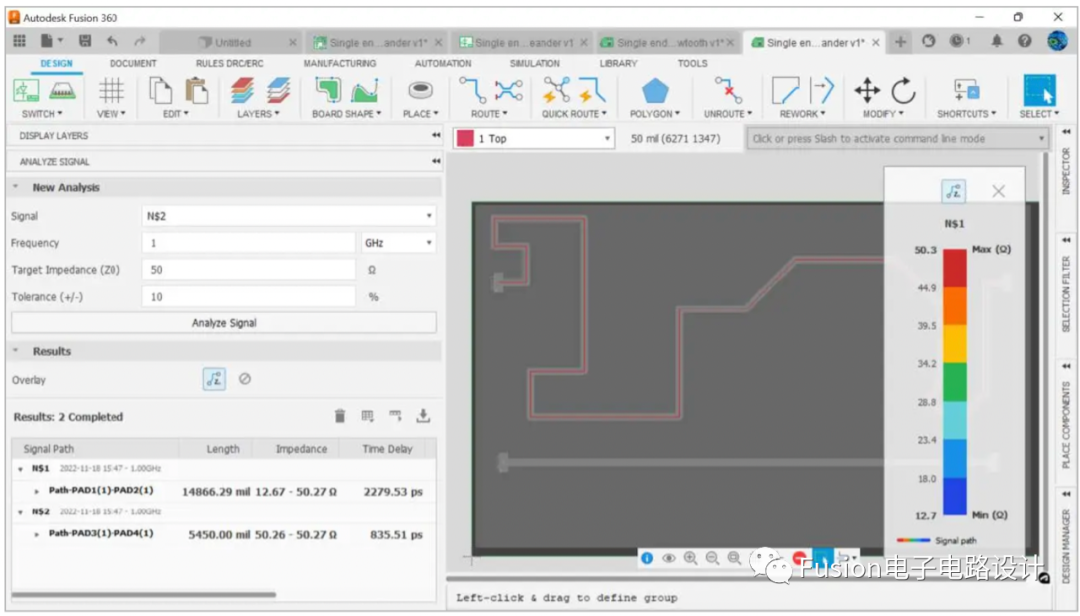

在这种情况下,时钟信号比串行数据信号延迟得多,接收器不能读取到01101,而是将错误地“看到”11010。所以高速信号的长度匹配很重要。Fusion 360中的信号完整性扩展程序计算了迹线中的传播延迟,从而可以很容易地看出信号的定时是否会出现问题。

Fusion 360 Electronics的信号完整性扩展程序将为您计算迹线传播延迟。

这里我们可以看到,两条迹线之间的传播时间差为591.29ps。如果我们的时钟频率脉冲开启时间开始接近两条迹线之间的传播速度差,我们将在数据读取中出现错误。

考虑传播时间差小于脉冲接通时间的情况。

我们可以在上面看到发送的数据 = 接收的数据。

然而,到达时间差越接近脉冲接通时间,就越可能发生错误。

数据和时钟之间的时间差称为时钟偏差。这就引出了我们的下一条经验法则。

4.保持时钟偏差小于时钟周期的1/10

我们可以从上面的示例中看到,这个经验法则使时钟边缘远离数据转换区。如果我们的时钟和数据信号的差异大于时钟周期的1/10,我们需要延长更快的信号。

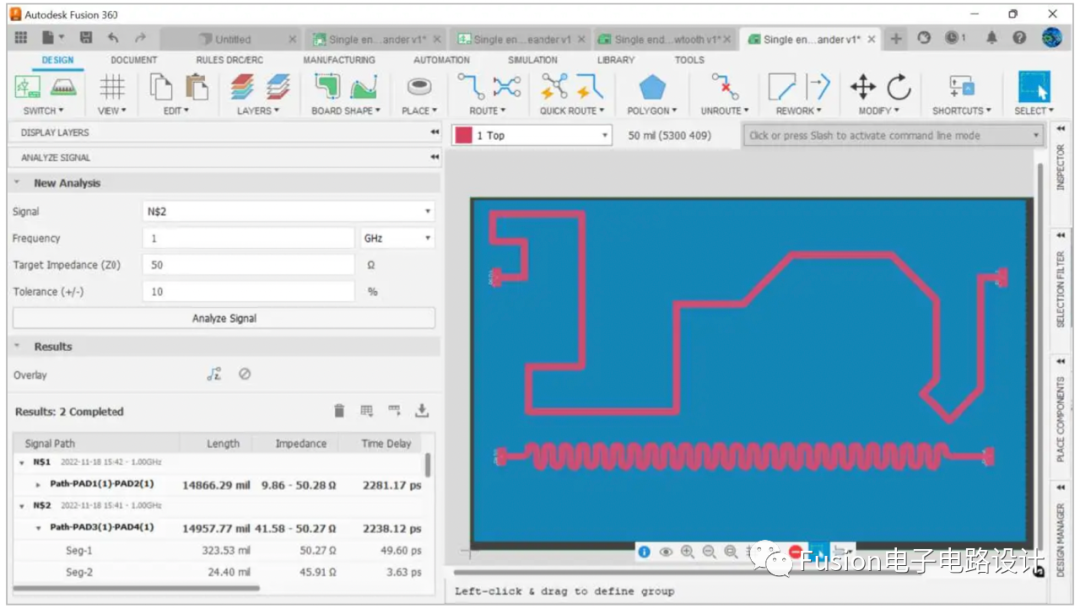

5.延长迹线以均衡定时延迟

有几种方法可以延长迹线,以便将时间差异纳入规范中。如果长度不匹配很小,可以通过重新布线迹线使其稍长来延长。Fusion 360 Electronics中的信号完整性扩展程序工具将显示迹线的传播延迟,您可以决定是否需要调整长度或使用折弯迹线命令延长长度。

6.折弯线路时遵循4X规则

折弯意味着来回移动迹线以延长它。考虑所示的电路板,注意底部迹线比顶部迹线短得多,而且速度明显快。

顶部迹线大约是底部迹线的两倍长。

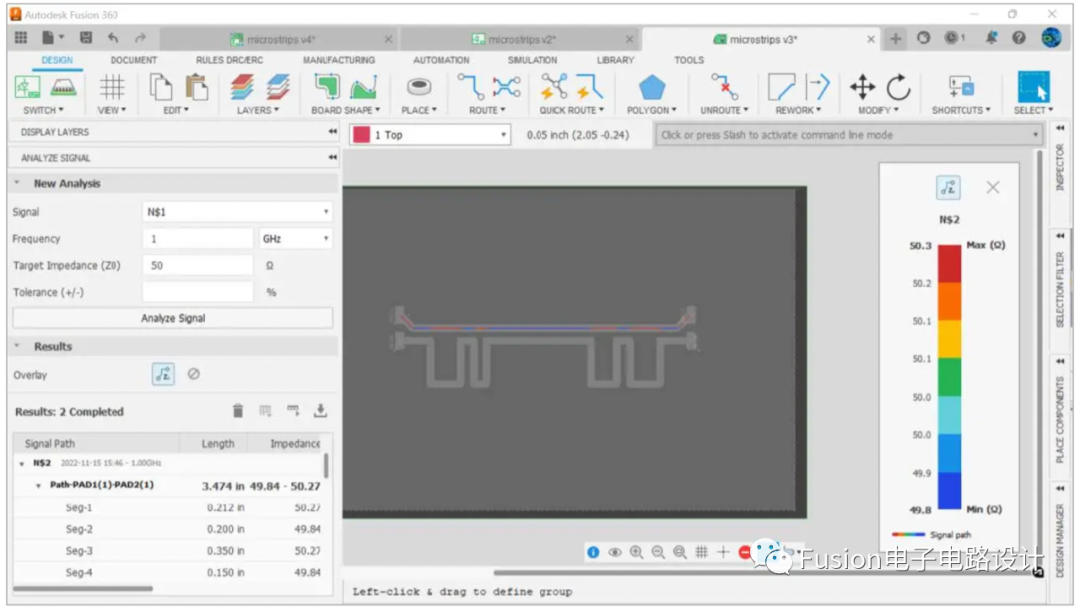

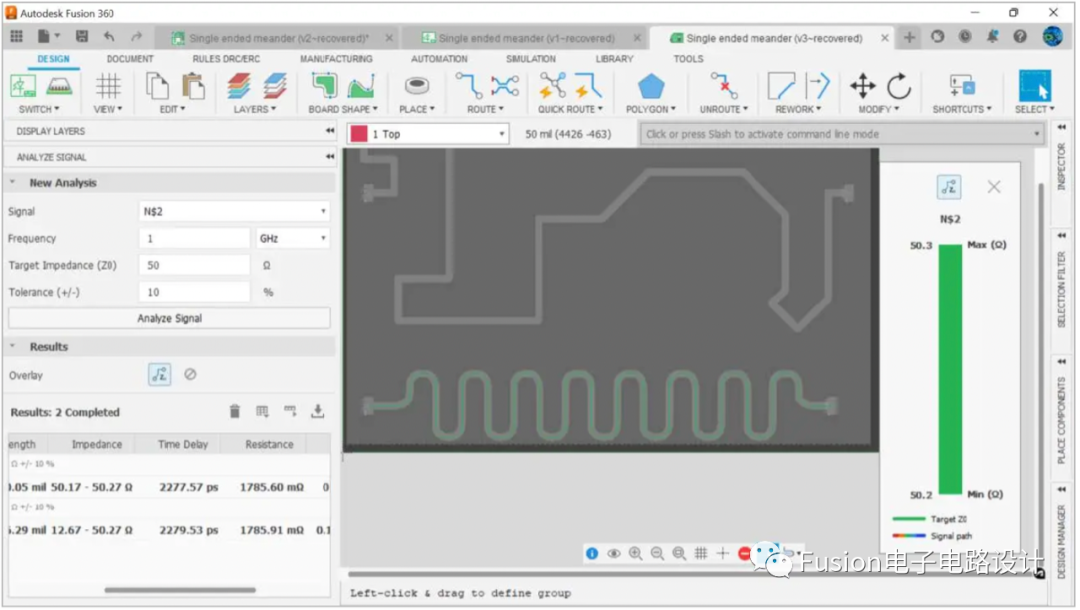

折弯底部迹线会导致更长的长度和传播延迟,这可能在规范范围内。Fusion 360 Electronics允许您在单端信号和差分信号之间进行迂回。

底部迹线加长以匹配顶部迹线的长度。

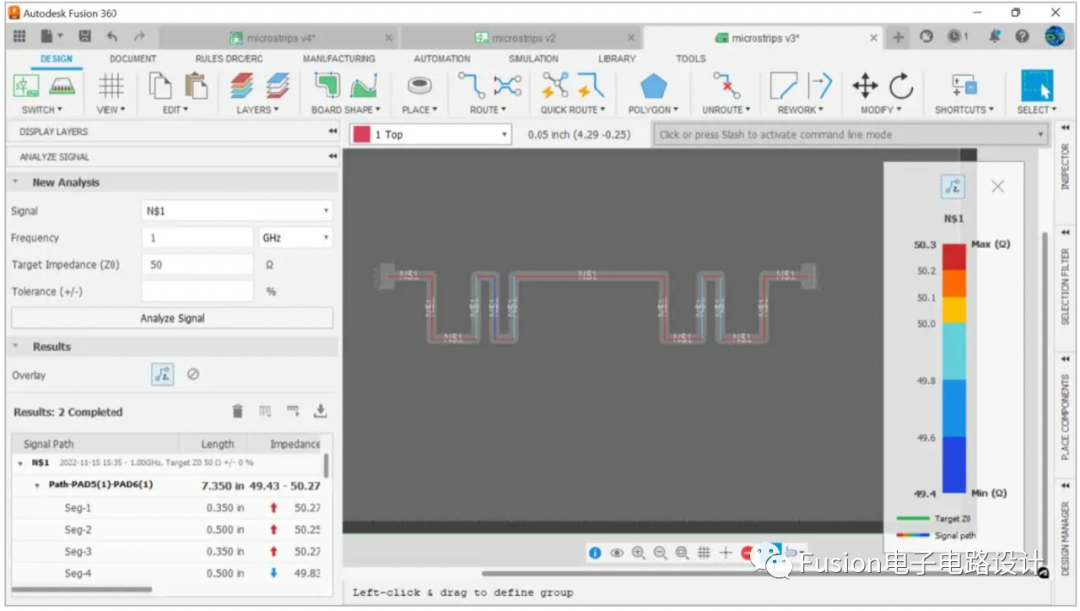

当折弯时,电路板设计者通常遵循4X规则:将折弯之间的距离保持为迹线宽度的4X(4倍),因为这将最小化阻抗不连续性。让我们看看这个例子中的迹线阻抗。

底部迹线由于间距小而紧密耦合。

相邻迹线之间存在许多不连续性,这是电场相互重叠导致的。看看当我们将间距设为迹线宽度的4倍时会发生什么。阻抗现在变得一致啦!

阻抗现在一致啦。

差分布线也可能需要延长,但让我们等到稍后讨论差分信号时再说吧。

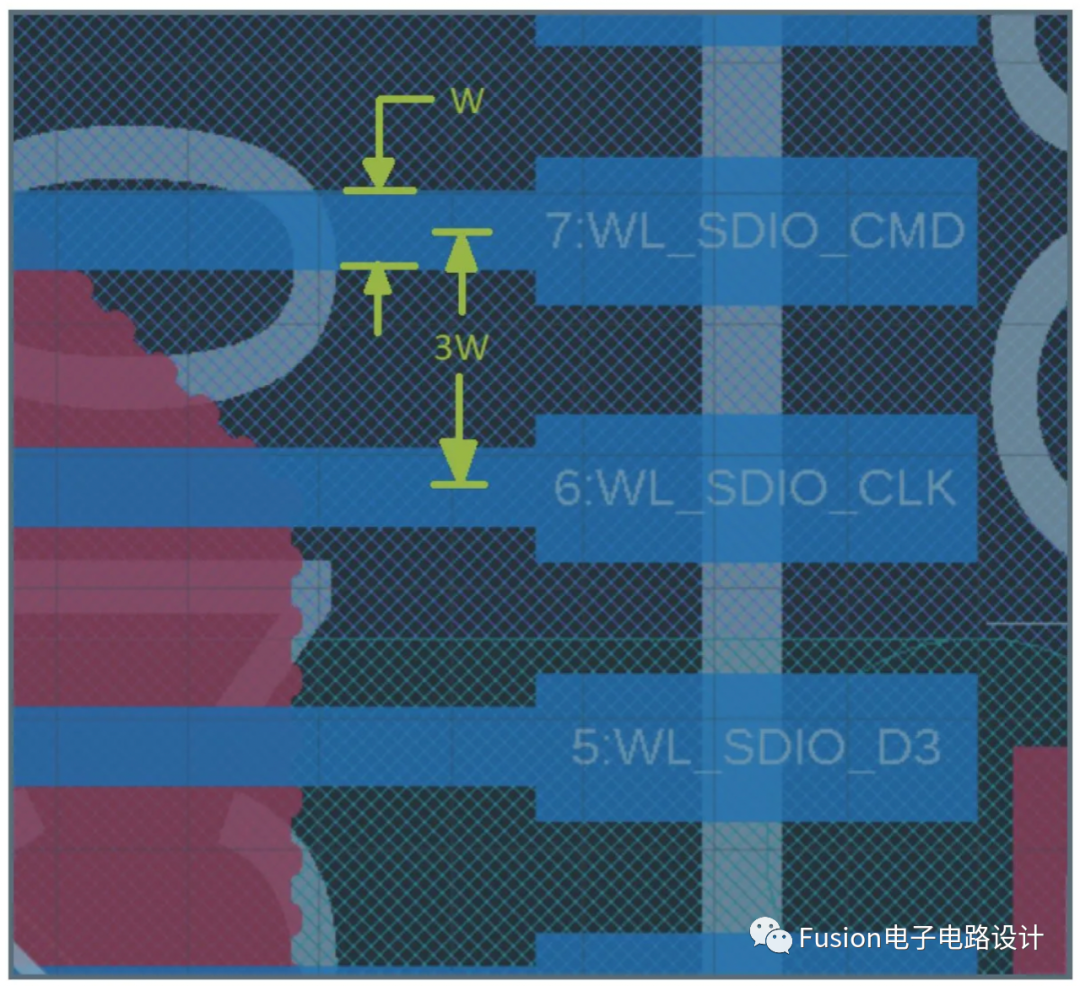

7.遵循3W规则以最小化串扰

在早期的电话时代,如果承载通话的电缆中的电线并排,您可以听到邻居的谈话。这种现象称为“串扰”。

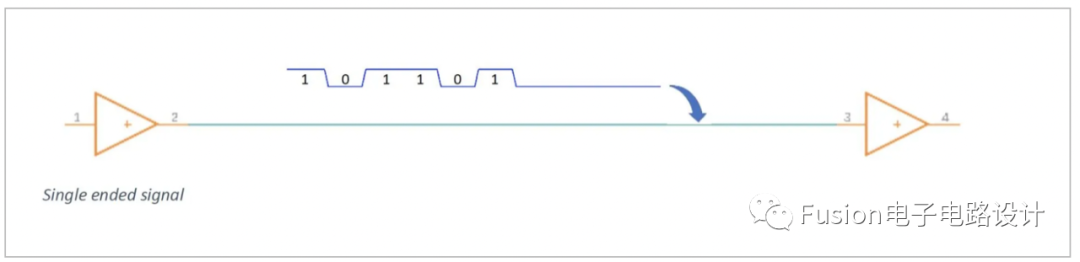

考虑传统的单端数字信号。数据由代表1和0的高电压和低电压组成。

单端信号。

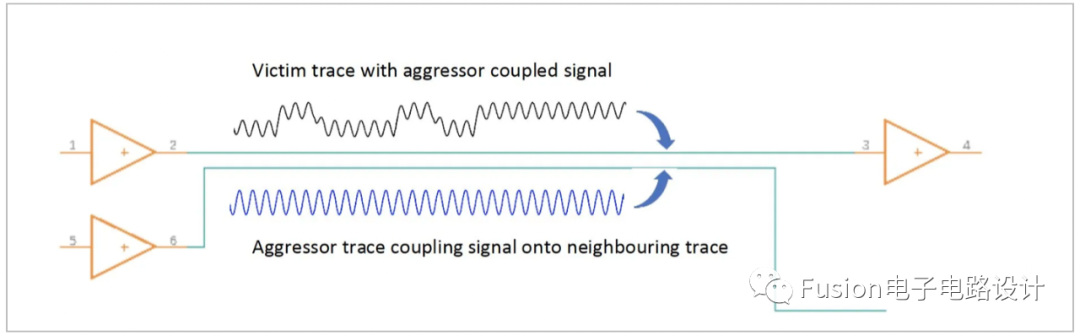

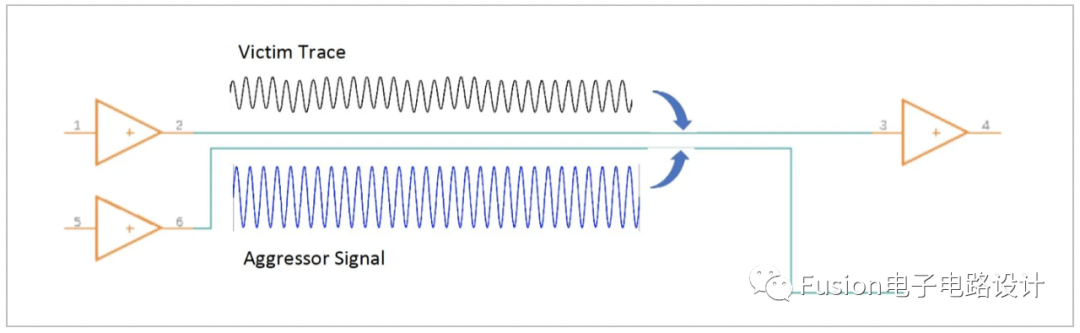

然而,附近的线路会将不需要的噪声耦合到信号上。

如果来自“侵略信号”的耦合噪声(不需要的信号)足够大,则“受害信号”(需要的信号)可能被严重地混淆。

串扰的3W规则规定,平行迹线之间的距离应至少为3W,从迹线的中心到中心进行测量,以最小化它们之间的耦合,其中W=迹线的宽度。当然,更多的空间是更好的,特别是当频率增加到GHz区域或长度过长时。还要注意的是,3W规则假设相邻层上有敷铜,因为这将电场限制在迹线两侧较小的距离。

可以将两条相邻的迹线视为电容耦合的两条迹线。电容器只是由绝缘体隔开的两个极板,正好是两个相邻的迹线,绝缘体是它们之间的空气。与电容器一样,极板之间的距离越大,电容越小。电容越低,耦合信号越小。类似地,电路板越长,电容越大,耦合信号越大。所以,在高速设计中,尽量保持迹线短而远。

8.遵循差分时钟的8W间隔(或探索其他规则)

高速差分信号需要更大的间隔。此规则可保持所需的信号阻抗。此8W规则也适用于同一层上的敷铜。考虑以下USB差分信号:

70.2Ω阻抗的迹线。

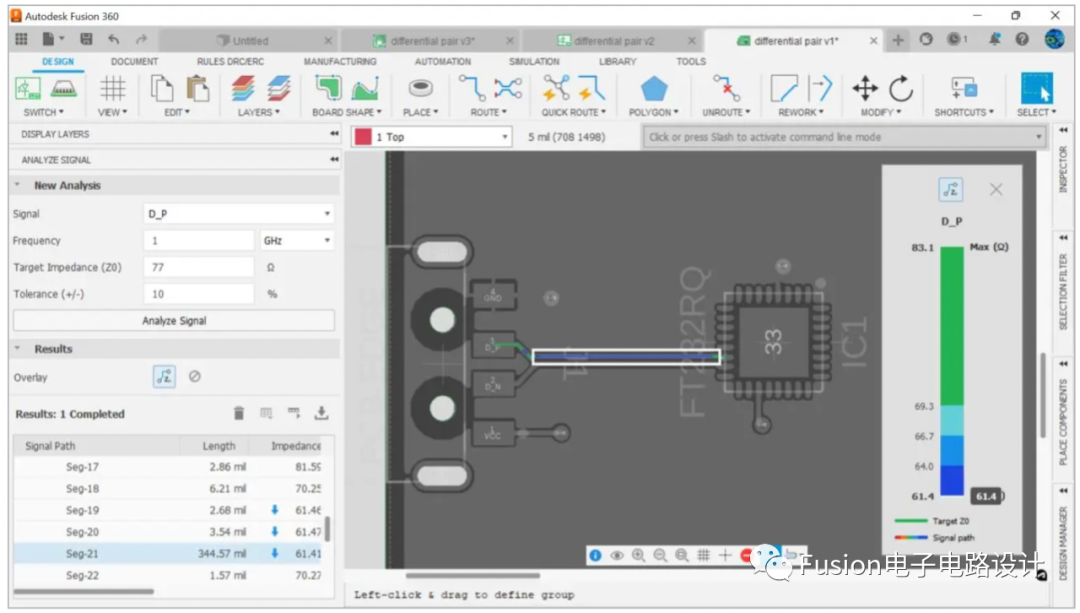

上图示例里,大多数迹线的阻抗为70.2Ω。看看如果我们在靠近信号的顶层放置接地敷铜,阻抗会发生什么变化。线路阻抗几乎全部为61Ω。

阻抗随顶部接地敷铜显著变化。

但是,按照我们的8W规则,放入80mil 间距,我们得到了之前的阻抗70.2Ω。

将接地敷铜与迹线隔开,使阻抗回到70.2Ω。

8W规则是保守的数字,有些使用5W甚至3H,其中H = 接地层和信号层之间的电介质高度。通过信号完整性扩展程序,Fusion 360 Electronics可以向您显示计算的阻抗值,并帮助您确定拥挤信号线路之间的影响。

9.差分布线的长度不匹配没有经验法则

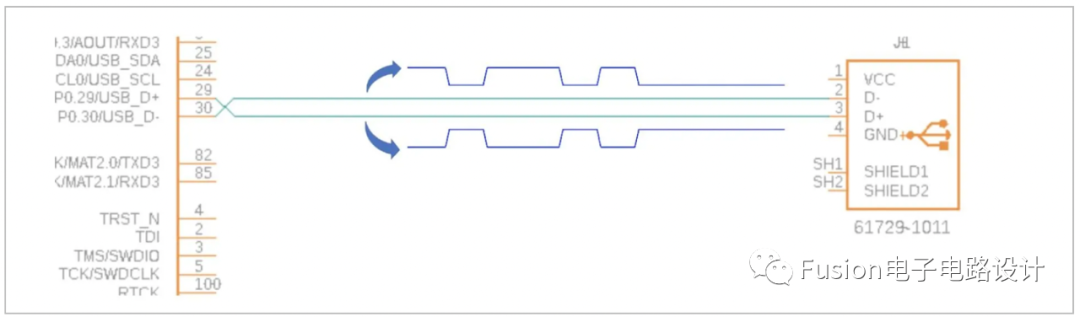

到目前为止,我们已经多次提到差分信号,因此让我们更详细地了解它们。

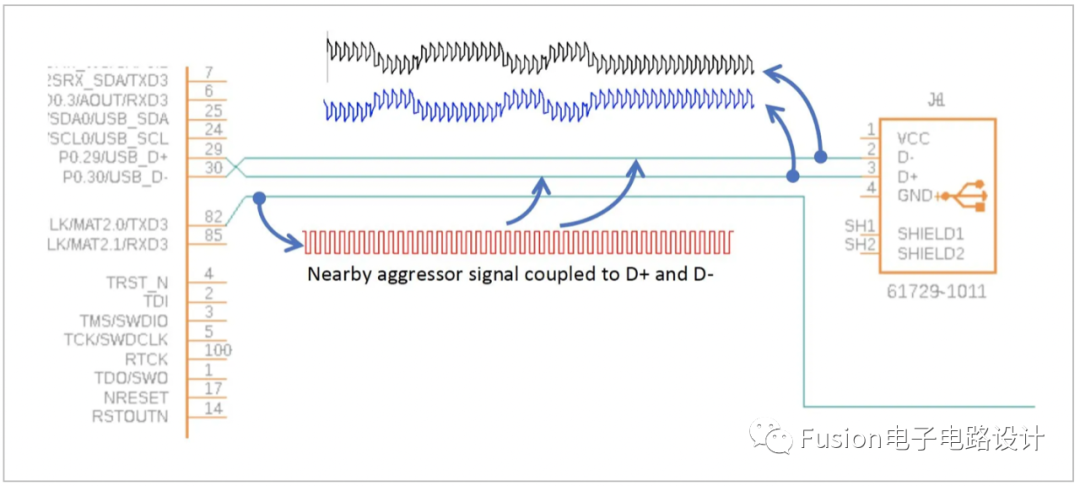

差分信号在HDMI、USB、LVDS等高速通信标准中非常常见。这是因为它们抗噪音。让我们看看他们为什么能拒绝噪音。

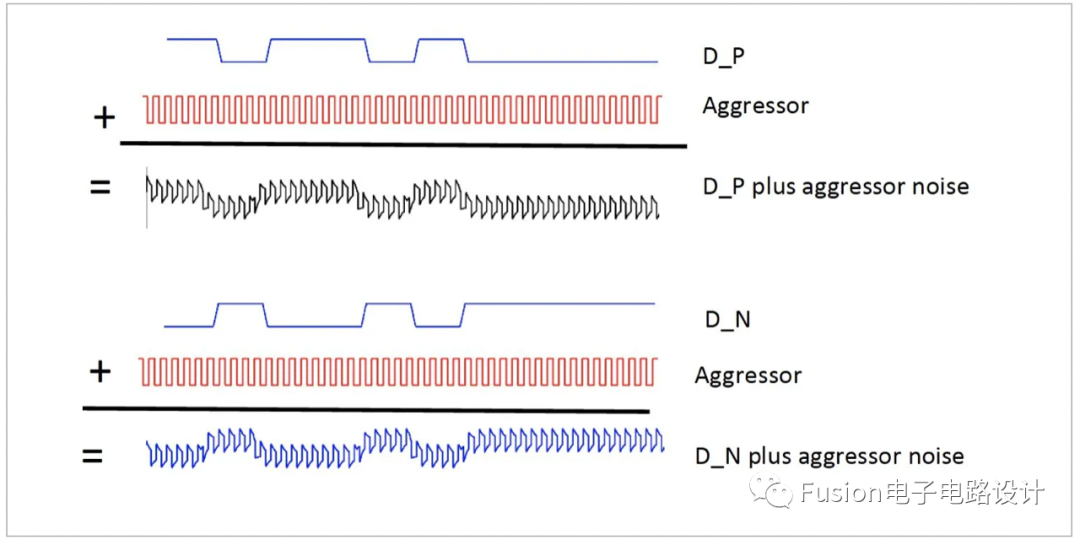

差分信号由两个信号D+(D_P)和D-(D_N)组成。这对电线上的信号极性相反。

差分信号极性相反。

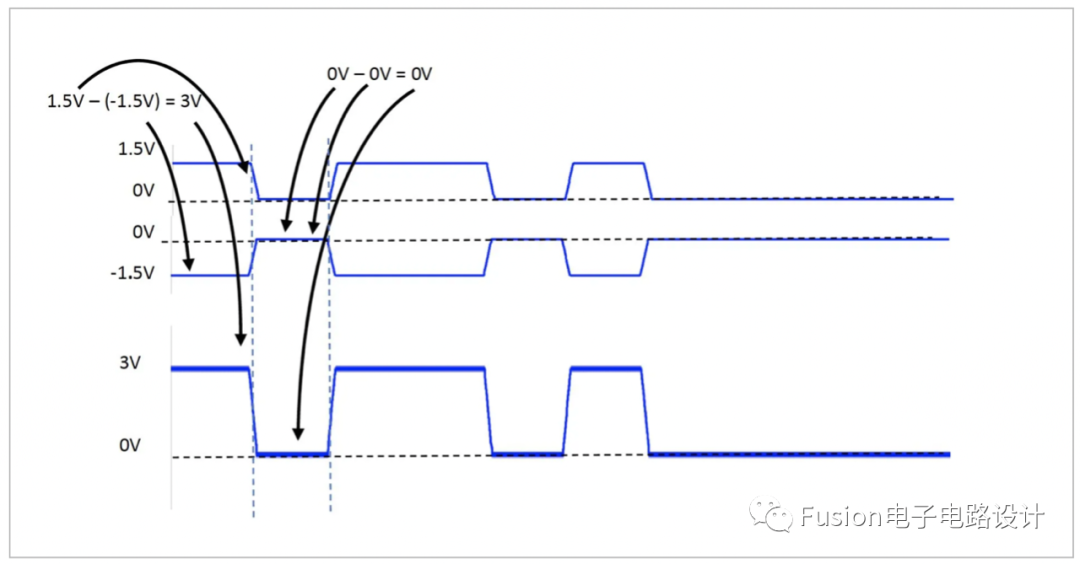

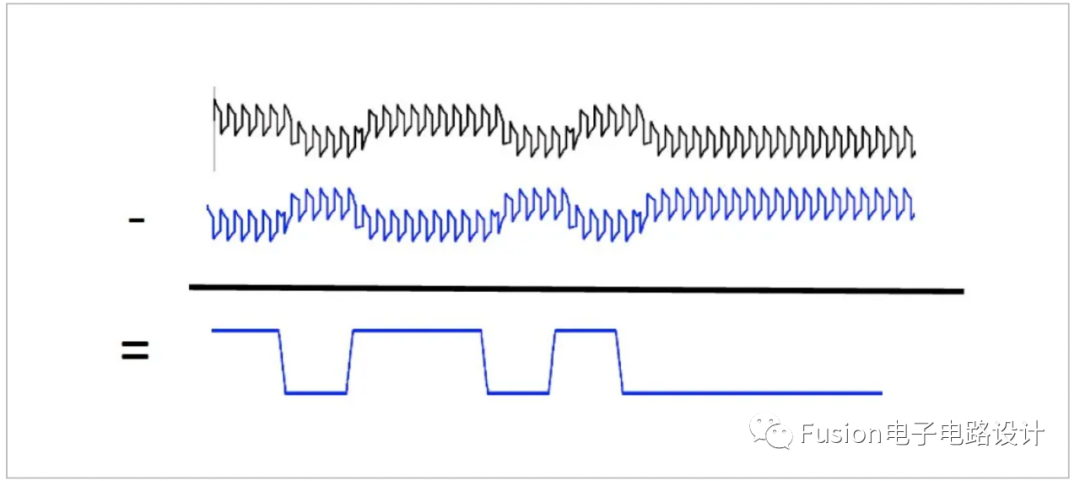

差分信号的接收端从正信号中减去负信号,得到恢复信号。

正如我们前面所说的,差分信号的真正优点是它们可以抑制噪声。考虑附近具有不希望的干扰信号的差分信号,该干扰信号将信号耦合到每个差分线。

产生的耦合信号将以相同的极性出现在差分布线的每条迹线上。即:

在接收机处,两个噪声信号彼此相减,我们得到两个没有任何干扰噪声的差分信号。即,

(D_P+Aggressor)–(D_N+Aggressor)=D_P – D_N

而且,从前面我们知道D_P – D_N = 两倍大的单个信号。从图形上看,它意味着:

两种信号的共同噪声消失了。

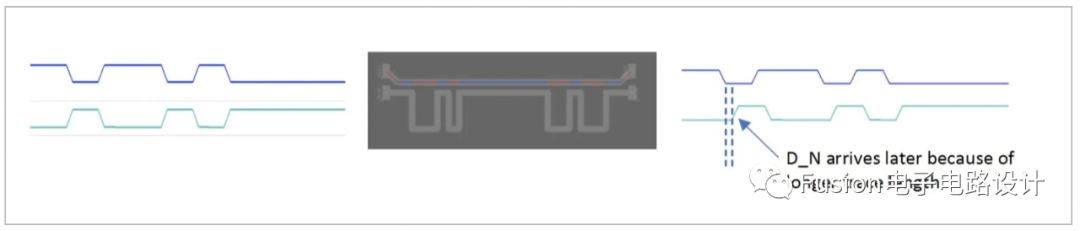

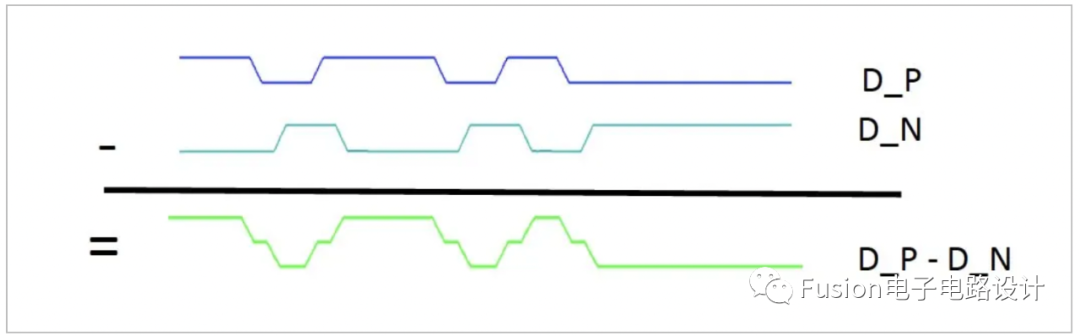

差分信号也对信号对之间的定时差敏感。考虑以下情况,其中一对信号中的一个信号必须传播更长的距离,因此到达时间较晚。

从D_P减去D_N后的结果如下:

也许接收机能正确解码D_P–D_N,也许不能。这就引出了我们的下一条经验法则:差分布线的长度不匹配没有经验法则。

高速信号规格将确定差分布线的长度最大的不匹配值。遵守技术规格说明,不然任何其他情况都可能导致不必要的EMI或EMC问题。

10.了解对内和对间延时差 (Understand intra pair and inter pair skew)

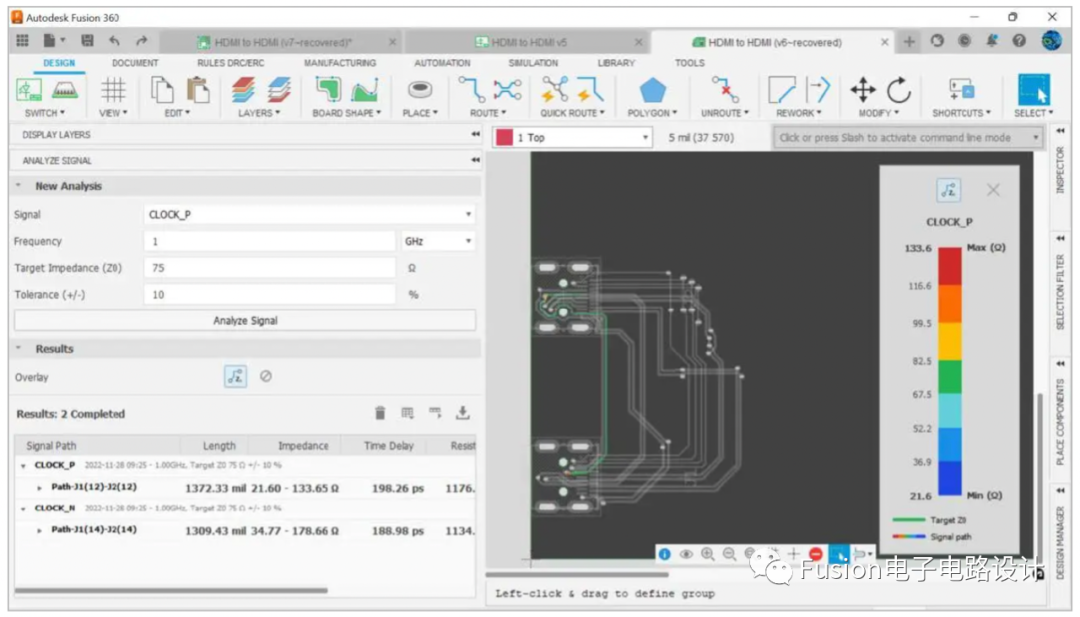

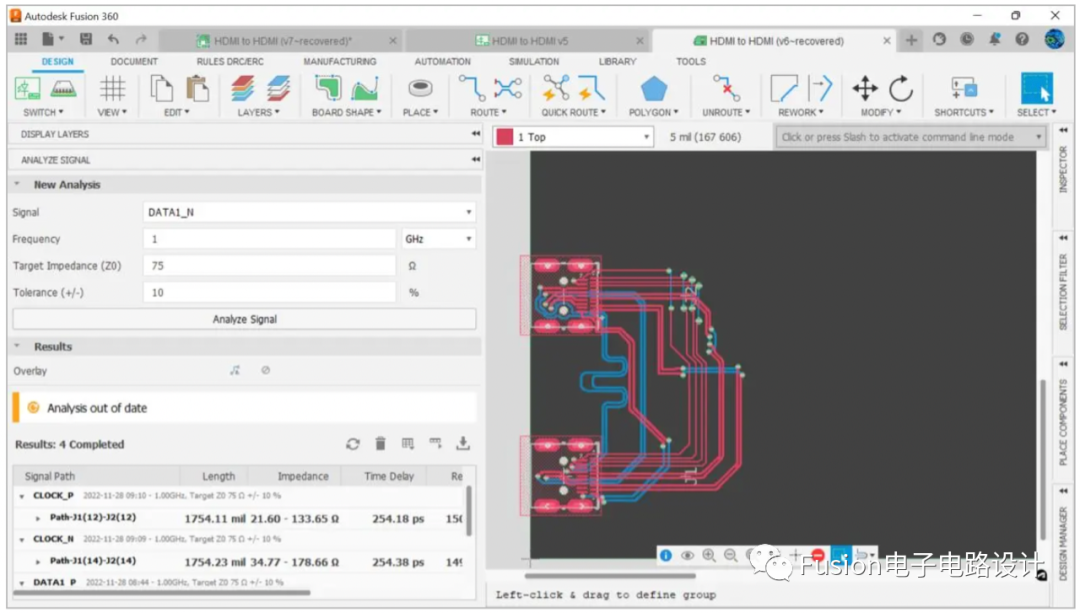

对内延时差(Intra-pair skew)是单个差分对的布线路径之间的时间差。如上所示,不同的时差会干扰信号,使其变得不可用。解决方案是延长较短的差分对。

差分对之间的不同长度。

“meander 1800 mil”命令会让时钟线延长到1800 mil(数据线的长度)。

折弯命令用于延长差分对的线路长。

请注意,折弯还调整了时钟差分对的长度,以最小化对间偏移。

Fusion 360信号完整性扩展程序使电路板设计者能够模拟迹线的阻抗和传播延迟。可以看到间距、迹线宽度、信号拥挤和层堆叠对阻抗控制线路的影响。经验法则可以得到验证,所提供的见解可以用来确定是否需要遵循经验法则。通过Fusion 360信号完整性扩展程序,设计人员可以修改和调整迹线长度和路径,提高电路板的信号完整性和设计质量。

准备好开始高速电路板设计了吗?立即免费14天试用Fusion 360信号完整性扩展程序吧。

审核编辑:汤梓红

-

**十条PCB元器件摆放小建议**2024-03-14 4984

-

元器件布局的10条规则2022-02-12 9431

-

十条PCB元器件摆放小建议2021-01-26 4545

-

闸流管和双向可控硅成功应用的规则有哪些十条黄金规则详细说明2019-10-11 1764

-

闸流管和双向可控硅成功应用的十条黄金规则详细说明2019-09-29 1743

-

准确测量示波器噪声的七条规则2018-11-01 2823

-

降低RF-PCB电路布局寄生信号的8条规则2018-09-10 5038

-

PCB设计中元器件布局的10条规则,布线的规则是什么?2018-07-17 17529

-

十条最有效的PCB设计黄金法则2017-08-17 3217

-

88条规则敲定:PCB电路板测试、检验及规范2016-12-26 5135

-

闸流管和双向可控硅 - 成功应用的十条黄金规则2013-09-13 1838

-

PLD、FPGA优秀设计的十条戒律2012-01-17 530

-

可控硅使用十条黄金定律2010-03-03 1363

-

闸流管和双向可控硅-成功应用的十条黄金规则2009-02-10 8391

全部0条评论

快来发表一下你的评论吧 !