半导体工艺中的蚀刻工艺的选择性

制造/封装

描述

刻蚀技术(etching technique),是在半导体工艺,按照掩模图形或设计要求对半导体衬底表面或表面覆盖薄膜进行选择性腐蚀或剥离的技术。刻蚀技术不仅是半导体器件和集成电路的基本制造工艺,而且还应用于薄膜电路、印刷电路和其他微细图形的加工。刻蚀还可分为湿法刻蚀和干法刻蚀。

刻蚀的机制,按发生顺序可概分为「反应物接近表面」、「表面氧化」、「表面反应」、「生成物离开表面」等过程。所以整个刻蚀,包含反应物接近、生成物离开的扩散效应,以及化学反应两部分。整个刻蚀的时间,等于是扩散与化学反应两部分所费时间的总和。二者之中孰者费时较长,整个刻蚀之快慢也卡在该者,故有所谓「reaction limited」与「diffusion limited」两类刻蚀之分。

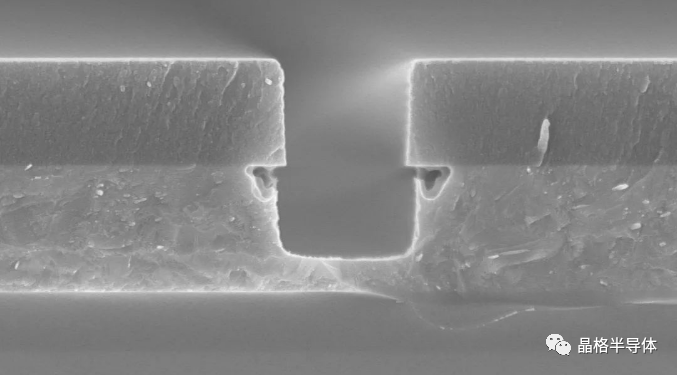

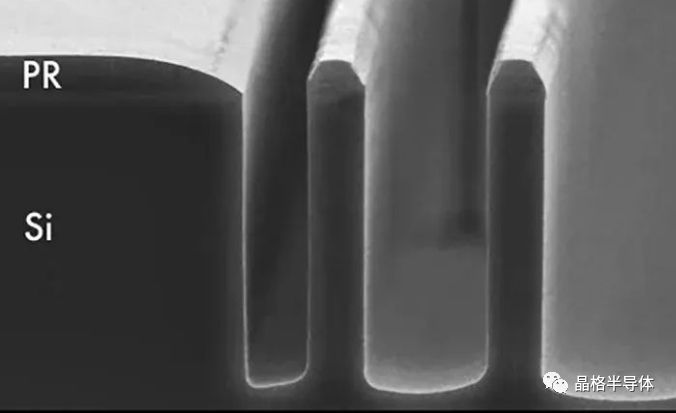

目前干法刻蚀市场占比90%,湿法刻蚀占比10%,湿法刻蚀一般适用于尺寸较大的情况下(大于3微米)以及用来腐蚀硅片上某些层或用来去除干法刻蚀后的残留物。其余,生产中大部分采用干法刻蚀。 干法刻蚀与湿法腐蚀工艺利用药液处理的原理不同,干法刻蚀在刻蚀表面材料时,既存在化学反应又存在物理反应。因此在刻蚀特性上既表现出化学的等方性,又表现出物理的异方性。所谓等方性,是指纵横两个方向上均存在刻蚀。而异向性,则指单一纵向上的刻蚀。干法刻蚀用于高精度的图形转移。目前我国刻蚀工艺以及刻蚀设备相对于光刻而言,已经能够达到世界较为前列的水平。能够达到较高的刻蚀选择性、更好的尺寸控制、低面比例依赖刻蚀和更低的等离子体损伤。

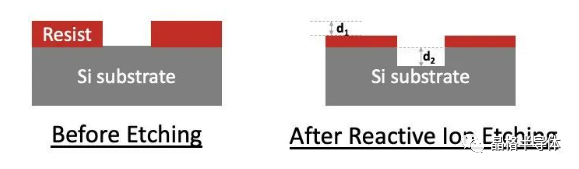

蚀刻的选择性 刻蚀选择性(Etch Selectivity)是描述在刻蚀过程中,所需材料与不应被刻蚀的材料之间刻蚀速率的比值。刻蚀选择性可以用来描述掩膜和目标材料的蚀刻速率之间的相对蚀刻速率,也可以是不同材料层之间的相对蚀刻速率。如果一个目标材料被刻蚀的速度是掩膜或基底材料的10倍,那么刻蚀选择比就是10:1。

刻蚀选择性越高,表示目标材料被刻蚀的速率很快,但是掩膜或相邻层刻蚀的速率很慢。高的刻蚀选择性确保掩膜在刻蚀过程中几乎不被消耗,并且在刻蚀完目标材料后反应停止,不会再刻蚀相邻层。一般来说,>5:1 的选择性被认为是高选择性。在某些情况下,选择性可能为 100:1。 刻蚀选择性越低,两种材料以相对相似的速率蚀刻。当选择性较低时,掩膜将无法为目标材料提供尽可能多的保护。这意味着必须使用更厚的掩膜来刻蚀到所需的深度,这样就提高了掩膜制作的难度和成本。另一方面,当目标材料被刻蚀完后,仍然会对底层材料进行刻蚀,这些都是我们所不想要的。

干法刻蚀过程中的注意事项

维持一致性(Uniformity)。一致性是指刻 蚀的速度在晶圆上的各个部位“有多相同”在 工艺进行的过程中,一定时间下,不同的晶圆部位刻蚀的速度不同,形成的形状也可能不同,所以可能会导致位于某些部位的芯片发生不良现象或其特性发生变化。

刻蚀速度(Etch Rate)。它意味着在一定时间内可以去除多少薄膜。刻蚀速度主要取决于表面反应所必需的反应性原子和离子的数量以及离子的能量,所以提高对这些因素的控制能力就可以提高总收益率。此外,选择性(Selectivity)、形状(Profile)等也是干式刻蚀的重要因素。

审核编辑:黄飞

-

使用n型GaSb衬底优化干法和湿法蚀刻工艺2022-05-11 1953

-

半导体器件制造中的蚀刻工艺技术概述2022-07-06 4905

-

湿法蚀刻工艺的原理2022-07-27 4116

-

PCB线路板外层电路的蚀刻工艺详解2018-09-13 3196

-

详谈PCB的蚀刻工艺2018-09-19 3866

-

PCB外层电路的蚀刻工艺2018-11-26 4274

-

PCB蚀刻工艺质量要求2020-03-03 4742

-

湿法蚀刻工艺2021-01-08 4875

-

《炬丰科技-半导体工艺》CMOS 单元工艺2021-07-06 2985

-

《炬丰科技-半导体工艺》GaN的晶体湿化学蚀刻2021-07-07 2444

-

《炬丰科技-半导体工艺》GaN 纳米线制造和单光子发射器器件应用的蚀刻工艺2021-07-08 4300

-

《炬丰科技-半导体工艺》InGaP 和 GaAs 在 HCl 中的湿蚀刻2021-07-09 4148

-

PCB蚀刻工艺原理_pcb蚀刻工艺流程详解2018-05-07 49076

-

芯片湿法蚀刻工艺2024-12-27 2027

-

什么是高选择性蚀刻2025-03-12 1185

全部0条评论

快来发表一下你的评论吧 !