基于深氮化镓蚀刻的微米尺寸光子器件的研制

电子说

描述

引言

GaN和相关合金由于其优异的特性以及大的带隙、高的击穿电场和高的电子饱和速度而成为有吸引力的材料之一,与优化工艺过程相关的成熟材料是有源/无源射频光电子器件近期发展的关键问题。专用于三元结构的干法蚀刻工艺特别重要,因为这种器件通常包括异质结构。因此,GaN基光电器件的制造部分或全部依赖于干法刻蚀。

典型地,蚀刻工艺应该产生高蚀刻速率、较小的表面粗糙化、良好的再现性和高度的各向异性。所有这些特性都可以用电感耦合等离子体(ICP)蚀刻来实现。侧壁和蚀刻表面形态是形成具有高纵横比的台面或垂直器件的关键参数。在光子器件的实际环境中,GaN蚀刻的要求固定在几百纳米的数量级,而这与垂直功率器件的预期完全不同,GaN的深度蚀刻目前需要用于新的应用。

实验与讨论

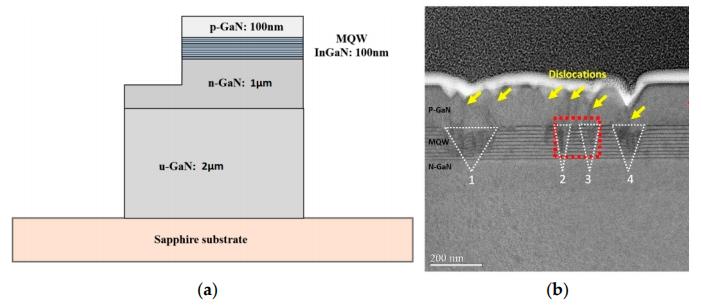

在我们的研究中,III族氮化物层通过使用金属有机化学气相沉积系统(MOCVD)在c面蓝宝石衬底上生长。外延层结构由2μm厚的未掺杂GaN、1μm厚的n-GaN、10个周期的10nm厚的GaN/3nm厚的InGaN MQW和100nm厚的p-GaN组成(如图1所示)。我们通过高角度环形暗场扫描透射电子显微镜研究样品的横截面和平面图。通过聚焦离子束(FIB)在薄箔上沿(1100)和(1120)轴倾斜制备样品,以便观察位错、化学分析和堆垛层错。

图1

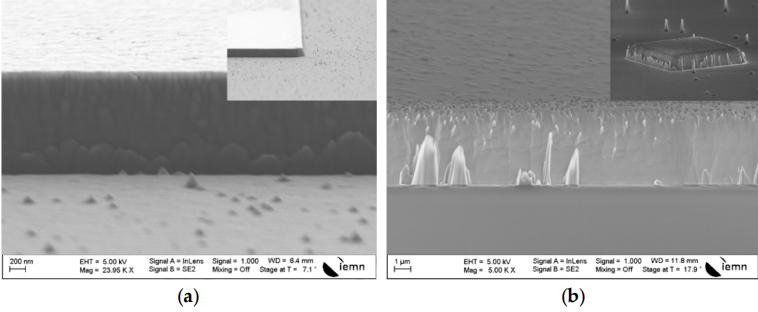

图2

我们应用Cl2/Ar等离子体蚀刻模板的一部分,即100纳米厚的p-GaN层。在GaN的氯化过程中,氯优先与镓物种(Ga)表面原子反应,形成Ga氯化物。对于InGaN/GaN MQW层状结构的蚀刻,铟物种(In)参与化学反应并有助于在表面上形成氯化铟,在工艺温度下不挥发。

为了分析二氧化硅掩模的较大耐久性和韧性,我们应用了深蚀刻工艺(图2),对于大于20×20m2的台面尺寸,蚀刻台面的质量是令人满意的,但是对于小于该尺寸的台面,获得的质量有限。通过观察台面的边缘的损坏区域,我们发现SiO2蚀刻掩模的限制。在该蚀刻轮廓范围内,使用SiO2盖板也出现柱状缺陷的形成。柱状缺陷通常是由于微掩蔽效应引起的,它们源于硬掩模材料的溅射,硬掩模材料在蚀刻表面上沉积颗粒,并产生局部微掩模。

为了通过蚀刻掩模完全蚀刻外延层以暴露蓝宝石衬底,我们需要通过高离子通量来实现用于形成厚台面的高蚀刻速率。此外,高ICP功率(> 500瓦)会由于蚀刻过程中的掩模损坏或腐蚀而导致侧壁粗糙。使用掩模可以减少掩模边缘的腐蚀,并限制使用氧化物掩模时观察到的柱状物的形成。

我们可以通过增加蚀刻掩模的厚度来延迟SiO2掩模的腐蚀,二氧化硅掩模形状不均匀性的存在会对蚀刻样品的侧壁造成损伤或条纹。我们可以通过优化用于构图SiO2的光刻工艺来减少掩模边界上的这些不规则性。英思特使用在蓝宝石衬底上生长得更厚的GaN外延层,对600nm厚的SiO2掩模进行了实验研究。研究发现二氧化硅掩模似乎是掩模的好选择,因为它提供具有降低的粗糙度和正确的选择性的侧壁。

结论

英思特针对垂直型器件的台面形成,在Cl2/Ar电感耦合等离子体中进行p-GaN/InGaN/n-GaN结构的干法刻蚀。其中蚀刻深度高达3μm,英思特通过蚀刻掩模和等离子体蚀刻工艺的结合,实现了具有光滑侧壁和减少的蚀刻后残留物的台面结构。在我们的研究中,干法蚀刻发展集中在GaN材料的深台面上。

实验表明,在微台面蚀刻的情况下,与SiO2和光致抗蚀剂掩模相比,Ni掩模更适合于深蚀刻工艺。对于超过6μm的蚀刻深度,这种掩模更适于获得良好的选择性和垂直蚀刻轮廓。在500瓦的ICP功率下,相对较高的蚀刻速率为198nm/min。英思特发现垂直和光滑的侧壁台面是为较高的ICP功率产生的,观察到GaN的蚀刻速率随着ICP功率的增加而增加,这归因于等离子体中Cl自由基和离子密度的增加。

审核编辑 黄宇

-

氮化镓功率器件结构和原理2024-01-09 6974

-

有关氮化镓半导体的常见错误观念2023-06-25 29072

-

什么是氮化镓功率芯片?2023-06-15 2485

-

通过热增强提高氮化镓的湿蚀刻速率报告2022-02-09 1084

-

氮化镓充电器2021-09-14 4534

-

《炬丰科技-半导体工艺》GaN 纳米线制造和单光子发射器器件应用的蚀刻工艺2021-07-08 4299

-

什么是氮化镓技术2020-10-27 2659

-

什么是氮化镓(GaN)?2019-07-31 8043

-

什么阻碍氮化镓器件的发展2019-07-08 3169

-

MACOM:硅基氮化镓器件成本优势2017-09-04 4738

-

硅基氮化镓在大功率LED的研发及产业化2014-01-24 4567

全部0条评论

快来发表一下你的评论吧 !