硬件电路设计之时序电路设计

描述

1 简介

上电时序(Power-up Sequeence)是指各电源轨上电的先后关系。 与之对应的是下电时序,但是在电路设计过程中,一般不会去考虑下电时序(特殊的场景除外)。今天,我们主要了解一下上电时序控制相关内容。

2 时序电路设计

今天主要从通用设计方案和专用设计方案两个方面进行进行讲解:

- 通用设计方案

通用的设计方案可以通过分立器件实现和 通用延时芯片实现 。

- 分立器件实现延时

这种方式比较简单,就是利用电容的充电特性。延时的时长,通过改变电容值的大小来实现。具体电路见下:

这种上电方案主要特点是电路结构简单,但上电延时时间难以精确控制,且可能导致上电的过程比较缓慢,在FPGA的上电过程中可以使用。

- 通用延时芯片

我们采用的LM3880芯片进行电源时序控制,这种控制的方式比较简单。LM3880 简单电源时序控制器提供了最简单的方法来控制多个独立电压轨的上电时序和下电时序。通过错开启动序列,可以避免可能影响系统可靠性的锁存情况或大 浪涌电流。

该芯片可以同时实现对上下电的控制,上电与下单的延时时间由EN管脚进行控制,默认是2ms。

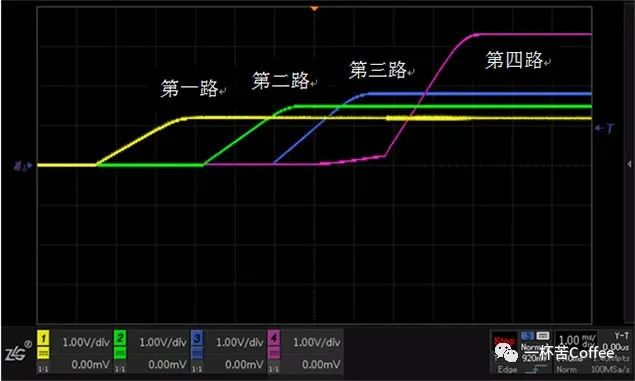

上电时序图见下:

下电时序图见下:

这款芯片还可以对延时的时间进行调整,默认为2ms。如需对 VCC 电压轨提供额外的延迟序列,在 EN 引脚上连接一个电容,见下图:

在使用内部上拉电流源为外部电容 (CEN) 充电的情况下,可通过下面公式来计算使能引脚延迟:

第一个计时器将在上升阈值开始计数,但始终会在第一个输出标志 释放之前 EN 引脚取消置位时复位:

- 专用设计方案

许多FPGA要求不同电源电压轨以特定顺序上电。内核电压的供应往往需要早于I/O电压的供应,否则一些FPGA会被损坏。为了避免这种情况,电源需要按正确的顺序上电。使用标准DC-DC转换器上的使能引脚,可以轻松实现简单的上电时序控制。器件关断通常也需要时序控制,仅执行使能引脚时序控制,很难取得良好的结果。更好的解决办法是使用具有高级集成时序控制功能的PMIC,例如 ADP5014。

更多的内容请参考设计手册。

-

时序电路的分类 时序电路的基本单元电路有哪些2024-02-06 4656

-

时序逻辑电路设计之同步计数器2023-05-22 5740

-

什么是同步时序电路和异步时序电路,同步和异步电路的区别?2023-03-25 30055

-

基本逻辑电路、时序电路、组合电路设计2022-10-10 2826

-

同步时序电路设计2018-10-31 1747

-

组合电路和时序电路的讲解2018-09-25 26201

-

Verilog设计初学者例程:时序电路设计2018-08-23 2551

-

异步时序电路设计2017-12-08 3420

-

基于FPGA技术的RS232接口时序电路设计方案2017-01-26 1325

-

数字电路之时序电路2016-08-01 19814

-

同步时序电路2010-01-12 5868

-

基本时序电路设计实验2009-10-11 3238

-

时序电路设计实例 (Sequential-Circuit D2009-09-26 788

-

时序电路设计串入/并出移位寄存器2009-03-13 6374

全部0条评论

快来发表一下你的评论吧 !