Xilinx VIO介绍和应用场景

描述

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的。其实Xilinx还提供了一个叫VIO的core,可以动态改变FPGA内部某个信号的值,但是一直没有用过,一来对于以前的项目来说,没有应用场景,通过寄存器就可以配置了;二来感觉这个东西不是很“实用”。

背景

在项目中,本来是通过PCIe来配置寄存器的,但是由于某些原因PCIe接口一直有问题,无法配置。FPGA内实现了一个功能,可以根据寄存器的值来执行不同的操作,这个时候就发现无法上板测试,因为没有办法配置寄存器。这个时候突然想到了VIO这个core。

VIO介绍

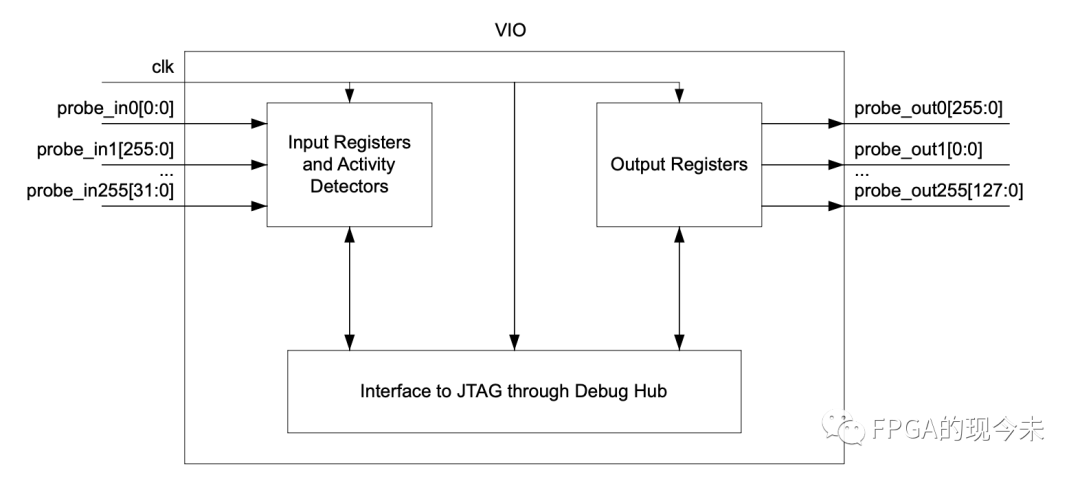

VIO 这个core其实非常的简单,没有什么太多需要介绍的,可以参考 PG159 ,这里做一个简单的说明。框图如下图所示:

该模块就是定义了一些输入和输出,其中可以定义的输入和输出信号的个数最多为256个,每个信号的位宽最大为256bit。在例化的时候只需要确定需要监控的信号个数,以及每个信号的位宽;或者需要控制的信号个数和每个信号的位宽即可。

场景应用

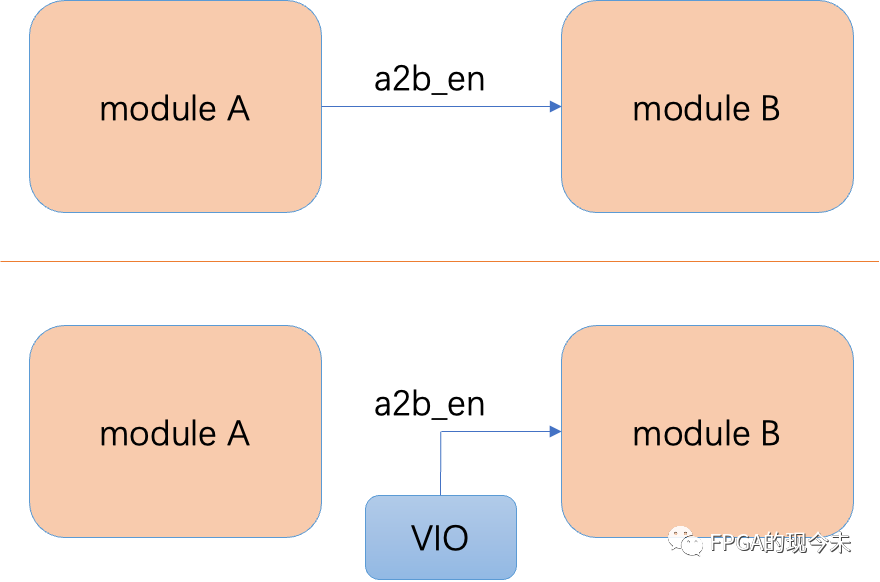

比如我们有如下一个场景,A模块输出一个控制信号a2b_en给B模块,从而控制B模块的工作方式。但是A模块目前还不能产生该信号,笔者的项目中,A模块就是PCIe模块,由于没有调通,还无法通过配置来控制a2b_en信号。

这个时候,我们例化了一个VIO模块,只用它的输出,并将这个输出连接到B模块的输入信号a2b_en上即可。

在加载后,vivado会弹出调试窗口,通过该窗口,我们可以看到控制信号a2b_en,这个时候就可以设置它的值为0还是为1.

当然上述例子中我们只是用了它的output,其input的使用就和ila有点类似了。

总结

当我们需要动态的修改FPGA内某些寄存器的值时,除了通过软件寄存器配置的方式,还可以通过例化VIO的方式来实现修改。另外VIO和ila一样也可以监控内部信号的值,当我们只是简单的观测下某个信号时,可以采用VIO,因为相比ila,它不需要缓存,当然对于复杂的问题分析,ila还是更胜一筹。

-

Switch的应用场景2025-12-12 194

-

XILINX FPGA Debug with VIO and TCL2012-03-08 5188

-

MOS管的应用场景2018-11-14 6517

-

=>的使用场景有哪些2020-10-27 1714

-

FPGA的应用场景2021-07-28 1904

-

ARM的技术特征是什么?应用场景有哪些?2021-11-05 3529

-

几种LED调光协议分析及具体应用场景介绍2021-12-31 2285

-

MS9331的应用场景是什么?2022-02-11 2080

-

RK3308的特点及应用场景是什么?2022-03-09 2111

-

Firefly集群服务器的应用场景资料介绍2022-08-04 3581

-

SMT组装工艺流程的应用场景2023-10-20 1250

-

labview 和 wincc 的区别 使用场景2023-10-27 5579

-

Vivado之VIO原理及应用2021-09-23 11777

-

meshtastic的应用场景介绍2025-02-21 1628

-

Xilinx FPGA串行通信协议介绍2025-11-14 2786

全部0条评论

快来发表一下你的评论吧 !