FPGA优质开源模块-SRIO IP核的使用

描述

本文介绍一个FPGA常用模块:SRIO(SerialRapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

由于Vivado中RapidIO IP核需要付费才能使用,因此本文提供完整工程源码。文章末尾有该工程源码获取方式,有需要的小伙伴可以收藏、分享一下。

01

软硬件平台

软件平台:Vivado 2017.4;

硬件平台:XC7K410T...;

02

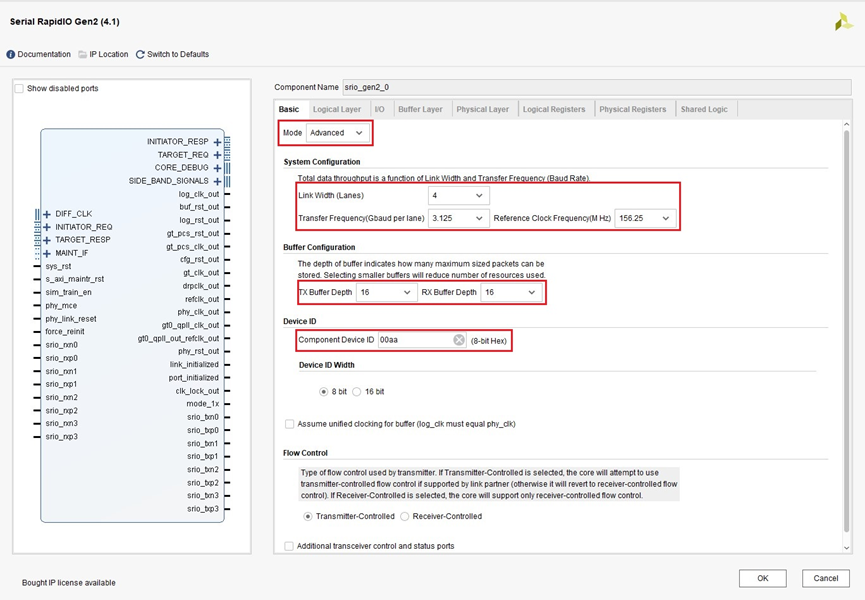

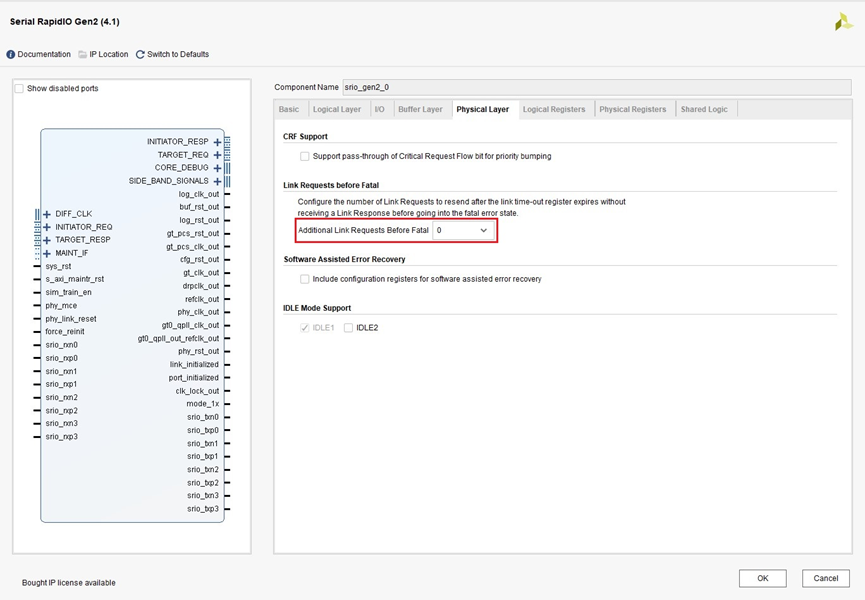

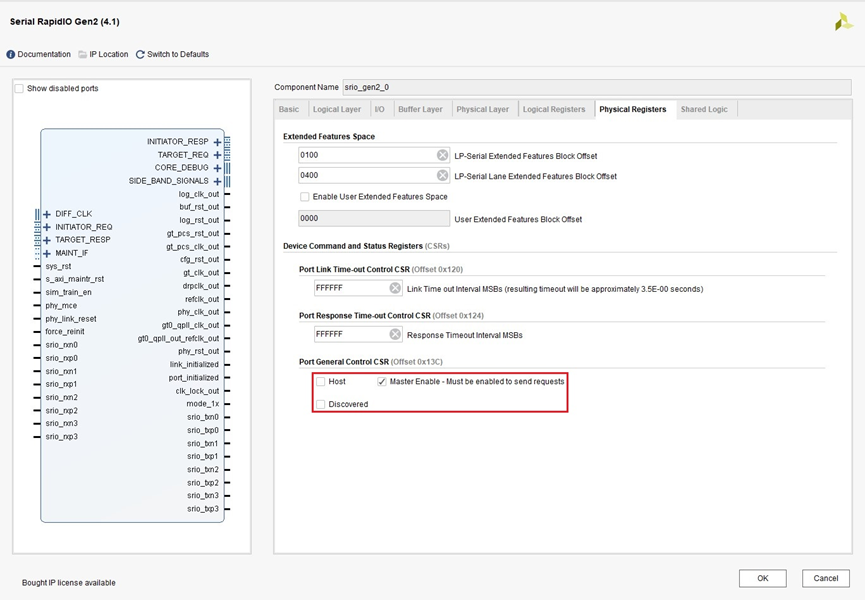

IP核参数配置

本工程SRIO IP核参数配置如下图所示,仅供参考:

03

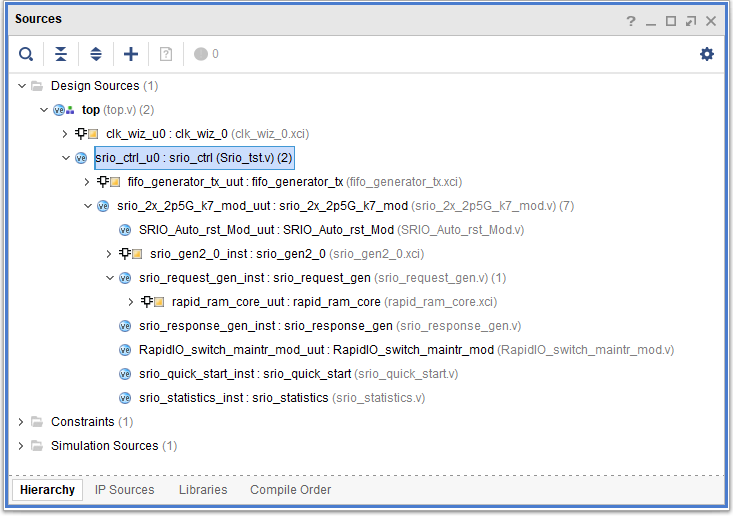

工程源码结构

下图是SRIO工程源码结构:

其中,

SRIO_Auto_rst_Mod:SRIO自动复位模块;

srio_request_gen:SRIO请求事务生成模块;

srio_response_gen:SRIO响应事务生成模块;

RapidIO_switch_maintr_mod & srio_quick_start:SRIO维护事务生成模块。

04

实现功能

该FPGA SRIO模块采用NWRITE类型事务往DSP目的地址传输数据,每包数据大小为256字节。数据写入完毕后,通过DOORBELL事务给DSP发送数据接收中断。另外FPGA端通过RapidIO IP核m_axis_treq接口接收来自DSP的数据。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA的IP软核使用技巧2024-05-27 3421

-

关于FPGA IP核2024-04-29 2166

-

基于FPGA的SRIO协议设计2023-09-04 2670

-

fpga ip核是什么 常用fpga芯片的型号2023-07-03 10425

-

SRIO IP核的三层协议的作用解析2023-04-25 2832

-

SRIO IP核的三层协议的作用?2023-03-03 1841

-

#FPGA点拨 如何验证带有IP核的代码电子技术那些事儿 2022-10-12

-

FPGA-串口通信模块(含IP核)2022-06-20 833

-

基于IP核的FPGA设计方法是什么?2021-05-08 1725

-

FPGA实现基于Vivado的BRAM IP核的使用2020-12-29 13683

-

采用EDA软件和FPGA实现IP核保护技术2019-07-29 2825

-

FPGA中IP核的生成2015-11-30 982

-

FPGA IP核的相关问题2013-01-10 3066

全部0条评论

快来发表一下你的评论吧 !