Efinity Interface Designer报错案例-v0

描述

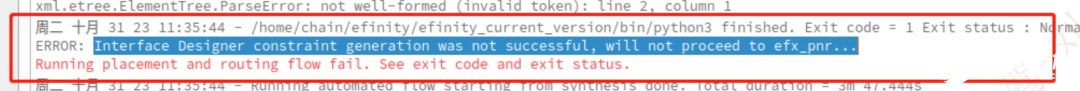

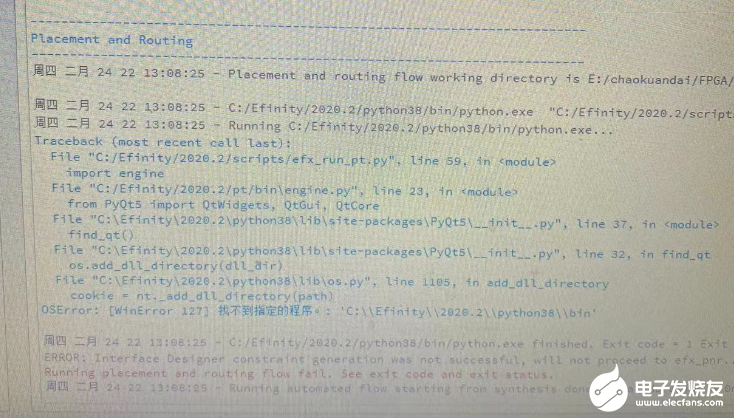

(1)ERROR:Interface Designer constraint generation was not successfull,will not proceed to efx_pnr...

原因:(1)有些客户使用Win7版本,目前Efinity对Win7的支持不好。建议升级成win10。

(2)杀毒软件删除了文件,实际interface生成约束是没有问题的,客户pnr的时候就报错,需要重新安装软件。

(3)电脑存在加密系统 。造成的现象是新建工程时interface可以打开,但是生成xxx.peri.xml文件之后再次打开就会报错。

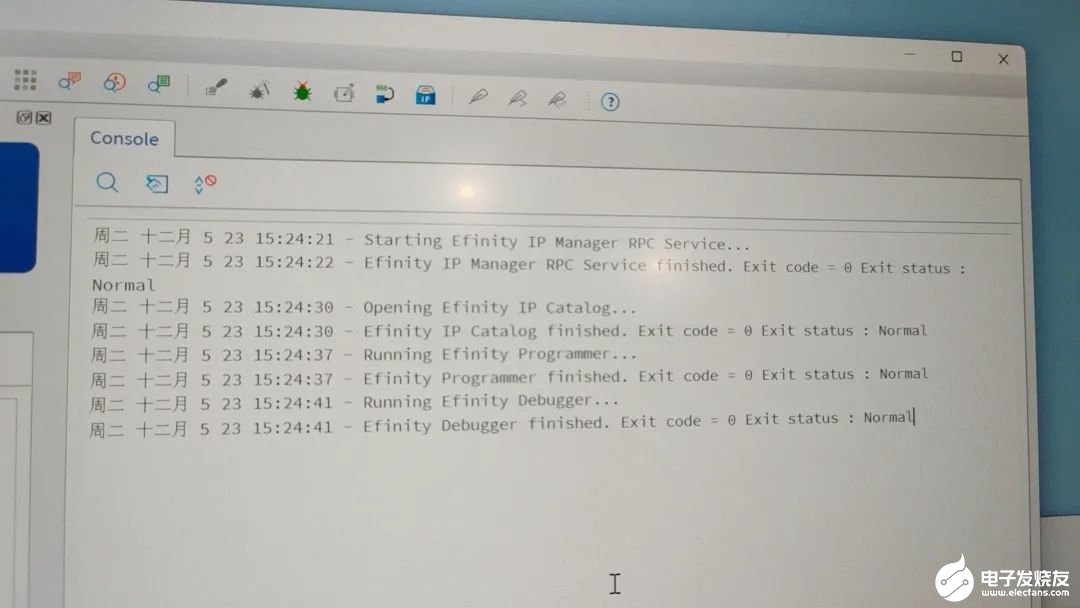

(2)Interface打不开。

现象:(1)打开interface的时候指示: Efinity Interface Designer finished. Exit code = 1 Exit status : Normal Interface design file exists, check and migrate done (2)新建工程第一次可以打开interface Designer (3)删除xxx.peri.xml之后,第一次也可以打开Interface Designer. 原因:电脑存在加密 (3) interface打不开 打开interface Designer时会报以下错误。 Efinity IP Catalog finished.Exit code = 0 Exit status:Normal

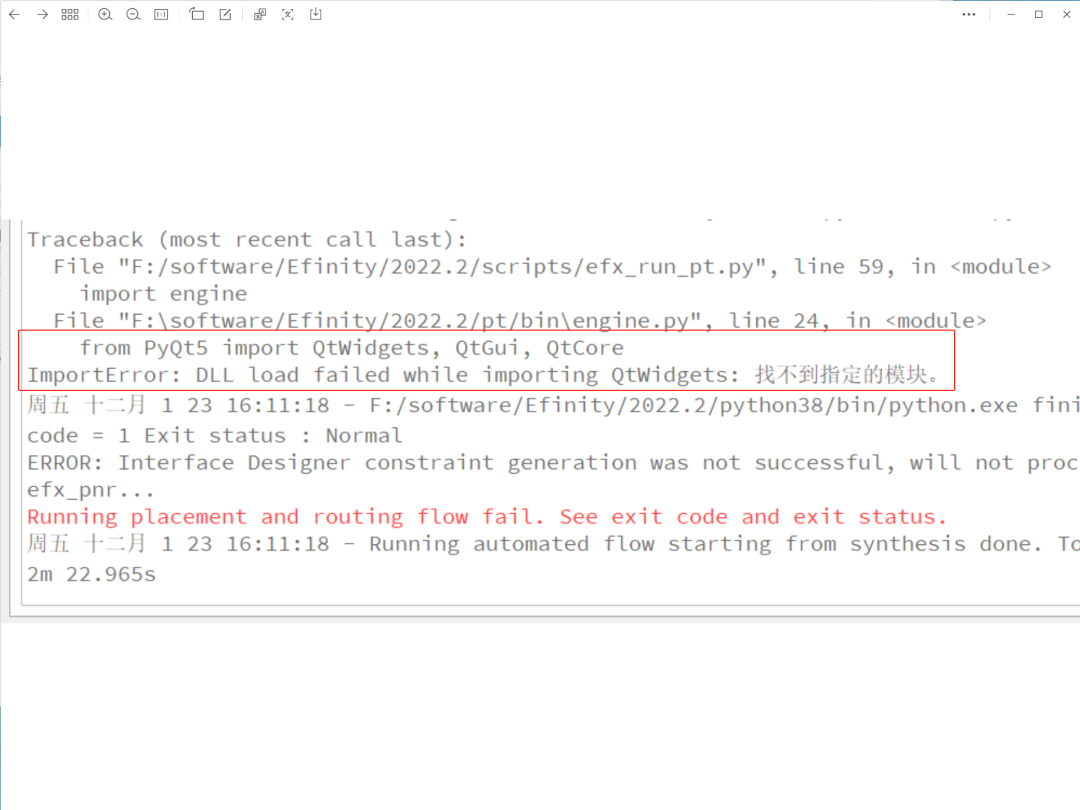

编译过程可能报以下错误:

ERROR: Interface Designer constraint generation was not successful, will not process pnr..

解决方案:安装VC_redist.x64.exe,注意参考软件安装指导的版本。

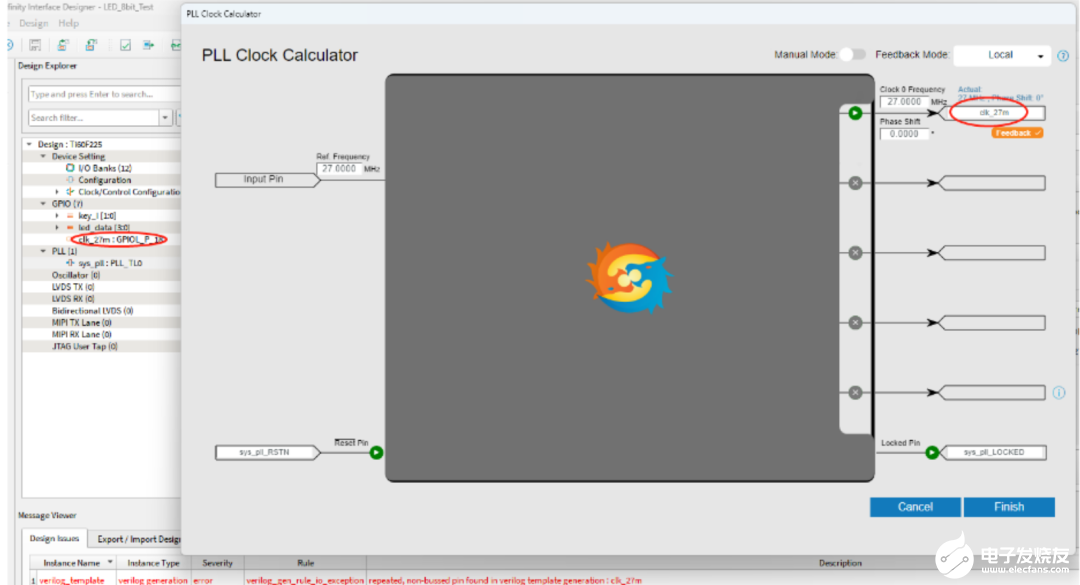

(4)repeated,non-bussed pin found in verilog template generation:clk_27m

说明:在GPIO处定义了一个clk_27m,在pll的输出上又定义了一个clk_27m,两个信号名冲突。

(5)ERROR: Interface Designer constraint generation was not successful, will not process pnr..

原因:1)一般是软件有360或者别的杀毒软件的相关文件删除了,需要找回文件或者重新安装软件。

2)客户使用Win7版本,目前Efinity对Win7的支持不好。建议升级成win10。

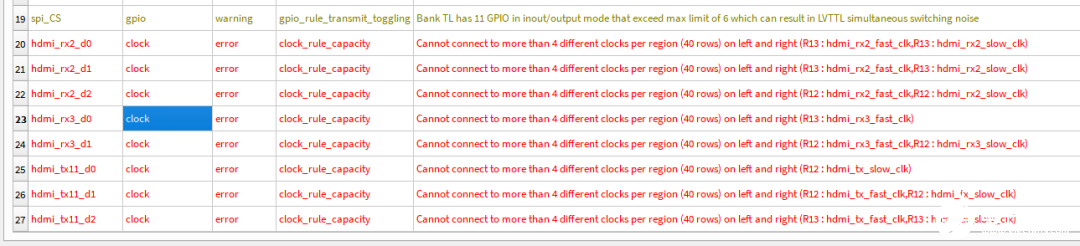

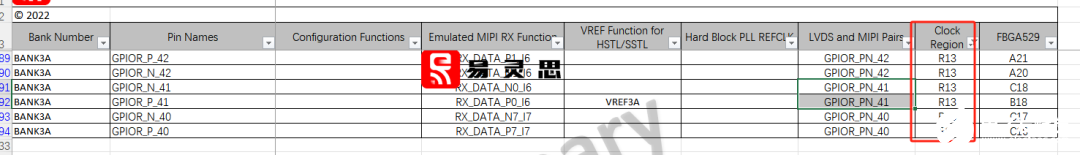

(6)cannot connect to more than 4 different clocks per region on left and right

原因是在pinout文件中对应的Clock Region中,不能超过4个时钟去驱动。

也就是GPIOR_PN_42,41,40三组差分对,不能由两组LVDS来驱动,因为每组LVDS时钟有lvds_fast_clk和lvds_slow_clk两个,两组就会有4个时钟在Region clock R13区域。

结论就是把LVDS差分对放在同一个Clock Region.

审核编辑 黄宇

-

ramsey_wang

2023-12-12

0 回复 举报HELLO,请问可以微信联系吗/ 收起回复

ramsey_wang

2023-12-12

0 回复 举报HELLO,请问可以微信联系吗/ 收起回复

-

Efinity软件安装-v52024-11-01 2152

-

TINA仿真OPA846的频率响应时,大信号(V0=2VPP),小信号(V0=0.2VPP)响应一样,是怎么回事呢?2024-08-19 328

-

LMV331如何让前级电路不输出V0波形的时候保证比较器输出低电平?2024-08-01 478

-

Efinity Interface Designer报错案例-v22024-04-07 2625

-

Efinity Interface Designer报错案例-v12023-12-12 2623

-

示波器DSO804A开机自检失败报错案例2023-10-27 1958

-

Efinity版本更新可能遇到的问题及解决办法2023-02-14 1770

-

基于FreeRTOS+LwIP的SNMP实现方案V02022-10-18 952

-

The Wasp Topdeck板专为Voron V0 IDEX打印机变体而设计2022-06-28 790

-

这个运放的输出V0是如何推导出来的?2019-12-19 3323

-

如何计算图中V0的输出电压?2019-09-06 4577

-

什么是V0主网在当前的区块链世界有什么不同2019-07-01 2449

-

LP236声音感应LED驱动芯片中文规格书_V02016-12-12 1172

-

V0图形是什么样子的?2012-03-10 3271

全部0条评论

快来发表一下你的评论吧 !