FPGA通过SPI对ADC配置简介(三)3线SPI配置时序分析

描述

AD9249的SPI控制模块包含4根信号线,即CSB1、CSB2、SDIO以及SCLK。但CSB1、CSB2可以一起由CSB来控制,实际上就是3线SPI。由于3线SPI数据的读、写操作在同一根信号线SDIO上实现,因此其配置方式与4线的配置稍微有些不一样。下面我们将详细介绍读写操作:

CSB:SPI控制读写使能信号;

SDIO:SPI的数据、地址读写端口;

SCLK:FPGA提供给ADC的SPI接口时钟;

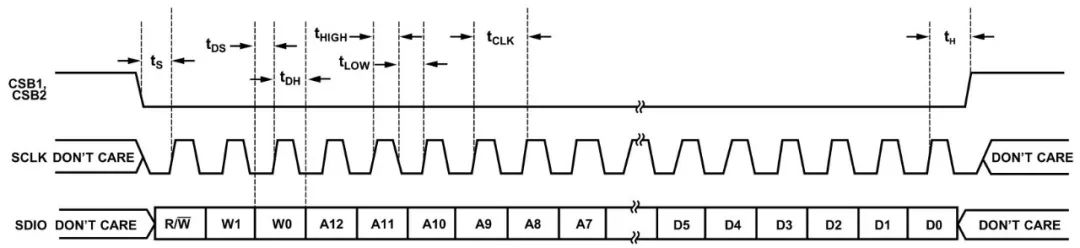

如下图1所示为该ADC的SPI读、写配置时序图。其中CSB和SCLK的操作和上篇介绍的4线SPI配置相同,图上的时序参数在其datasheet上也有明确的说明,这里就不介绍了。

3线SPI与4线SPI配置的主要不同之处在传输的数据格式以及I/O转换上。其读写数据格式由控制命令+地址+数据组成,而上篇提到的4线配置只有地址+数据。

图1:SPI读、写时序图

其中R/~W为高电平时,表示读操作,低电平表示写操作。W1,W0表示要读写的数据字节数,一般都设为0,代表每次读写一个寄存器地址的数据。A12~A0表示13bit的寄存器地址。D7~D0表示要读写的8bit寄存器数据。

因此我们在SPI写操作时,只需写入1bit 1 + 2bit 0 +13bit地址+ 8bit数据 即可。其配置的方法和上篇的4线SPI写操作相同。但当我们在执行SPI读操作时,就需要注意了:

首先需写入1bit 0 + 2bit 0 +13bit 地址,当最后1bit的地址A0在SCLK的上升沿写入SDIO后,SDIO会由输入口变为输出口,然后在接下来的8个SCLK下降沿,SDIO会输出寄存器的8bit数据。因此,在ADC的SDIO由输入变为输出口时,FPGA端的SDIO必须同步由输出口变为输入口,并在SCLK上升沿接收这8bit数据最稳定,FPGA端口的这种I/O转换可以通过其内置的三态门来实现。

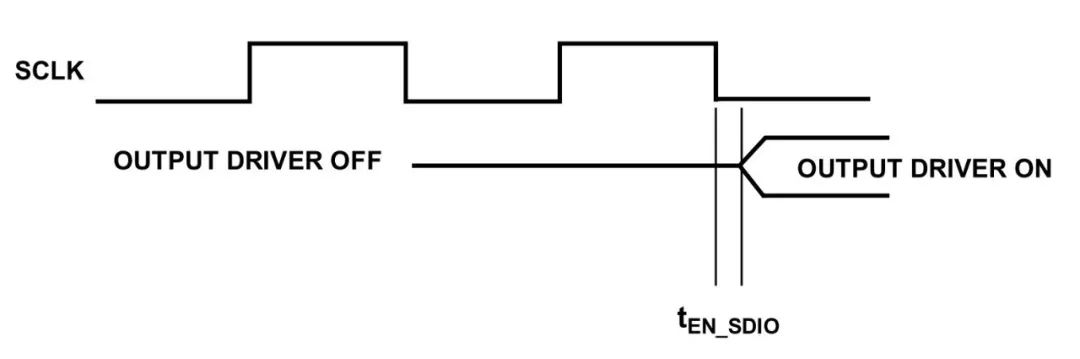

如图2所示为SDIO由输入口变为输出口的时序控制图,tEN_SDIO为转换时间,其最小时间为10ns,参考零点为SCLK下降沿。

图2:SDIO输入转换为输出的时序图

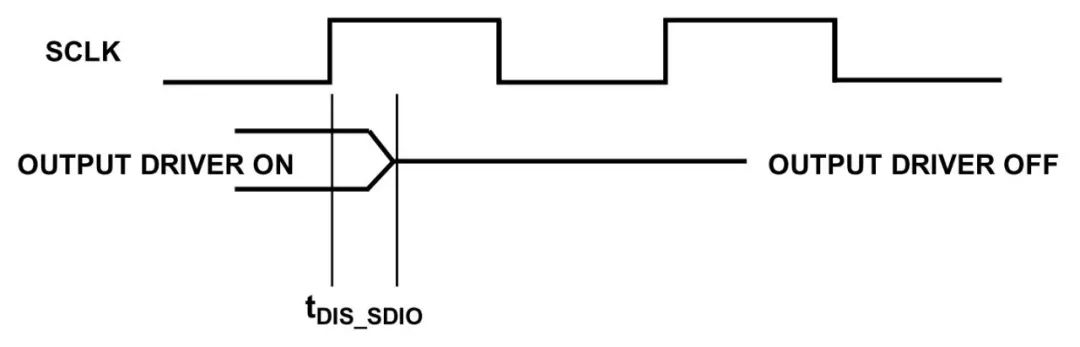

如图3所示为SDIO由输出口变为输入口的时序控制图,tDIS_SDIO为转换时间,其最小时间也为10ns,参考零点为SCLK上升沿。

图3:SDIO输出转换为输入的时序图

3线SPI的读写时序分析就介绍到这里了,同样强调几个关键点:

关键点1:CSB在读写操作时,必须拉低。读写完成之后,必须拉高。

关键点2:SDIO作为输入口时,数据每次必须在SCLK的上升沿写入SPI。

关键点3:SDIO作为输出口时,寄存器数据每次在SCLK的下降沿输出SPI,FPGA端在SCLK的上升沿处捕获数据最稳定。

关键点4:一定要满足datasheet给出的SPI的时序参数,并在代码实现时要留有适当的时序裕量。

关键点5:注意FPGA端的SDIO口的三态控制逻辑,以便正确读写ADC寄存器。

本篇以Analog Device(ADI)的多通道高速ADC芯片AD9249为例,简要介绍了ADC的3线SPI配置时序,希望我们能一起学习、一起进步!下篇将具体介绍如何用verilog实现FPGA通过SPI对ADC进行配置。

审核编辑:刘清

-

FPGA通过SPI对ADC配置简介(二)-4线SPI配置时序分析2023-12-11 3663

-

Gowin FPGA产品Slave SPI配置手册2022-09-15 593

-

STM32中SPI配置过程简介2022-02-17 900

-

一文看懂SPI协议2022-01-25 839

-

STM32学习笔记--SPI2021-12-22 1017

-

在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序2021-09-16 1641

-

在FPGA上编写通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序2021-03-10 1392

-

STM32的SPI接口、cubeMX软件配置SPI接口和分析SPI相关代码2020-09-24 17936

-

FPGA通过SPI对ADC配置简介-----什么是SPI?2020-09-07 6186

-

SPI方式FPGA配置和SPI flash编程2011-05-16 1126

-

FPGA中SPI复用配置的编程方法2010-01-06 3988

全部0条评论

快来发表一下你的评论吧 !