ARM系列—PCK600基础知识简析

电子说

描述

PCK-600是一个与功耗控制相关IP包,里面包含了六个组件,分别是LPD-Q,LPD-P,LPC-Q,P2Q Converter,CLK_CTRL和PPU。前面四个是辅助组件,后面两个才是这个IP包中的重要角色,我们一个一个来看。

LPD-Q

LPD-Q全称是Low Power Distributor Q-Channel,其作用是帮助带Q-Channel接口的控制器能够控制多个Q-Channel设备,并可能对其进行排序。

LPD-Q支持2-32设备Q-Channel接口,可配置为在以下两种模式(通过SEQUENCER参数)运行:

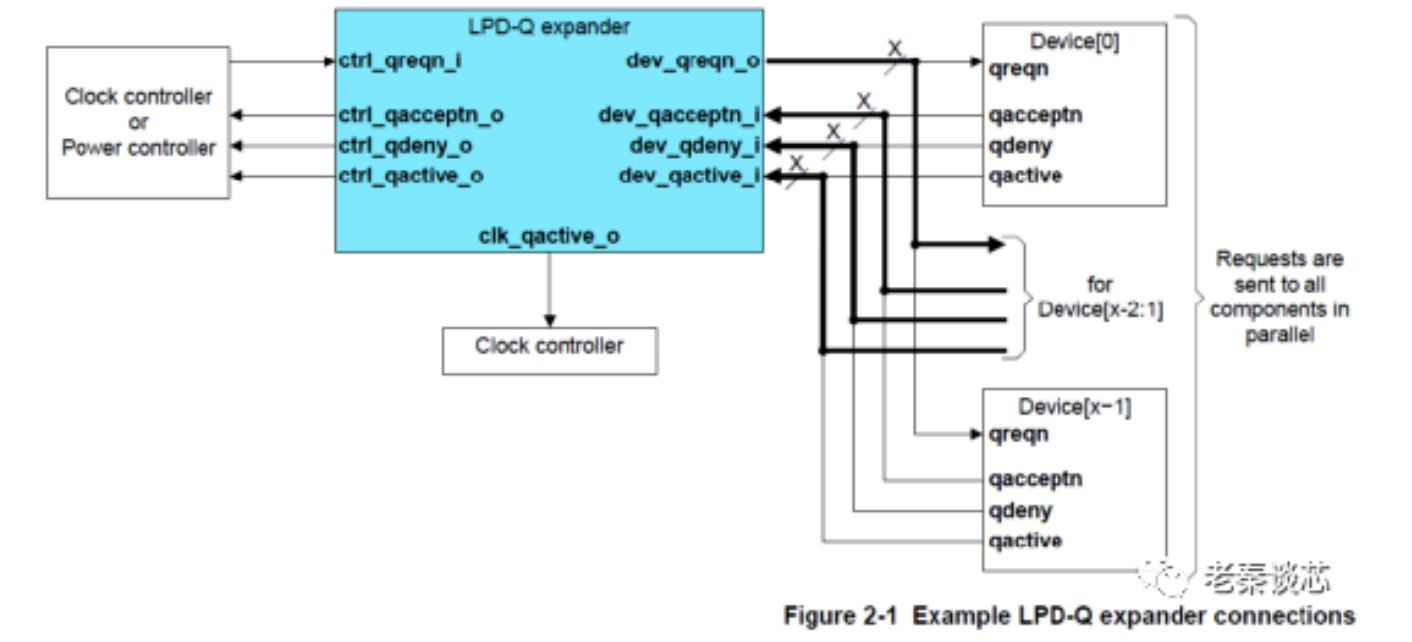

Q-Channel扩展器(Expander):控制器Q-Channel转换请求并行广播到所有设备Q-Channel。发送到设备的转换请求可以按任何顺序完成。在这个模式下,当LPD-Q在控制Q-Channel上收到静态进入或退出请求时,它会将该请求发送到所有设备Q-Channel。LPD-Q等待所有设备接受或拒绝,然后生成对控制器的响应。当出现拒绝情况时,LPD-Q会将所有设备Q-Channel返回到运行状态。

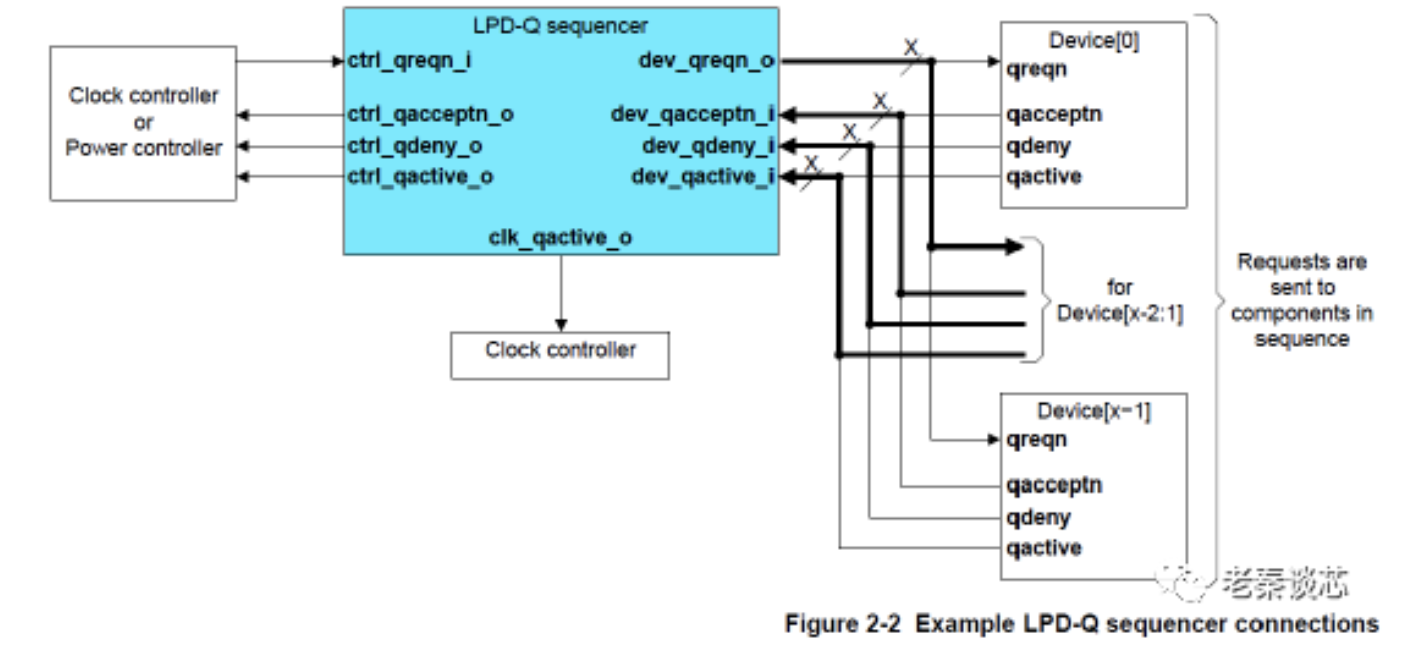

Q-Channel序列器(Sequencer):控制器Q-Channel转换请求按顺序传递给每个设备Q-Channel。每个转换请求必须在LPD-Q向下一个设备发送转换请求之前完成。在这个模式下,当LPD-Q在控制Q-Channel上接收到静态进入或退出请求时,它会依次向所有设备Q-Channel发送请求。LPD-Q等待每个设备的响应,然后再向下一个设备发送静止请求。LPD-Q在生成对控制器的响应之前,等待所有设备响应。

总结一下:LPD-Q是把一个Q-Channel扩展成多个Q-Channel,就这么简单。至于为什么要扩展,那一定是前面的控制器没那么多接口呗。

LPD-P

跟LPD-Q组件类似,LPD-P组件使P-Channel控制器能够控制多个P-Channel设备,并可能对其进行排序。不同的是,LPD-P使用的是P-Channel。LPD-P支持1-8个设备P-Channel接口,也是可以配置成两种模式:expander和sequencer。

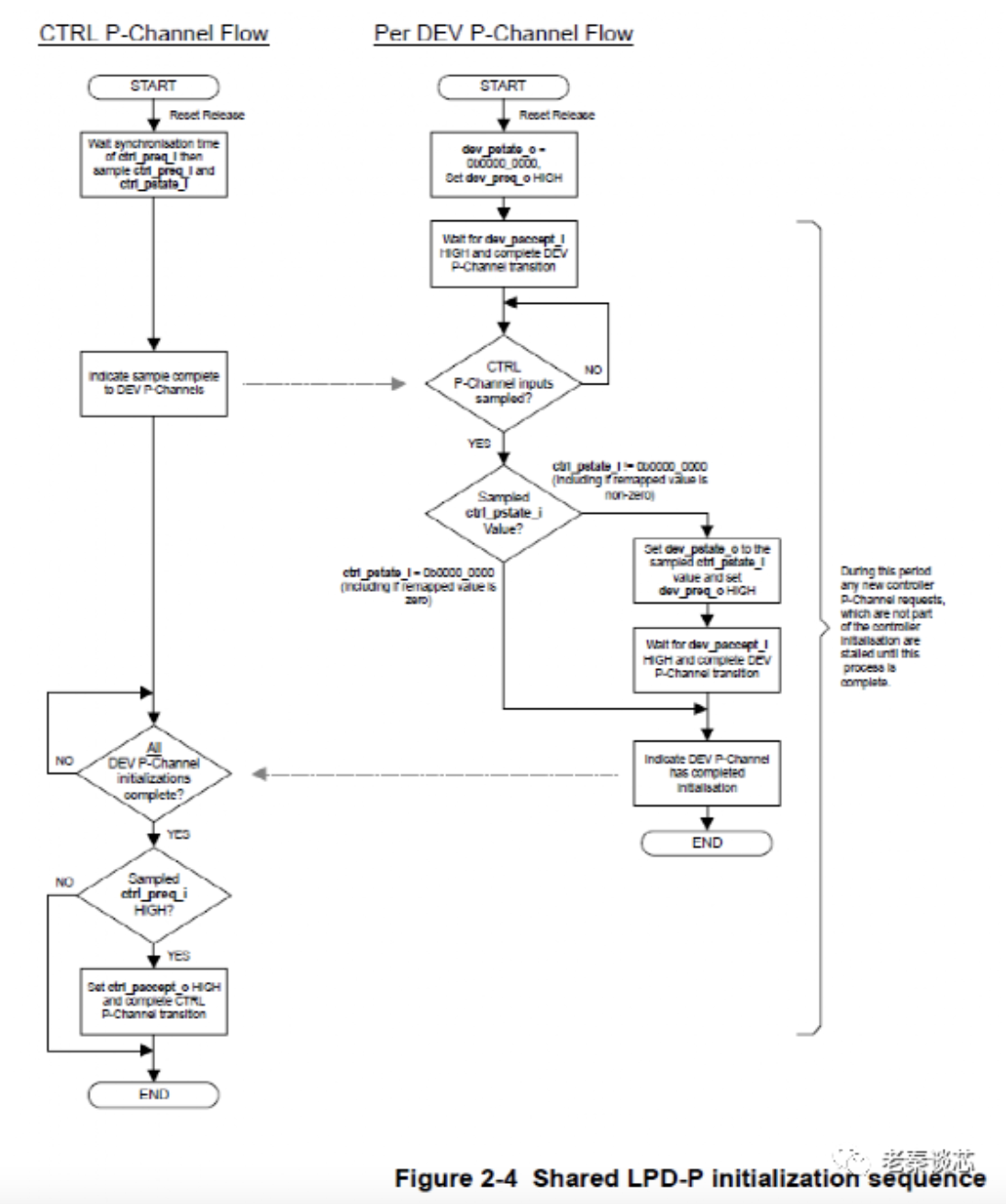

LPD-P将所有设备的P-Channel初始化为0x00,这是PCSA关闭电源模式。如果LPD-P设计用于不兼容的PCSA体系结构,则只支持较低的4位(PSTATE[3:0]),最多16种电源模式,PSTATE[7:4]位保留。

LPD-P在复位信号被释放后,将PREQ置高。这会消除复位和时钟使能之间的依赖。这里跟LPD-Q的区别主要还是P-Channel引起的。

总结一下:LPD-P与LPD-Q类似,所不同的就是接口类型从Q-Channel换成了P-Channel,而已。

LPC-Q

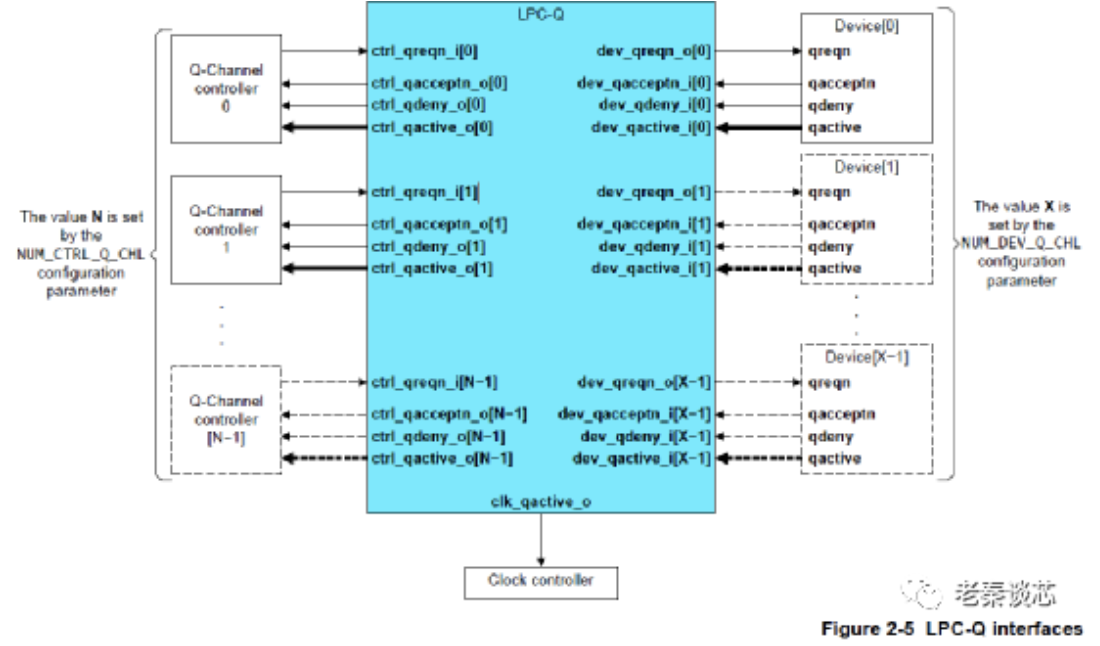

LPC-Q的全称是Low Power Combiner Q-Channel,用于两个或多个Q-Channel控制器控制一个或多个具有相同控制要求的设备。当任何控制Q-Channel请求静止时,LPC-Q将设备Q-Channel移动到静止状态。当最后一个控制Q-Channel退出静止状态时,设备Q-Channel退出静止状态。

LPC-Q支持2-32个控制接口,1-32个设备接口。

总结一下:LPD-Q是一对多控制,即一个控制器接口,多个设备接口。而LPC-Q是多对一或者多对多控制。在实际的应用中,要格外注意PLC-Q的使用,确保被控制设备能够正确进入静止状态。

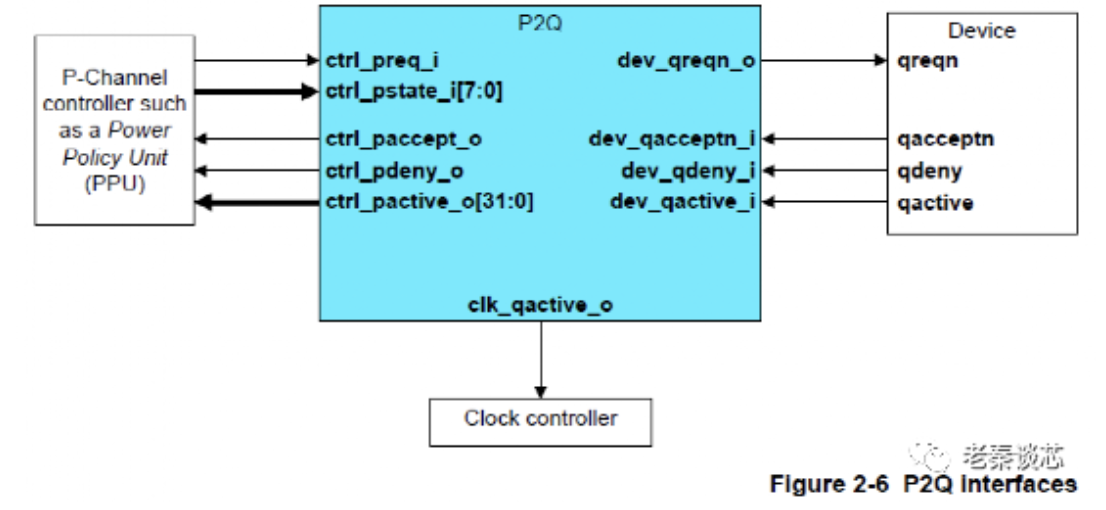

P2Q converter

P2Q converter将单个P-Channel转换为单个Q-Channel。P2Q支持PSTATE最大8-bit宽度,PACTIVE最大32-bit宽度。

这个组件没啥可总结的了。

有了以上四种辅助组件,对于电源和时钟的控制路径设计就灵活多了,是不是很像搭积木。

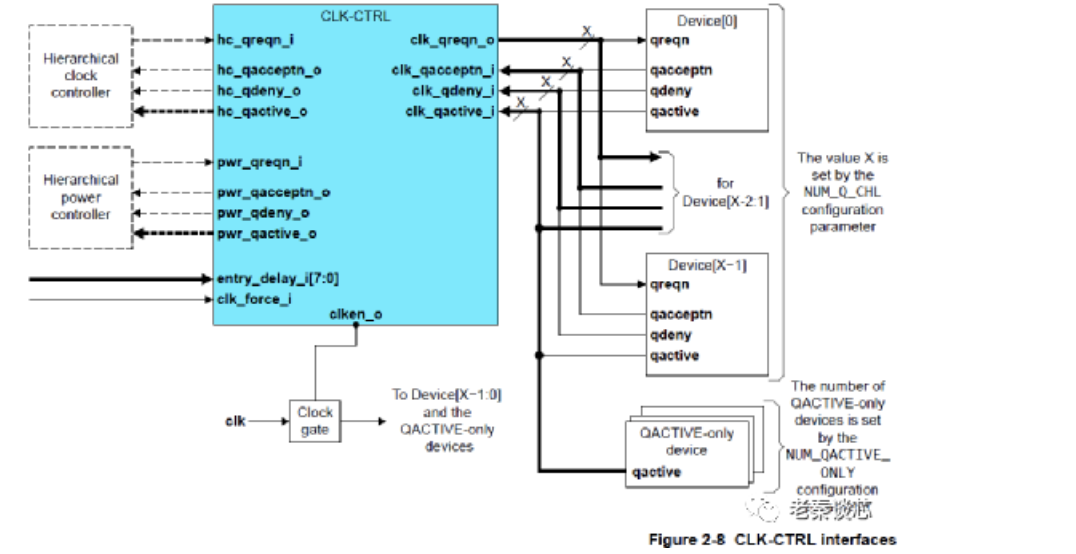

CLK-CTRL

CLK-CTRL是Clock Controller的缩写,为时钟域中支持Q-Channel低功耗接口(Low Power Interface,LPI)时钟选通的设备提供高层次的时钟控制。CLK-CTRL使用Q-Channel确保设备先进入静止状态,然后关闭设备时钟。

CLK-CTRL监控Q-Channel的clk_qactive_i输入,以了解何时必须执行Q-Channel请求。当所有Q-Channel都处于静止状态时,CLK-CTRL将clken_o设置为低,以停止时钟。当任何一个clk_qactive_i变高时,CLK-CTRL将启用时钟,并将所有设备Q-Channel移至运行状态。

通过改变entry_delay_i[7:0]可以配置CLK-CTRL在滞后0-255个时钟周期后再进入禁止状态。通过控制输入信号clk_force_i可以关闭CLK-CTRL的时钟关断功能,也就是输出时钟一直打开。

要注意控制器端的两组Q-Channel接口,一组是Hierarchical clock control Q-Channel(简称HC),另外一组是Hierarchical power control Q-Channel(简称PWR)。HC允许更高级别的时钟控制器向CLK-CTRL发出请求;PWR允许更高级别的电源控制器向CLK-CTRL发出请求。

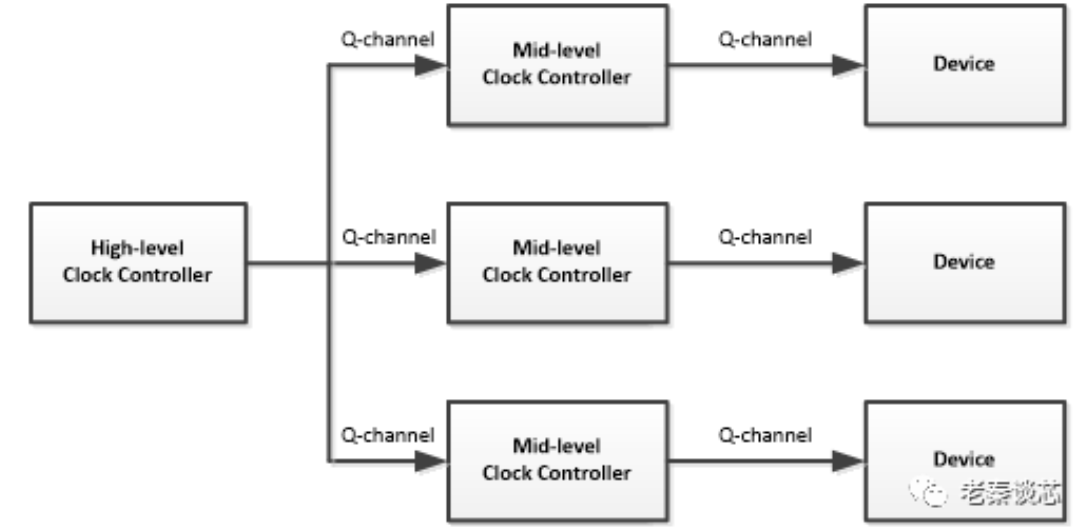

这里稍加解释,时钟控制器可以是级联控制,所以对于系统中的某一个CLK-CTRL来说,可能有更高层级的CLK-CTRL来控制它,例如下图。

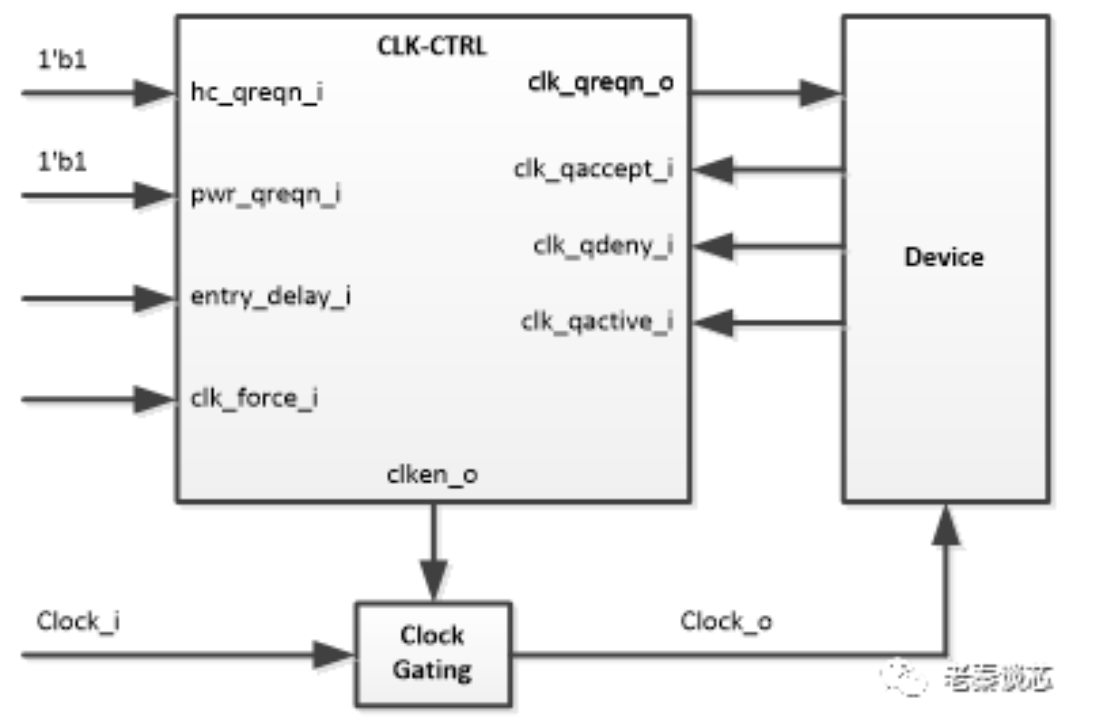

对于PWR接口也好理解,如果被控制的设备需要做电源开关,那么在设备掉电前,需要先关闭设备的时钟,确保此设备处于非工作状态。因此,PWR接口就是留给电源控制器去控制设备的时钟用的。如果用PPU作为电源控制器,这个PWR接口就不一定需要用了,因为PPU本身就带有时钟控制逻辑,也就是有一个输出信号clk_enable用于做时钟开关。

HC和PWR两组接口是否需要用取决于具体实现。如果只想让CLK-CTRL根据设备的状态来决定是否关断设备的时钟,那么就可以把HC和PWR接口设置成固定值。

总结一下:CLK-CTRL由于有了HC和PWR两组接口,用起来就比较灵活了。

PPU

PPU在之前分析过很多次了,具体功能就不再说了。

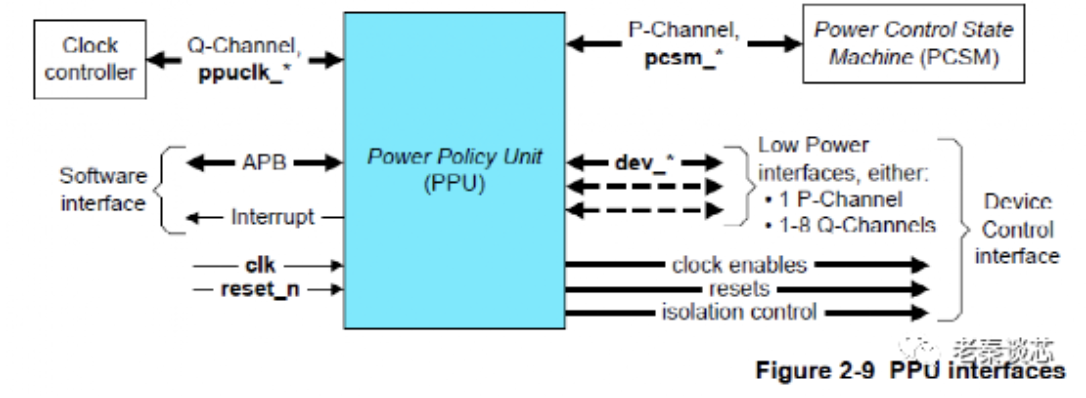

PPU接口比前几个组件复杂一点:

- 配置接口:APB

- 时钟控制器接口,这个接口在PPU的架构spec(1.1版本)中没有

- 中断接口

- PCSM接口

- 设备LPI接口:Q-Channel(1-8个)或P-Channel(1个)

- 设备控制接口

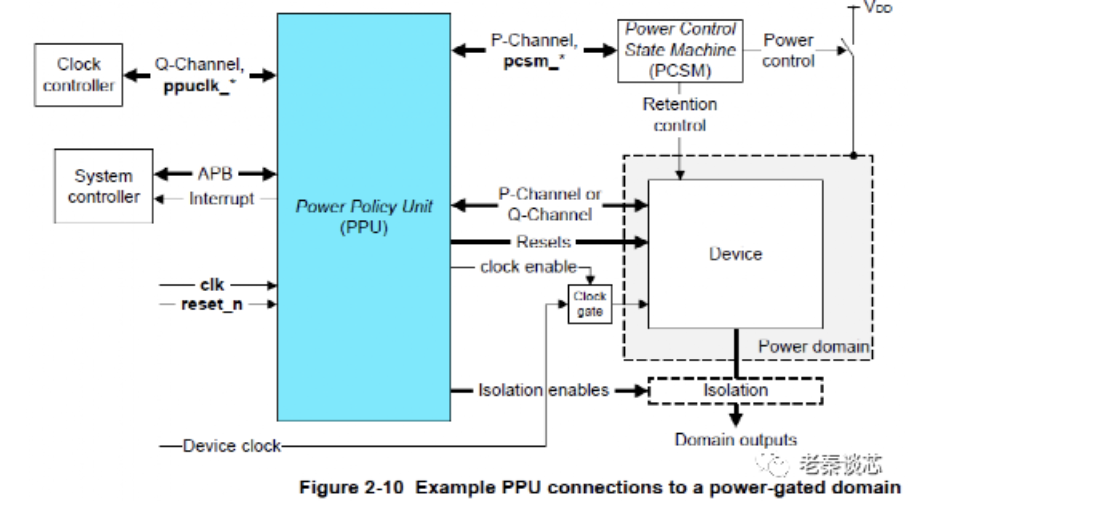

PPU在系统的典型应用如下图:

总结一下:用PPU做电源控制器,需要额外设计PCSM。由于PPU有了一组时钟控制的Q-Channel接口,在设备关闭电源的情况下,PPU可以关闭时钟,节约一点点功耗。

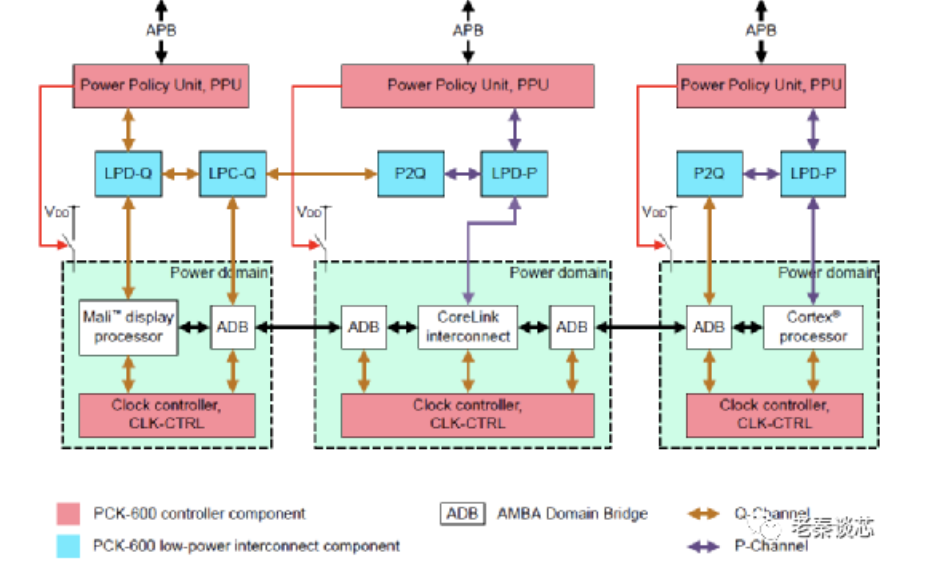

最后,放一张用PCK-600组件做电源/时钟控制的示意图。

-

阻燃系列基础知识2026-02-06 590

-

汇编基础知识教程之ARM汇编简介2023-01-30 2145

-

ARM架构基础知识点汇总2021-12-13 1960

-

ARM汇编基础知识点汇总,错过肯定后悔2021-11-29 1604

-

单片机MSP430系列的CCS基础知识2021-08-23 1309

-

ARM架构基础知识小结2020-12-29 2621

-

ARM基础知识2018-01-25 5355

-

电源管理基础知识电源管理基础知识电源管理基础知识2017-09-15 1758

-

浅谈ARM处理器基础知识2017-01-14 757

-

arm内核基础知识介绍2016-01-08 798

全部0条评论

快来发表一下你的评论吧 !