使用Genus retime技术的实现原理

描述

设计中经常会碰到一些非常复杂的逻辑,组合逻辑层数非常多,往往造成无法满足设计的时钟频率要求。

Cadence综合工具Genus支持retime技术。

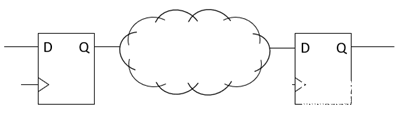

Retime技术的原理非常简单。例如下图,两级flop之间的组合逻辑太大,限制了时钟频率。

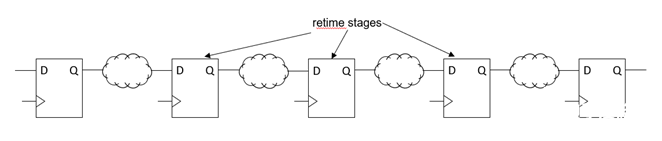

Retime技术类似pipeline。Retime技术在两级flop之间插入retime stage flop,把复杂的组合逻辑分割成里几个部分,每个部分的组合逻辑层数都相对较小,使得每一级都能工作在较高的频率,从而满足整个设计的时钟要求。

当然,retime技术不是“免费”的。

- 插入了中间级,latency增加了。上图中latency增加了3个cycle。

- 插入了中间级flop,面积功耗都会大一些。

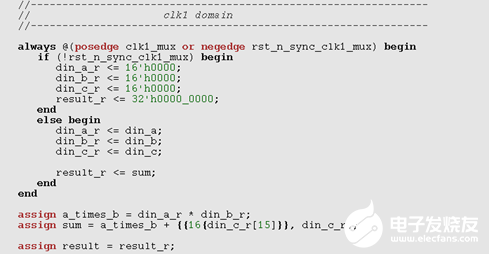

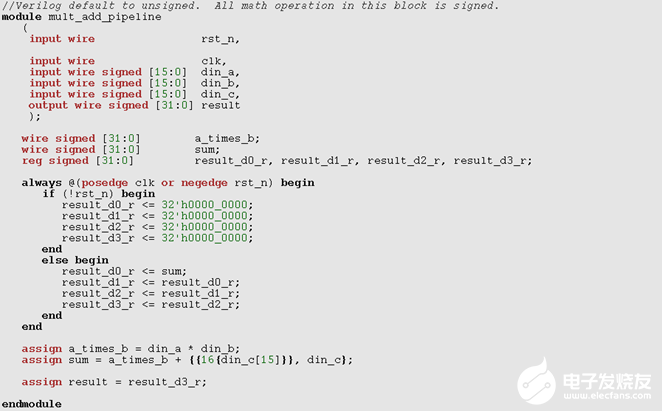

下面是一个实例。这个设计实现乘+加(multiply-add)运算。这类运算在DSP中很常见。这里的乘法器是16位输入乘16位输入,得到32位结果,再和符号扩展(sign extended)后的第三个输入相加。

综合用Genus,target 65nm的库。顺便插一句,很多朋友总以为只要上了先进工艺,timing的问题就解决了。做产品与做科研不同。做产品是要讲成本的。上了先进工艺只能说明你资金充裕。使用成熟工艺,虽然慢很多却能实现一样的performance,这才是真正的设计能力。

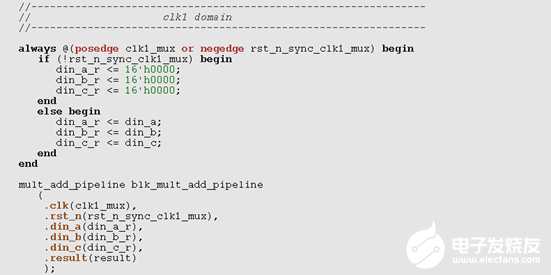

首先来看看最直接的实现方案。这里输入锁存后再运算,运算结果锁存后再输出。这样做屏蔽了input delay,output delay对运算逻辑timing的影响,可以更好地评测运算逻辑的速度。

这里也可以看到,手动插入pipeline stages很难,尤其是乘法运算。这是一个整体,无法手动切割。当然有朋友可能会说,例化Synopsys DesignWare里的multi-stage multiplier。那样当然也是可以的,优缺点你也知道了,这里就不赘述了。

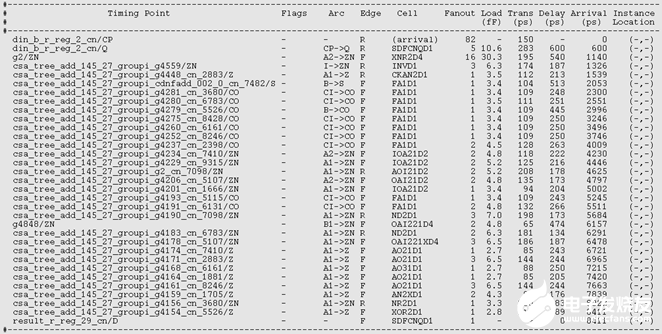

Genus综合后最差的路径如下。

时钟周期为9ns,positive slack 26ps,能满足。也就是说这个实现方案最多也就是只能跑110MHz左右。如果系统的要求是400MHz,这个最直白的实现方案显示是不行的。

下面再来看看使用Genus retime技术的实现方法。在这个实现中把multiply-add放到了一个独立的module中,这样做是为了在Genus综合中单独将这个module的retime打开。

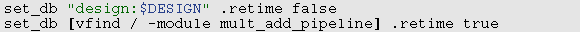

Genus综合时在syn_generic之前关闭整个设计地retime,打开multiply_add_pipeline模块地retime。

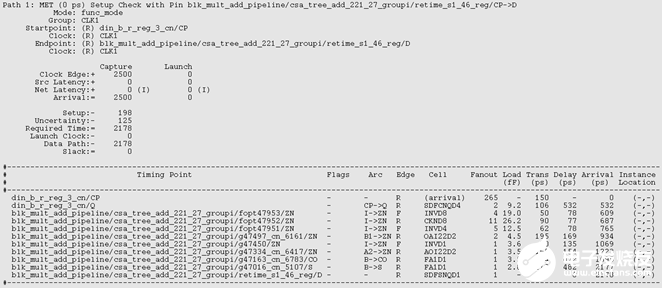

Genus综合结果如下。

可以看到,时钟提高到了2.5ns (400MHz),依然能满足,slack为0。

这里还要提一下,Genus retime的算法非常聪明。RTL里我们给了中间三级32*3=96个DFF,实际上最后Genus并没有全部用掉96个DFF,只用了2+9+31个DFF置换为retime中间级flop,其余的都优化掉了。可以说Genus retime真的很“省”。

总结一下,Genus retime技术通过移动pipeline flop的位置将复杂组合逻辑分割成几级,可以大大提高电路的速度。

审核编辑:黄飞

-

经典C语言接口与实现:创建可重用软件的技术2023-09-25 528

-

自动驾驶技术的实现2021-09-03 3213

-

逻辑电路的纠错技术是如何实现的?2021-06-18 1831

-

什么是多点触控技术?多点触控是怎么实现的?2021-06-17 1871

-

怎么实现基于RFID技术的离散MES设计?2021-06-07 1894

-

怎么利用蓝牙技术实现遥控打印?2021-05-28 1779

-

怎么实现基于CDMA技术的准确寻址?2021-05-27 1990

-

如何实现蓝牙技术的低功耗?2021-05-18 2319

-

怎么实现基于FPGA技术的智能导盲犬设计?2021-05-08 1842

-

RFID技术怎么实现药品管理?2019-09-20 2279

-

无线充电技术设备的实现无线充电技术设备的实现2017-09-15 1141

-

什么是红外对频技术,具体怎么实现的?2016-10-21 5260

-

PWM技术实现方法原理详解2010-01-10 195245

全部0条评论

快来发表一下你的评论吧 !