数字前端电路:简单的边沿检测电路分析

描述

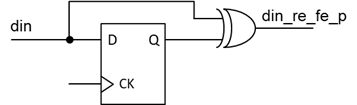

如何知道一个信号上升沿或下降沿是否到来?下面是一个简单的边沿检测电路。

这个电路的原理很简单。当din上升沿或下降沿到来时,din_re_fe_p产生一个脉冲。后续电路看到这个脉冲,就知道din上升沿或下降沿发生了。

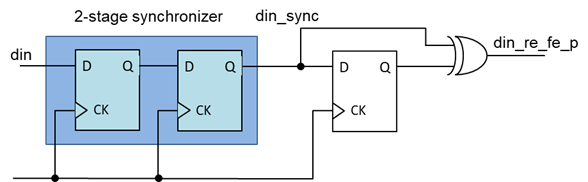

如果din是异步输入,前面要加一个两级同步器(其实就是两级DFF)。

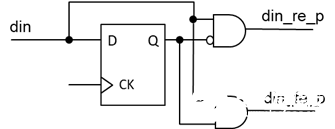

边沿检测可以演化出只检测上升沿,只检测下降沿。

边沿检测电路非常有用。

例1:作为跨时钟域同步握手信号

有一组信号data_bus,需要从clk_a同步到clk_b。如果每一个信号都经过两级同步器,那就太浪费资源了。而且有时一组信号要保证所有位传到clk_b时同时更新,就更不能用两级同步器了。两级同步器的latency在1到3个周期之间,有随机性,无法保证两个信号各自通过同步器后同时更新。

这个场景可以加一个简单的握手信号data_toggle。当clk_a这边信号变化时,data_toggle也改变状态(0->1或1->0)。data_toggle送到clk_b,经过两级同步+边沿检测产生data_toggle_re_fe_p,clk_b这边的逻辑看到data_toggle_re_fe_p脉冲后,就可以放心大胆地锁存data_bus。

喜欢low power的朋友可以把data_toggle_re_fe_p作为ICG的EN信号。RTL写得干净,工具也能自动infer ICG。

边沿检测输出作为ICG EN其实是非常有用的low power技巧之一。

当然,这个例子是很简单地握手方式。复杂一些的可以用request,acknowledge之类的双向握手。

clk_a送一个req=1到clk_b,告诉clk_b数据ready。

clk_b同步req并做上升沿检测。检测到req上升沿后锁存数据。

clk_b发一个ack=1给clk_a,告诉clk_a数据已经锁存。

clk_a同步ack并做上升沿检测。检测到ack上升沿后清除req=0,准备下一次传数据。

clk_b这边检测到req下降沿,清除ack=0,准备接受下一次数据。

审核编辑:黄飞

-

FPGA设计经验之边沿检测2012-03-01 5474

-

FPGA设计经验:边沿检测2017-08-16 2226

-

数字前端生存指南—RTL2023-12-04 12888

-

IC数字前端设计实战案例系列pdf2011-12-14 11316

-

寻找数字前端设计的讲师2012-06-07 1954

-

[招聘] 新思科技(Synopsys)上海/西安招聘数字前端AC2017-03-03 3058

-

fpga应用篇(二):边沿检测2017-04-06 4023

-

小白入门数字前端,求大神指教需要学什么知识以及用哪些软件2018-03-22 4653

-

如何去实现一种数字前端的设计?包括哪些步骤?2021-06-18 1501

-

数字IC前端和后端有何区别2021-07-28 5803

-

针对TD-SCDMA标准的数字前端解决方案2009-08-22 512

-

软件无线电中的数字前端2011-02-28 838

-

边沿检测的目的及电路原理分析2019-11-19 11955

-

FPGA学习-边沿检测技术2022-11-26 2932

-

Gvim工具在数字前端开发中扮演的角色和重要的意义2025-02-20 1193

全部0条评论

快来发表一下你的评论吧 !