针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(1)

描述

对于UltraScale/UltraScale+芯片,几乎FPGA内部所有组件都是可以部分可重配置的,这包括CLB中的查找表(LUT)、触发器(FF)、移位寄存器(采用LUT实现)、分布式RAM/ROM等,Block如BRAM、URAM、DSP、GT(高速收发器)、PCIe、CMAC、Interlaken MAC等,SYSMON(XADC和System Monitor),时钟单元如BUFG、MMCM和PLL等,I/O相关单元如ISERDES、OSERDES和IDELAYCTRL等。只有与配置相关组件必须在静态区,包括BSAN、CFG_IO_ACCESS、EFUSE_USR、ICAP、FRAME_ECC、MASTER_JTAG、STARTUP、和USR_ACCESS。

Pblock的大小

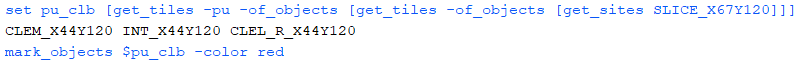

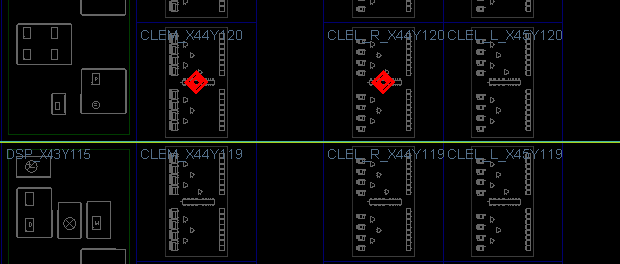

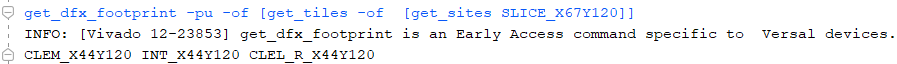

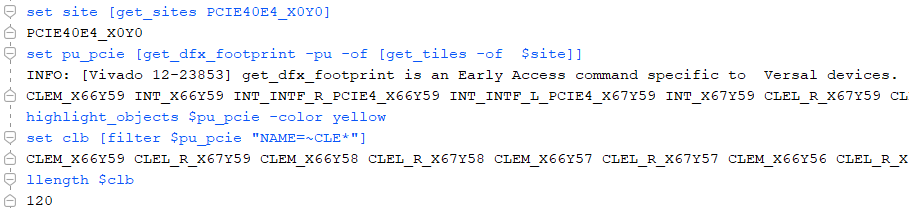

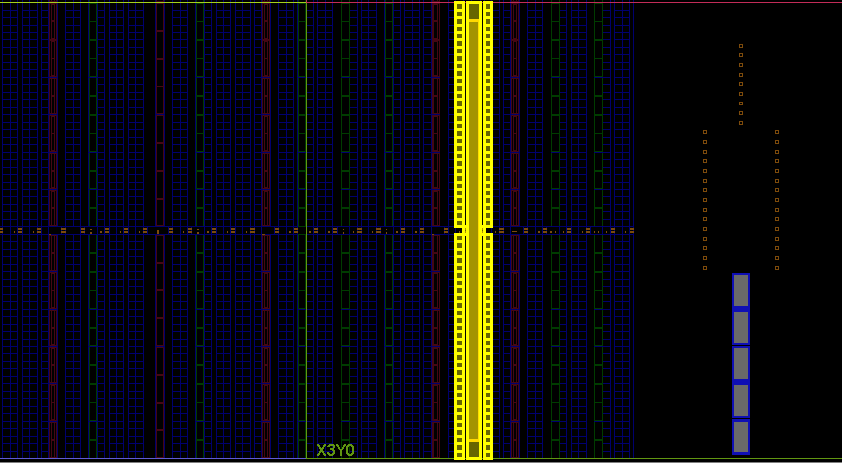

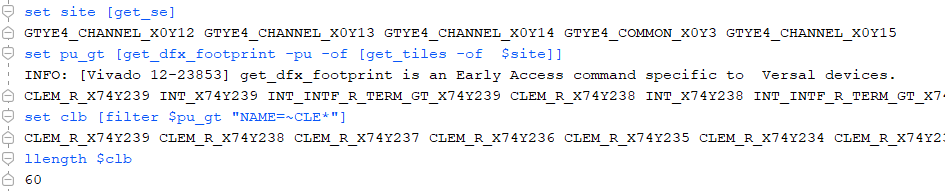

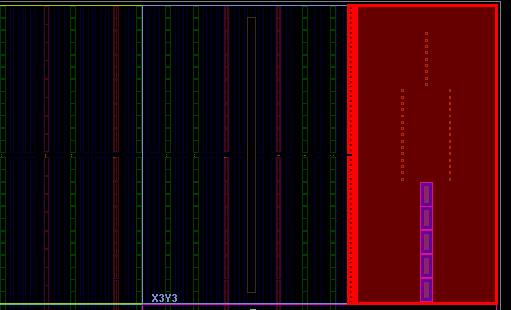

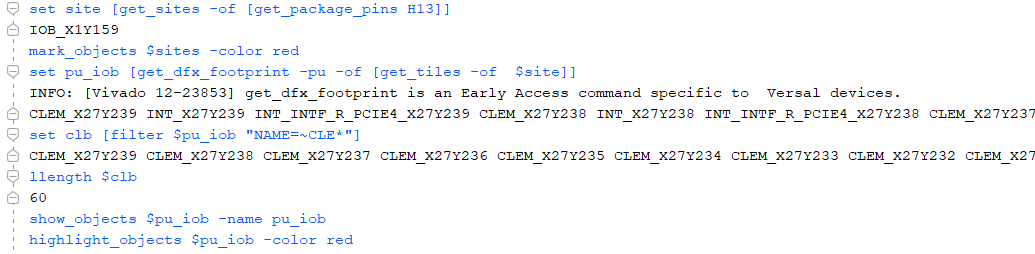

DFX设计中,动态区都有专属的Pblock。Pblock的最小范围是由PU(ProgrammableUnit)决定的,而一个PU的大小是跟资源类型紧密相关的。例如,对于SLICE,其PU为所属的CLB以及与之相邻的一个CLB,同时还包括这两个CLB共享的Interconnect,这可通过如下Tcl命令获取,注意最外层的Tcl命令get_tiles需要添加选项-pu。如果Vivado版本是2023.1或更高版本,可以使用命令get_dfx_footprint外加选项-pu实现同样功能。

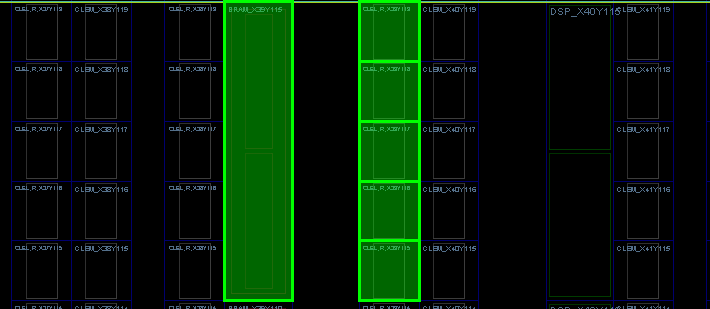

对于BRAM(36Kb),其PU包含自身之后还包含与之相邻的5个CLB以及共享的Interconnect,如下图所示。

对于PCIE,其PU包含自身之后还包含两侧各60个共120个CLB以及共享的Interconnect,如下图所示。

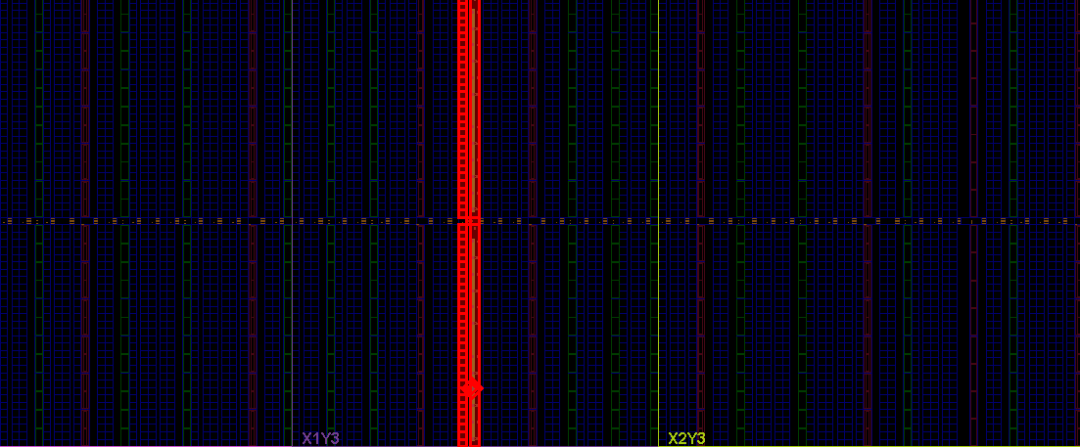

对于高速收发器,其PU包含自身之外还包含与之相邻的60个CLB以及共享的Interconnect,如下图所示。

对于PackagePin,其PU包含其所在IO Bank的所有资源,如下图所示,这也表明了同一个IO Bank内的管脚要么均在静态区,要么均在动态区。

在UltraScale/UltraScale+ FPGA中,Pblock不再需要设置属性RESET_AFTER_RECONFIG,但需要将属性SNAPPING_MODE设置为on。这样工具给了用户足够的灵活性去画Pblock,但为了保证Pblock不违反PU的要求,工具又会在已画Pblock的基础上自动调整,这正是SNAPPING_MODE的作用。

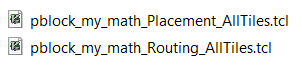

对于DFX工程,在执行完布局布线之后,会生成一个名为hd_visual的文件目录,在此文件夹下有两个Tcl文件,如下图所示,文件名为pblock__Placement/Routing_AllTiles.tcl。

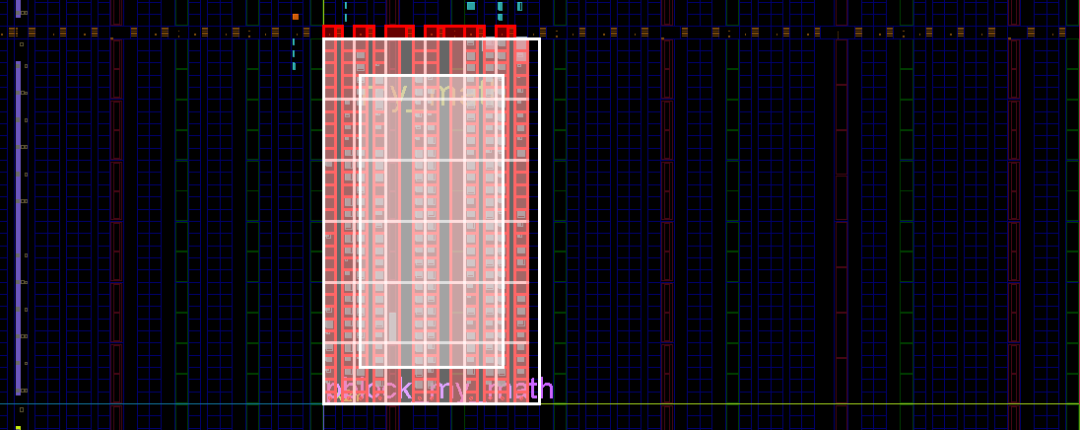

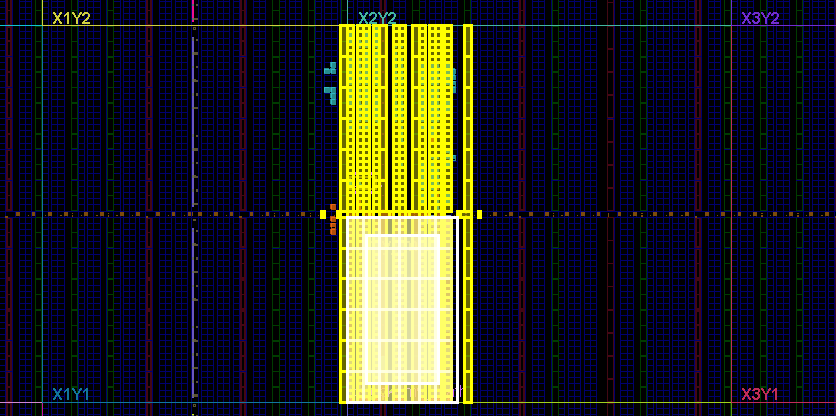

打开布线后的网表文件,执行source命令即可看到整个Pblock的实际布局范围和布线范围。图中白色高亮标记为原始Pblock范围,红色标记为实际Pblock的布局范围,黄色标记为实际Pblock的布线范围,包括了扩展的布线区域。对于Vivado2023.1及之后版本,可直接使用命令get_dfx_footprint实现同样功能。

sourcepblock_my_math_placement_AllTiles.tcl

对于UltraScale/UltraScale+ FPGA,动态区Pblock的高度可以不是以Clock Region对齐,这在上述案例中已有体现。换言之,上图中Pblock所在Clock Region的其他区域仍然可以供静态区使用,但不能供其他动态区使用。这意味着同一个ClockRegion只能拥有一个RP,所以可以看到“可重构”仍然是按照ClockRegion作为基础帧执行的。

扩展的布线区域

对于动态区的Pblock,其属性CONTAIN_ROUTING的值为TRUE,意味着动态区的布线也在划定的Pblock内。但实际上,最终的布线区域是可扩展的,不仅是已画好的Pblock,还包括Pblock之外的布线资源。从而,与RM输入/输出端口相连的网线就可能出现扩展的布线区域内(Pblock之外),但只要Partition Pin落在扩展区域内,就可以不用限定PartitionPin的位置。这里并不是说Pblock的形状不规范才导致布线区域扩展,即使是正规的矩形Pblock也可能会有扩展的布线区域。

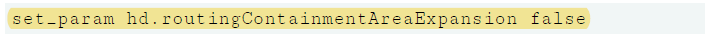

但一个事实是扩展的布线区域一定是以Clock Region为边界的。由于动态区布线区域的扩展,动态区对应的bit文件大小就会增大,但是如果动态区对应的bit文件大小比设计性能更为关键,可通过如下命令禁止动态区性能扩展。另外,7系列FPGA是不支持动态区布线区域扩展这一功能的。从Vivado2020.2开始,算法的改进促使动态区布线扩展区域更小同时这种更小的布线区域对布线性能影响也更小。

审核编辑:刘清

-

AMD推出全新Spartan UltraScale+ FPGA系列2024-03-18 1247

-

采用UltraScale/UltraScale+芯片的DFX设计注意事项2024-01-18 2178

-

针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)2023-12-21 2024

-

UltraScale和UltraScale+ FPGA封装和管脚用户指南2023-09-13 1064

-

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计2022-11-02 2559

-

UltraScale/UltraScale+的时钟资源2022-05-12 2674

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 4869

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 2793

-

UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法2020-11-04 9913

-

赛灵思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P2020-11-02 2756

-

Zynq UltraScale+ MPSoC的发售消息2018-11-27 4505

-

Xilinx 宣布Vivado设计套件开始支持16nm UltraScale+产品早期试用2017-02-09 681

-

闲话Zynq UltraScale+ MPSoC(连载1)2017-02-08 1070

全部0条评论

快来发表一下你的评论吧 !