一种使用fifo节约资源降低功耗的设计方法

电子说

1.4w人已加入

描述

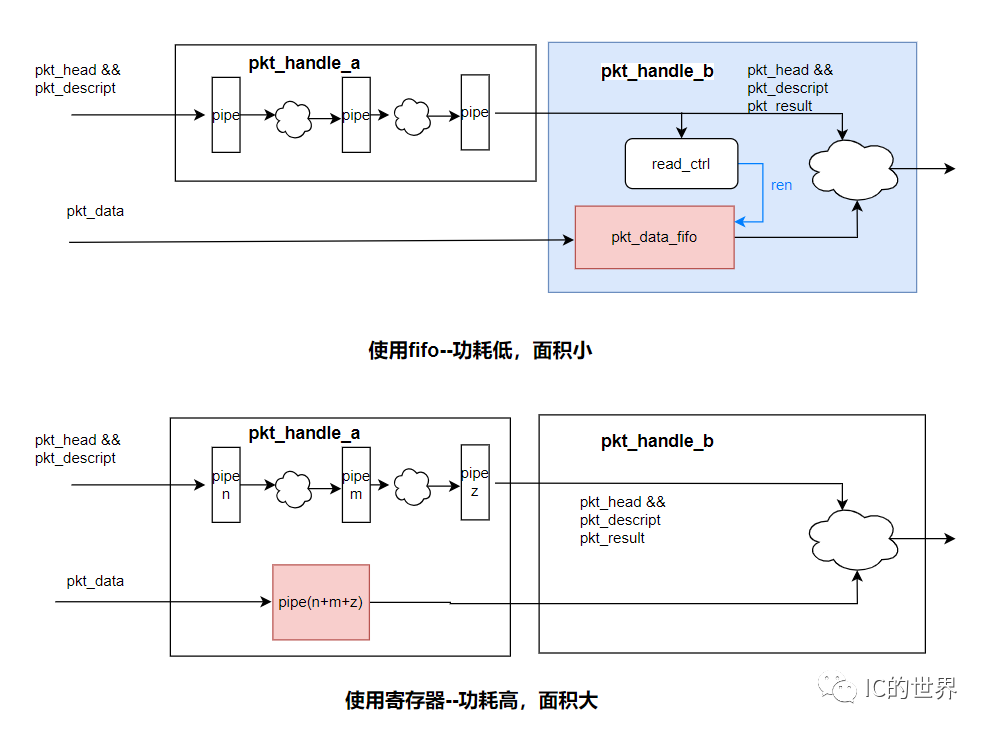

本案例中,我们讲解一种使用fifo节约资源,降低功耗的设计。如图所示,pkt_handle_a模块是对数据包进行处理的模块,但是不需要包数据(pkt_data),而仅仅需要根据包头(pkt_header)和包描述符(pkt_descript)。

这时候该怎么设计呢?

可以采用如下方式:在pkt_handle_b模块使用一个fifo用于存储包数据(pkt_data),pkt_handle_a模块的输入仅仅只有包头和包描述符,pkt_handle_a模块完成包处理后新增处包处理结果(pkt_result),送到pkt_handle_b模块,pkt_handle_b模块在需要读出包数据(pkt_data)的时候才将fifo内的数据读出。

在包数据位宽较大,pkt_handle_a流水拍数较大时,相对于使用寄存器对包数据(pkt_data)进行打拍,使用fifo存储包数据(pkt_data)的实现方式更有优势,功耗低,面积小。

虽然从存储bit位角度计算两种设计需要的bit位几乎相同,但是相对于寄存器,底层用ram实现的fifo面积更小,功耗更低。

pkt_handle_a和pkt_handle_b之间可能存在更多的模块,数据流水可能长达几十到上百个周期,因此流水拍数越大,节约面积,降低功耗的效果越明显。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

降低电路漏电功耗的低功耗设计方法2020-09-16 13206

-

FPGA低功耗设计小贴士2015-02-09 2997

-

IC芯片功耗有哪些降低方法?2017-06-29 2698

-

请问如何让音频功率降低功耗?2018-08-06 4334

-

如何降低FPGA设计的功耗?2019-08-15 2940

-

提高功率降低功耗的方法2021-02-26 1986

-

分享一种具有低功耗意识的FPGA设计方法2021-04-29 1234

-

如何让音频功率降低功耗?2023-11-29 6840

-

一种异步FIFO的设计方法2006-03-24 1958

-

一种低功耗触摸按键应用的设计方法2009-11-06 2626

-

一种低功耗智能传感主动式标签的设计2012-10-24 866

-

详细介绍一种显著降低LoRa节点功耗的方法2020-10-26 2511

-

一种单片机系统RAM的低功耗测试方法2021-06-24 955

-

一种低成本、低功耗的WiFi61812021-10-30 1343

-

如何降低设备功耗,降低采集设备功耗的几种方法2023-10-11 3023

全部0条评论

快来发表一下你的评论吧 !