详解内存条和内存颗粒

电子说

描述

内存条DIMM

在80286时代,内存颗粒(Chip)是直接插在主板上的,叫做DIP(Dual In-line Package)。到了80386时代,换成1片焊有内存颗粒的电路板,叫做SIMM(Single-Inline Memory Module)。由阵脚形态变化成电路板带来了很多好处:模块化,安装便利等等,由此DIY市场才有可能产生。当时SIMM的位宽是32bit,即一个周期读取4个字节,到了奔腾时,位宽变为64bit,即8个字节,于是SIMM就顺势变为DIMM(Double-Inline Memory Module)。这种形态一直延续至今,也是内存条的基本形态。

说到这里,小张着急了:”这和我的内存有啥关系?“。当然有关系,就是和10600S的S有关,现在DIMM分为很多种:

RDIMM: 全称(Registered DIMM),寄存型模组,主要用在服务器上,为了增加内存的容量和稳定性分有ECC和无ECC两种,但市场上几乎都是ECC的。

UDIMM:全称(Unbuffered DIMM),无缓冲型模组,这是我们平时所用到的标准台式电脑DIMM,分有ECC和无ECC两种,一般是无ECC的。

SO-DIMM:全称(Small Outline DIMM),小外型DIMM,笔记本电脑中所使用的DIMM,分ECC和无ECC两种。

Mini-DIMM:DDR2时代新出现的模组类型,它是Registered DIMM的缩小版本,用于刀片式服务器等对体积要求苛刻的高端领域。

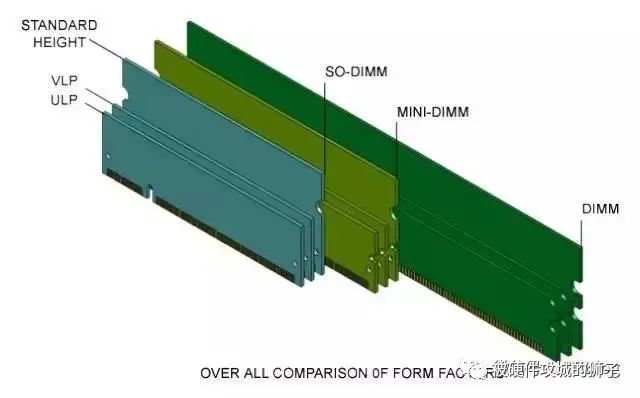

一般内存长度 133.35mm,SO-DIMM为了适应笔记本内狭小的空间,缩短为67.6mm而且一般为侧式插入。高度也有些变种,一般的内存条高度为30mm,VLP(Very Low Profile)降低为18.3mm,而ULP(Ultra Low Profile)更是矮化到17.8mm,主要是为了放入1U的刀片服务器中。

大小关系如下图:

小张这下知道10600S中S代表了SO-DIMM,看来大小没错。不过速度呢?

DDR到DDR4

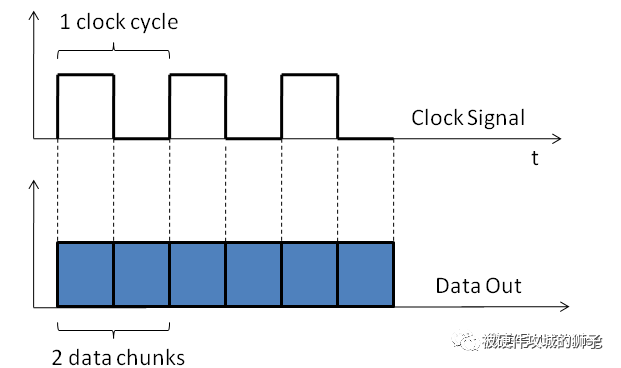

为了照顾小张的急性子,我就跳过了SDRAM后DDR和Rambus/RDRAM争天下的故事。DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”。DDR SDRAM在原有的SDRAM的基础上改进而来。也正因为如此,DDR能够凭借着转产成本优势来打败昔日的对手RDRAM,成为当今的主流。顾名思义,和原本的SDRAM相比,DDR SDRAM一个时钟周期要传输两次数据:

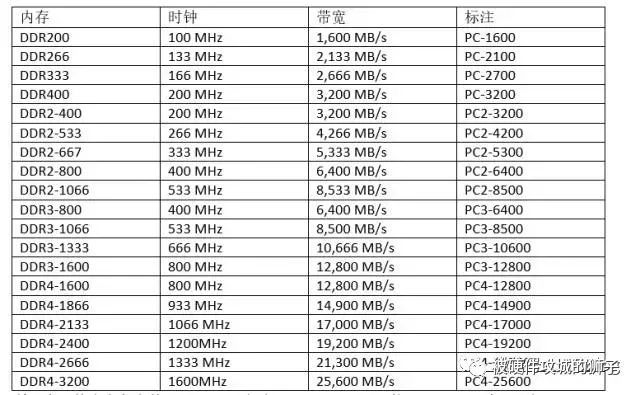

从DDR到DDR4主要的区别是在于传输速率的不同,随着时钟周期的不断降低,传输率也不断提高。还有电压也越来越低。有趣的是命名规则,大部分台式机DIMM厂商都会标注DDRx-yyy,x代表第几代,yyy代表数据传输率。而大部分的SO-DIMM和RDIMM等则标注PCx-zzzz,x还代表第几代,zzzz则代表最大带宽。因为DDR位宽为64位,8个字节,所以zzzz=yyy * 8,而yyy又是时钟的两倍。下面这张表是主要的各代DDR内存的速度:

所以小张的内存条上的PC3-10600S代表DDR3,1333MHz的SO-DIMM。小张又问,那2R*8啥意思呢?

RANK和BANK

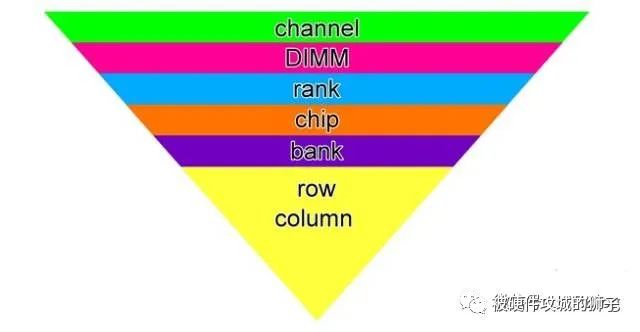

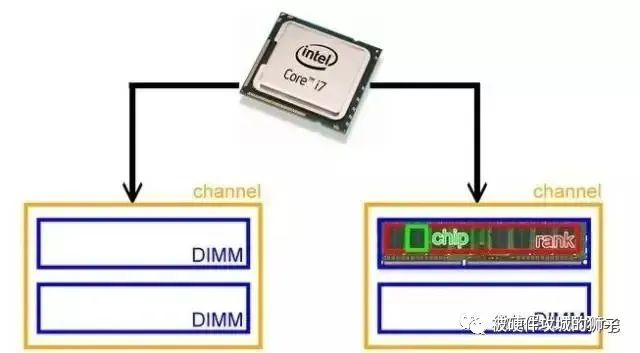

其实从外观上就可以看出来小张的内存条由很多海力士的内存颗粒组成。从内存控制器到内存颗粒内部逻辑,笼统上讲从大到小为:channel>DIMM>rank>chip>bank>row/column,如下图:

一个现实的例子是:

在这个例子中,一个i7 CPU支持两个Channel(双通道),每个Channel上可以插俩个DIMM,而每个DIMM由两个rank构成,8个chip组成一个rank。由于现在多数内存颗粒的位宽是8bit,而CPU带宽是64bit,所以经常是8个颗粒可以组成一个rank。所以小张的内存条2R X 8的意思是由2个rank组成,每个rank八个内存颗粒。由于整个内存是4GB,我们可以算出单个内存颗粒是256MB。

首先RDIMM 16GB 2R*8是什么意思

16GB代表总的容量是16GB,

2R代表一共有2Rank的总线宽度,不考虑ECC的时候,一个Rank是64位,

8代表一个Chip的位宽是X8,

总结:一个Rank包含8个X8的Chip,那么2R就说明一共16个Chip;假设每个Chip都是单die的,那么Chip的大小就是1GB的。

其次RDIMM 16GB 2R*4是什么意思

16GB代表总的容量是16GB

2R代表一共64*2的总线宽度

4代表Chip的位宽是X4,

总结:假设一个Chip中只有一个die那么Chip的数量就是2*64/4=32颗,每一颗的容量就是16GB/32=0.5GB,也就是4Gb;

再次RDIMM 32GB 2R*4是什么意思

32GB的容量

2*64的宽度

X4的位宽,

总结:颗粒=2*64/4=32颗,那么每一颗的容量就是1GB,也就是8Gb;

再次LRDIMM 64GB 4R*4 是什么意思

64GB的容量

4*64的宽度

X4的位宽,

总结代表颗粒是4*64/4=64颗,但是其实DIMM最大只能放32个Chip,每个Chip上有两个Die,每个Die是1GB;

最后3DS LRDIMM 64GB 4R*4是什么意思

64GB的容量

4*64的宽度

X4的位宽,Die一共是64颗,每颗1GB,一个Chip两个Die

问题来了3DS代表3维堆叠,如果一个Chip中可以放4个Die那么这个DIMM怎么命名呢

4个Die,一个Die1GB,一个Chip是4GB,那么32个Chip最大是128GB,一个die的位宽是X4的话,32Chip*4Die*X4位宽/64=8Rank,因此可以称为是3DS LRDIMM 128GB 8R*4或者3DS RDIMM 128GB 8R*4

最后一个问题RDIMM代表寄存器DIMM就是将地址和控制总线进行缓存的DIMM,这样信号更好一些,LRDIMM比前者更进一步,将数据总线也进行缓存,进一步提高可靠性。

内存颗粒chip

DDR4 协议标准中规定了几种 DRAM 颗粒的容量规格,这些规格包含哪些方面?本文将讨论这个话题。

DRAM 容量规格

DDR4 (下文可能混合使用 DDR4/DDR/DRAM, 皆为同义)颗粒在容量上有四种规格,分别为 2Gb、4Gb、8Gb 以及 16Gb。

DRAM 颗粒的容量 = 地址数量 x 位宽

每种颗粒容量规格,提供了 3 种地址数量和位宽的组合,以 2Gb 颗粒为例:

| 容量 (Gb) | 位宽 (b) | 选址数量 |

|---|---|---|

| 2 | 4 | 512M |

| 2 | 8 | 256M |

| 2 | 16 | 128M |

提供多种组合目的是为了提供灵活的配置方案。因为一个嵌入式系统的 DRAM 位宽一般为 32 或者 64 比特(在 PC 上有更大的位宽),需要拼接多片 DDR4 颗粒才能提供这么多比特,那么使用不同位宽的 DDR 颗粒就会有不同拼接方案。

以 32 比特位宽,嵌入式系统为例,使用不同位宽的 2Gb 颗粒,有以下几种组合:

| 系统位宽 (b) | 系统容量 (Gb) | 2Gb x4 颗粒数量 | 2Gb x8 颗粒数量 | 2Gb x16 颗粒数量 |

|---|---|---|---|---|

| 32 | 16 | 8 | ||

| 32 | 8 | 4 | ||

| 32 | 4 | 2 |

一般系统位宽的需求是固定的,而颗粒容量和位宽是一对可调整的参数,提供不同的系统容量,仍以 32 比特系统 DRAM 位宽为例:

|

2Gb 颗粒 |

4Gb 颗粒 | 8Gb 颗粒 | 16Gb 颗粒 | |||||

|---|---|---|---|---|---|---|---|---|

| 颗粒位宽 (b) | 系统容量(Gb) | 数量 | 系统容量 (Gb) | 数量 | 系统容量 (Gb) | 数量 | 系统容量 (Gb) | 数量 |

| x4 | 16 | 8 | 32 | 8 | 64 | 8 | 128 | 8 |

| x8 | 8 | 4 | 16 | 4 | 32 | 4 | 64 | 4 |

| x16 | 4 | 2 | 8 | 2 | 16 | 2 | 32 | 2 |

上表中的数量指的是系统的 DDR 颗粒总数量。有点与直观感觉违背的事实是,采用的位宽更大的颗粒,系统的总容量更低。

这是因为相同容量的颗粒,位宽越大,地址数量也就越少,所以系统位宽固定时,决定系统容量的是颗粒的地址数量:

系统容量 = 地址数量 x 系统位宽

接下来我们来看颗粒的地址数量以及其寻址方式。我们知道 DDR4 的寻址由 COL - ROW* - BANK- BANKGROUP 组成(单个 RANK 时)。

*COL, column, 指 DRAM 内部存储阵列中的列

**ROW, row , 指 DRAM 内部存储阵列中的行

颗粒的列数量是固定的 1024 列,而行、Bank(BA)、Bank Group (BG) 数量在不同位宽时则是不同的。

| 位宽 (b) | 选址数量(M) | 行数量 | 列数量 | BG 数量 | 每个 BG 中 BA 数量 |

|---|---|---|---|---|---|

| 4 | 512 | 32768 | 1024 | 4 | 4 |

| 8 | 256 | 16384 | 1024 | 4 | 4 |

| 16 | 128 | 16384 | 1024 | 2 | 4 |

地址所属的行、列、BA 以及 BG 的寻址是通过对应的地址线寻址得到,所以不同位宽的颗粒地址线的数目也不同。

| 位宽 (b) | 行地址线数目 | 列地址线数目 | BA 地址线数目 | BG 地址线数目 |

|---|---|---|---|---|

| 4 | 15 | 10 | 2 | 4 |

| 8 | 14 | 10 | 2 | 4 |

| 16 | 14 | 10 | 2 | 2 |

由于行列地址线是分时复用的,以 x4 位宽为例,行列共享 A0-A14 地址线中的 A0-A9,所以 x4 位宽总地址数量为 15 (A) + 2 (BA) + 2 (BG) = 19。

这里我们看到使用小位宽颗粒虽然能够拼接更多颗粒,提供更大的系统容量,但是所需要的地址线较 x8 和 x16 的颗粒也更多。这是更大系统容量的代价,或者说是系统容量与地址线数量的折中考量( trade-off)。

| 位宽 (b) | 总地址线数目 | 行地址线 | 列地址线 | BA 地址线 | BG 地址线 |

|---|---|---|---|---|---|

| 4 | 19 | A0-A14 | A0-A9 | BA0-BA1 | BG0-BG1 |

| 8 | 18 | A0-A13 | A0-A9 | BA0-BA1 | BG0-BG1 |

| 16 | 17 | A0-A13 | A0-A9 | BA0-BA1 | BG0 |

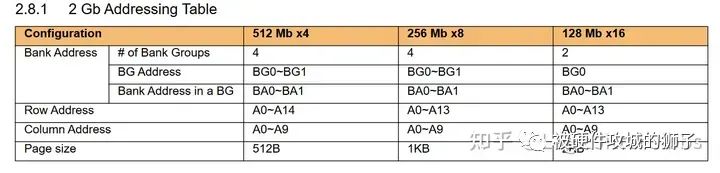

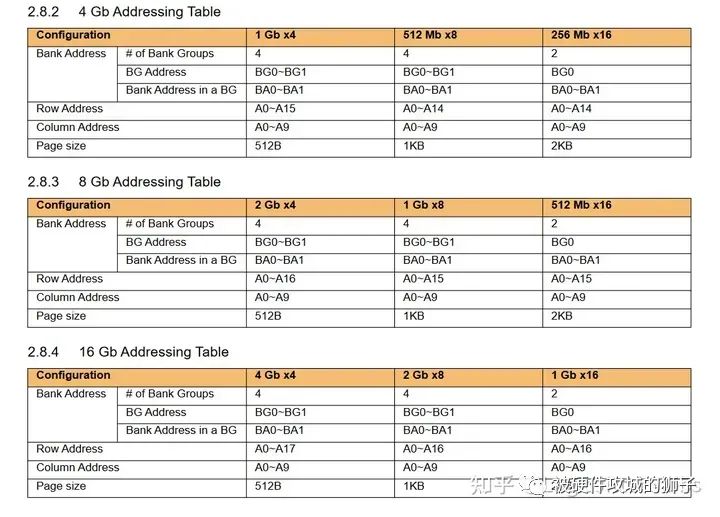

下面几张图都摘自 DDR4 协议 2.8 节,列出了 DDR4 支持的四种容量颗粒的属性,从中我们可以发现几点:

地址线最多的是 16Gb 容量的 x4 颗粒,使用 A0-A17 地址线。需要注意的是所有 PHY 都会有 A0-A16 (因为 RAS_n 复用为 A16),但有些 PHY 可能不支持 A17。

所有颗粒每个 Bank Group 都有 4 个 Bank

但是,x16 颗粒只支持 2 个 Bank Group,而其他颗粒支持 4 个

x4 颗粒的地址线最多,而 x8 和 x16 颗粒的地址线数目相同,比 x4 少 1。x8 和 x16 的选址数目差异体现在 x16 的 Bank Group 少一半

另外值得一提的是页大小(Page size),等于一行中的数据数量,直观来说页大小与位宽直接相关。

Page size = 位宽 x 列数量 = 位宽 x 1K

对于 x4 颗粒,页大小 = 4b x 1k = 4kb = 512B

顺序读取同页数据时,每次读取之间是基本无需等待的。而非同页数据之间,则需要按照协议要求,在两次读取之间增加延迟。举例而言, x16 颗粒上可以无延迟顺序读取 2KB 数据,但是如果是一个 x8 颗粒,则需要在读取完 1KB 数据后,关闭当前行并且打开下一行,才能读取后 1KB 数据,需要增加的延迟大约在几十个时钟周期量级。

最后,我们在前文中使用 4b x 512M 来描述一个 x4 颗粒,这是从颗粒位宽 x 地址数量的角度出发。协议中的称呼为 512Mb x 4,个人觉得两种称呼都可使用吧,笔者自己平时也没特别在意。

DDP 颗粒

最后讨论一种容量比较特别的颗粒,也是最近工作中遇到的。事情是这样的,客户提问说 SoC 能不能支持一种 4GB 的 DDR4 颗粒。阅读完本文的读者知道,DDR4 最大只有 16Gb(2GB)的颗粒,哪来的单颗 4GB 颗粒?

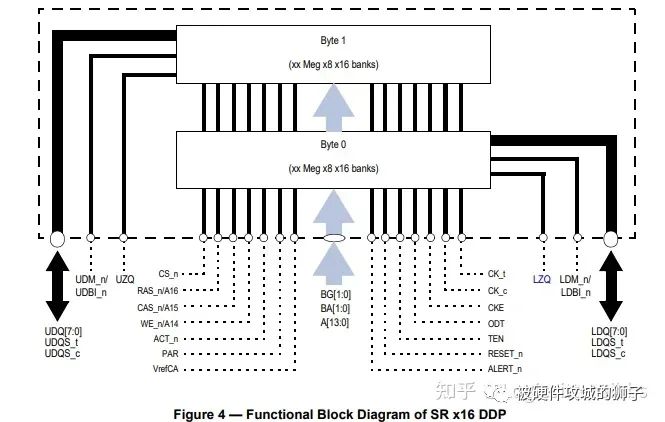

看了客户发来的颗粒 spec (是三星的颗粒)才知道,客户想使用的是一种特殊封装的颗粒,DDP(Dual Die Package),在协议的 2.9 节有简略的介绍。

DDP 颗粒顾名思义就是将两个 x8 Die 封装在一起,这样最大能够提供单颗 32Gb (2 x8 16Gb)的容量。

两个 Die 的连接方式如下图所示,它们的 CA 在封装内被堆叠(或者焊接)到一起,往封装外引出各自的 DQ 和 DQS 引脚。

协议中提到,除了具体产品手册的特殊注明外,DDP 颗粒的特性以及时序和普通的 x8 颗粒相同。

DDP 的好处是可以节省 PCB 的空间和布局布线时的难度,另外,因为两个 Die 之间的 CA 信号延迟会非常小,笔者觉得或许可以跳过两个 Die 之间的 write leveling 训练。

DDP 的劣势就显然易见,或许因为额外的封装成本,价格会相对更高,自然用户就会比较少,用户越少,价格也就越昂贵,供货越得不到保证,半导体行业典型的恶性循环就出现了。基于这些考虑,我们的客户后来也放弃了这个想法。

审核编辑:汤梓红

-

DDR内存条对比分析2011-12-29 4809

-

内存条颗粒哪个好?内存条颗粒排行!快来看看你的内存条颗粒排在哪里 #电脑 #电脑知识jf_49750429 2022-11-03

-

内存条芯片参数2008-10-19 4843

-

FPGA对DDRSDRAM内存条的控制2010-06-29 3119

-

DDR3内存条电路图2015-12-31 11820

-

内存条买单条跟双条的区别解析2018-06-11 39786

-

加内存条需要注意什么2018-12-08 133096

-

内存条的什么属性重要应该如何选择2019-12-01 7285

-

如何选择合适的内存条?内存条的什么属性最重要2020-04-12 9065

-

内存条坏了会出现什么状况_内存条坏了如何解决2020-06-01 13580

-

内存条故障原因及解决2020-06-09 10410

-

内存条起着什么样的作用2020-06-17 5787

-

单面与双面的内存条有什么区别2020-06-19 20654

-

DDR内存条的设计.zip2022-12-30 786

-

服务器内存条和普通内存条的区别2024-02-19 13534

全部0条评论

快来发表一下你的评论吧 !