IGBT模块银烧结工艺引线键合工艺研究

描述

欢迎了解

张浩亮 方杰 徐凝华

(株洲中车时代半导体有限公司 新型功率半导体器件国家重点实验室)

摘要:

主要研究了应用于 IGBT 模块封装中的银烧结工艺和铜引线键合工艺,依据系列质量表征和评价方法,分别验证并优化了银烧结和铜引线键合的工艺参数,分析了衬板镀层对烧结层和铜线键合界面强度的影响,最后对试制的模块进行浪涌能力和功率循环寿命测试。结果显示 , 与普通模块相比 , 搭载银烧结和铜线键合技术的模块浪涌能力和功率循环寿命均有大幅的提升,并且银烧结和铜线键合界面未见明显的退化。

0 引言

在汽车和新能源器件等领域,功率器件模块的工作温度和功率密度的提高,对模块封装互连可靠性要求也更高。随着芯片能力的提升,硅器件的工作结温可能达到 175 ℃。传统的芯片连接工艺为焊料焊接,常用的 SnAgCu 系和 SnSb 系焊料难以在更高的工作温度下保证模块的可靠性;其次,芯片正面的铝线键合点也一直是模块长期可靠性的短板,模块在承受周期性的应力时,铝线键合点会出现疲劳退化。无铅焊料的熔点较低(210~240 ℃),无法使用常规的 PI 胶涂覆进行键合点强化。因此,既要保证模块能够在高温下稳定运行,又需要能够在循环的“热 - 机械”应力下保证高可靠性,需要开发能够替代传统焊接和铝线键合点的互连工艺。

银烧结材料具有更高的热导率、电导率、机械强度和接近纯银的熔点,银烧结工艺迅速成为最具应用前景的互连技术之一。铜引线键合点是一种替代铝线键合点的很好的解决方案,除提供更高的键合强度外,相比铝线,铜线还具有更强的通流能力。但其在工艺实现方面还存在相当的难度,因为铜线材质较硬,芯片正面必须做很厚的铜金属才能兼容铜线键合,这又导致了金属化后薄片晶圆的翘曲,带来了新的工艺难题。

本文讨论了一种结合银烧结和铜引线键合技术的高可靠性互连技术,被称为 DTS(Die Top System)技术。文献研究表明,该互连技术可以显著提升模块的功率循环能力。

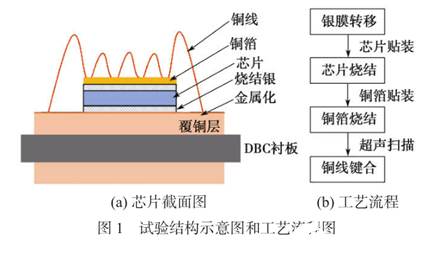

1 试验结构与工艺流程

试验结构如图 1(a) 所示,在芯片与衬板之间使用银烧结工艺实现互连,在芯片正面烧结一片铜箔作为缓冲层,并在铜箔上进行铜线键合。因为芯片需要进行双面烧结,因此正面也需要进行金属化处理。基本的工艺流程如图 1(b) 所示,首先将银膜转移至芯片背面,然后进行“芯片 - 衬板”烧结,最后在铜箔上实现铜线键合。

2 试验与分析

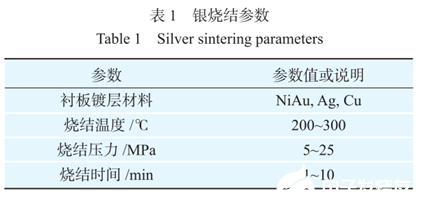

对大面积硅基芯片的烧结工艺进行研究,芯片尺寸为 12.2 mm×12.2 mm,金属化条件为双面镀 Ni/Au。将芯片烧结到覆铜陶瓷基板(Direct Bonding Copper,DBC)衬板上,衬板的表面金属化条件分别为镀化学镍金(Electroless Nickel/Immersion Gold,ENIG), Ag, Cu。根据银烧结的工艺特点,通常可以分为有压烧结和无压烧结;根据所使用烧结材料的粒径,也会将银膏分为微米银、纳米银、微纳米混合材料和其他添加成分银膏。本文中采用纳米银有压烧结工艺,烧结工艺验证的项点主要包括烧结温度、压力和时间,参数如表 1 所示。

为了观察烧结界面的结合情况,使用超声波扫描对烧结界面进行分析,然后观察界面的微观形貌,并分析烧结层孔隙。将样品切割,并使用环氧镶样后研磨抛光,使用光学显微镜和扫描电镜(SEM)观察试样横截面的微观组织,利用能谱仪 (EDS)分析界面扩散层的成分组成,最后处理图像并分析烧结层的孔隙分布。

使用直径为0.375 mm的铜线进行键合工艺的研究,包括键合压力、超声能量和键合时间等主要工艺参数的研究。铜线键合工艺参数曲线主要包括 3 个阶段,分别为初始接触、参数上升和水平保持阶段。对不同阶段的铜线键合工艺参数进行了分析,推力测试作为评估指标之一,用于表征键合点的剪切强度,然后制备样品,并使用 SEM 观察键合界面,评估结合情况;最后在ΔT=100 ℃的条件下进行了模块级的功率循环测试,同时常规封装模块作为对比对象同步进行了试验;在模块失效之后,对其测试寿命进行对比,并分析银烧结和铜线键合界面相比试验前的退化情况。

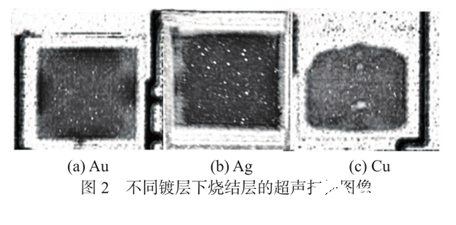

2.1 银烧结工艺验证和优化

在相同的烧结条件下,不同镀层衬板上的烧结层的超声扫描图像如图 2 所示。从图 2 可以看出,在镀Au 和镀 Ag 的界面上,超声扫描结果相似,烧结界面没有出现分层和空洞,但在烧结过程中,裸铜衬板边缘铜层在高温下会发生氧化,氧化层阻碍了烧结银颗粒与覆铜层之间的扩散,界面出现分层,图像中显示芯片边缘的烧结不良。

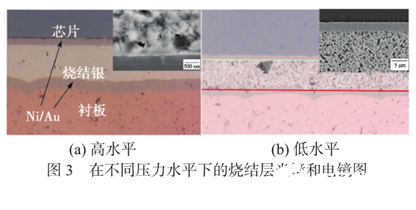

在衬板镀 NiAu 和镀 Ag 金属化的条件下,银烧结工艺对气氛条件的要求更低。在不同的压力水平下,从金相截面的光镜和 SEM 图像中可以看到,芯片的孔隙率会明显不同(如图3 所示)。在更高的压力水平下,烧结层内部的孔隙有效下降,从光镜图像中无法观察到明显的孔隙,在合适的工艺参数下,可以看到烧结银与衬板镀层原子互相扩散后,边界已难以观察到。

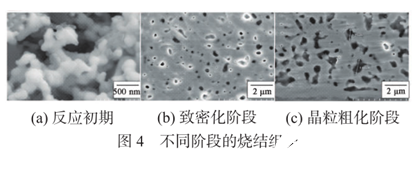

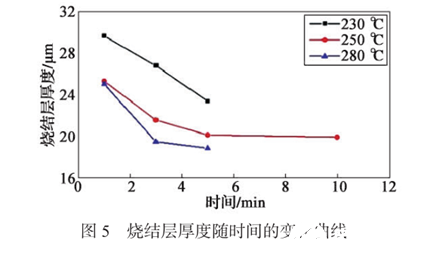

在烧结过程中,烧结温度和烧结压力是最重要的反应驱动力,烧结时间则是保证反应发生完全。烧结反应发生的主要驱动力为总表面能的降低,实现这一结果主要有 2 个反应方向,分别为致密化和晶粒粗化。在烧结反应的前期,原子扩散和晶界扩散是主要的反应机制,此刻表现为银颗粒的合并、烧结颈的出现和生长,如图 4(a) 所示。在反应中期和后期,体扩散和晶粒粗化成为反应的主导机制,此时主要表现为晶粒的持续生长与合并,烧结孔隙的数量逐渐减少。如图4(b)所示,在致密化主导的组织中,孔隙较多,尺寸较小;当晶粒粗化主导反应时,转变为图 4(c) 所示的形貌,孔隙尺寸较大,晶粒合并生长。在相同的压力条件下,不同的时间和温度下烧结层厚度随时间变化的趋势如图 5 所示。从图 5 可以看出,随着烧结温度的升高,烧结层的致密化速率增加,在 250 ℃的条件下,5 min 的烧结时间之后,烧结层致密化速度快速下降。

2.2 铜线键合工艺

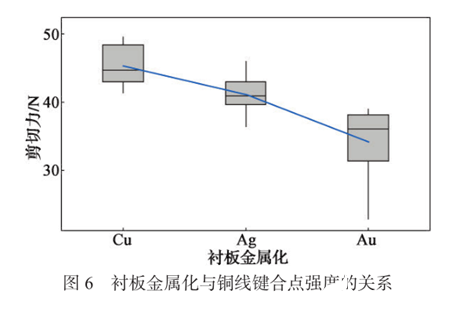

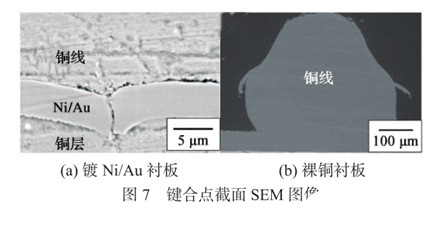

相比铝线键合,铜线的硬度更高,键合工艺需要更大的压力和能量,对镀层和基材也都有一定的要求。尽管芯片正面已烧结缓冲铜层,但“铜层 + 烧结层”的总厚度相比铜线的直径依然较薄,因此过高的键合参数依然会使芯片遭到损坏而失效。在相同的工艺参数下使用不同镀层的衬板进行铜线键合对比,使用剪切强度作为表征指标,如图 6 所示。镀银衬板的铜线键合强度略低于裸铜衬板,因为镀银层的厚度较薄,铜线可以破坏镀层与基材的覆铜,直接形成连接,但此过程依然会消耗部分超声能量,而在镀 NiAu 衬板上的键合点推力强度收敛性较差,强度为 20~40 N,相比裸铜衬板键合下降较多,这主要是由于在铜线键合工艺下 Cu 与 Ni 原子难以形成固溶强化,界面结合情况较差。如图 7 所示,在 Ni/Au 镀层界面,并没有形成良好的扩散连接,而且连续镀层在键合过程中发生了断裂,界面连接的不稳定性导致键合强度大幅波动;在裸铜表面键合的铜线属于同质金属结合,界面扩散良好,没有发现分层和裂纹的存在。

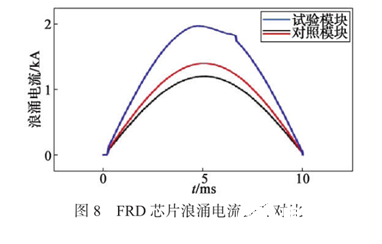

2.3 对芯片极限能力的提升

FRD 芯片的浪涌能力对比如图 8 所示。芯片正面烧结铜片和键合铜线后,FRD 的浪涌能力获得显著的改善,相比于常规“焊接 + 铝线”键合模块,试制模块芯片浪涌能力获得大幅提升。由于芯片正面增加了烧结层和缓冲垫片,电流被有效均化,当芯片电流达到浪涌极限时,正面烧结层和铜线键合点均未出现破坏。与常规模块相比,试制模块浪涌失效的主要破坏模式从常见的芯片发射极炸毁转变为场环终止区失效。

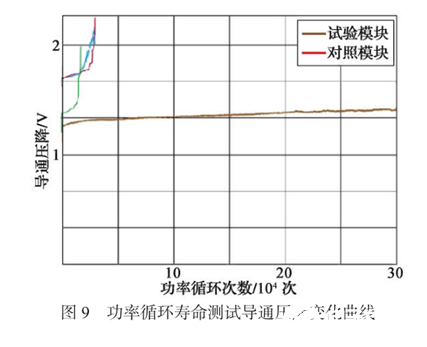

2.4 对模块的功率循环寿命能力的提升

功率循环寿命测试导通压降变化曲线如图9所示,功率循环寿命测试的条件为ΔT=100 ℃。从图 9 可以看出,试验样品循环寿命获得了数倍的提高。常规模块的失效模式为芯片正面铝线键合点脱附,从而导致模块互连失效,而试验模块在长时间的功率循环测试后,芯片并未出现电性能失效。

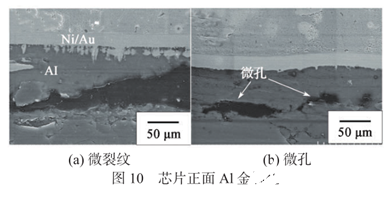

对失效模块进行分析,尽管铜线键合点的强度出现了一定的退化,但仍在允许的范围内,而位于芯片边缘的铝金属化由于承受较大的循环应力,呈现退化迹象。在互连界面中,芯片正面的铝金属化层内出现了微裂纹萌生的迹象,内部出现韧窝和微孔,如图 10所示。从图 10 可以看出,烧结界面结合良好,并无明显的裂纹和分层出现。因此,在承受循环应力时,芯片本身正面的金属化层可能成为潜在的失效风险点,可能逐渐发展成贯穿裂纹,导致器件的最终失效。

3 结语

在烧结工艺中,随着烧结时间的增加,在不同的温度下,烧结层厚度逐渐降低,随温度升高,烧结组织收缩的速度逐渐加快,同时增加压力可以有效地降低烧结组织空隙率。在银烧结工艺中,衬板镀 Au 和镀Ag 界面的烧结效果相似,均优于裸铜衬板。衬板的基材和镀层条件对铜线键合工艺均有一定影响。裸铜衬板由于和铜线属于同质金属结合,因此强度更高,相比之下,Ni/Au 镀层的键合界面存在裂纹,强度稳定性较差。

综合来讲,与常规封装模块相比,芯片双面银烧结和铜线键合技术可以明显提高模块的疲劳寿命,但该技术较高的材料成本和额外的工艺过程也导致其应用存在一定的限制,预计在碳化硅系列的宽禁带功率器件中将具有较好的应用前景。

审核编辑 黄宇

-

什么是引线键合?芯片引线键合保护胶用什么比较好?2025-06-06 1541

-

引线键合的基础知识2025-01-02 3366

-

有偿求助本科毕业设计指导|引线键合|封装工艺2024-03-10 10248

-

金丝引线键合的影响因素探究2024-02-02 2132

-

烧结银原理、银烧结工艺流程和烧结银膏应用2024-01-31 5840

-

IGBT模块银烧结工艺大揭秘,成本降低与性能提升双赢策略2024-01-06 3162

-

优化关键工艺参数提升功率器件引线键合的可靠性2023-12-25 3970

-

什么是引线键合?引线键合的演变2023-10-24 3996

-

引线键合工艺流程讲解2023-04-07 11565

-

LED引线键合工艺评价2021-11-21 2666

-

LED引线键合的检测内容与工艺评价2017-10-23 1605

-

大功率IGBT模块封装中的超声引线键合技术2011-10-26 1918

-

半导体引线键合清洗工艺方案2010-04-22 19462

全部0条评论

快来发表一下你的评论吧 !