Vitis 统一软件平台文档

描述

AMD Vitis 软件平台是一款开发环境,主要用于开发包括 FPGA 架构、Arm 处理器子系统和 AI 引擎在内的设计。Vitis 工具与 AMD Vivado ML 设计套件相结合,可为设计开发提供更高层次的抽象。

本用户指南涵盖了 Vitis 入门、使用 Vitis Unified IDE、Bootgen 工具、Vitis Python CLI、软件命令行工具、GNU 编译器工具、嵌入式设计教程以及驱动程序和库。如果您希望获取完整版文档,请至文末扫描二维码进行下载。

Vitis 软件平台包括以下工具

-

Vitis Embedded - 用于开发在嵌入式 Arm 处理器上运行的 C/C++ 应用代码

-

编译器和仿真器 - 用于使用 AI 引擎阵列执行设计

-

Vitis HLS - 用于开发基于 C/C++ 的 IP 块,该 IP 块主要针对 FPGA 架构

-

Vitis Model Composer 是一种基于模型的设计工具,可在 MathWorks Simulink 环境中进行快速设计探索

-

一系列性能优化的开源库函数,如 DSP、视觉、求解器、超声和 BLAS 等,其可采用 FPGA 架构执行,也可使用 AI 引擎执行

工具与库

Vitis 嵌入式

Vitis Embedded 是一个独立的嵌入式软件开发包,主要用于开发运行在嵌入式 Arm 处理器上的主机应用。

Vitis AIE DSP 设计工具

编译器和仿真器

AMD Versal 自适应 SoC 器件具有 AI 引擎阵列,有助于采用资源和电源都优化的方式实现高性能 DSP 功能。将 AI 引擎与 FPGA 架构资源一起使用,有助于非常高效地实现高性能 DSP 应用。

Vitis HLS

Vitis HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。

Vitis HLS 工具与 Vivado ML 设计套件(用于综合、布置和路由)及 Vitis 统一软件平台(用于异构系统设计和应用)高度整合。

Vitis Model Composer

Vitis Model Composer 是一款基于模型的设计工具,可在 MathWorks Simulink 环境中实现快速的设计探索。

此外,该工具还允许您使用一系列 AI 引擎和可编程逻辑 (HDL/HLS) 块对设计进行建模和仿真。

Vitis 库

性能优化的开源库,提供开箱即用的加速,对于采用 C、C++ 编写的现有应用而言,代码修改极少,甚至不需要修改代码。

按原样利用特定领域的加速库,通过修改适应您的需求,或者在您的自定义加速器中用作算法构建块。

设计流程

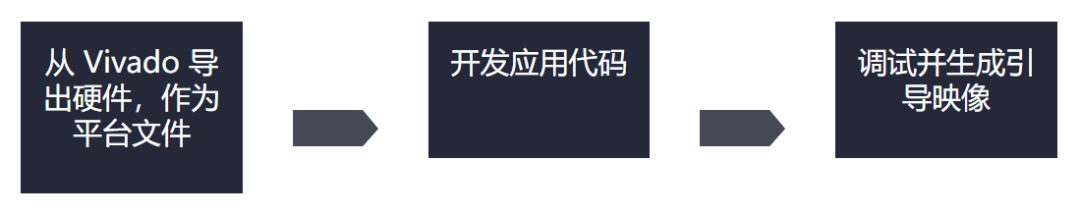

Vitis 嵌入式软件开发流程

在 AMD 自适应 SoC 中为 Arm 嵌入式处理器子系统开发 C/C++ 代码的设计人员通常会使用该流程。

-

硬件工程师不仅可设计可编程逻辑,而且还可使用 AMD Vivado ML 设计套件将硬件按 XSA 文件导出。

-

软件工程师可将这些硬件设计信息整合到他们的目标平台中,并可使用 Vitis 嵌入式软件开发应用代码。

开发人员可在 Vitis 嵌入式软件中执行所有系统级验证,并通过生成引导映像来启动应用。

2023.2 版本新特性

-

AIE-DSP 设计的新特性:AIE 仿真器和编译器增强

-

全新独立 Vitis 嵌入式安装程序:面向为 PS 子系统编写嵌入式 C 代码的设计人员

-

最新 Vitis 统一 IDE (GUI):从 2023.2 版开始,Vitis 将在所有 Vitis 工具中提供一个全新的通用 GUI。

-

配置文件、调试与跟踪的新特性 — 面向 AMD Versal AIE 器件系列

+

获取完整版

《Vitis 统一软件平台文档》

请扫描二维码进行下载

原文标题:Vitis 统一软件平台文档

文章出处:【微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

-

全新AMD Vitis统一软件平台2025.2版本发布2025-12-12 945

-

全新AMD Vitis统一软件平台2025.1版本发布2025-06-24 2010

-

全新AMD Vitis统一软件平台2024.2版本发布2024-12-11 1875

-

Vitis统一软件平台文档:嵌入式软件开发2023-09-15 754

-

Vitis统一软件平台用户指南:系统性能分析(v2020.1)2023-09-13 712

-

Vitis 统一软件平台文档:应用加速开发2023-07-19 1785

-

在赛灵思FPGA SoC平台上使用VITIS AI加速人工智能应用2022-11-22 3585

-

Vitis软件平台、vitis实例、裸机SOC(SDK)程序移植教程2022-07-25 19431

-

Vitis软件平台、vitis实例、裸机SOC(SDK)程序移植2021-01-31 2477

-

Vitis 统一软件平台简介 可实现最高的AI推断性能2020-11-24 4667

-

Vitis里如何创建嵌入式软件工程2020-11-04 6956

-

Xilinx首次推出软件和硬件设计统一的开发工具平台2020-08-17 1641

-

赛灵思SDK工程移植到Vitis的详细步骤2020-03-08 10511

-

Xilinx Vitis统一软件平台面向所有开发者解锁全新设计体验2019-10-10 3477

全部0条评论

快来发表一下你的评论吧 !