PCIe串行总线发展历史及工作原理

接口/总线/驱动

描述

PCIe是一种高速串行计算机扩展总线标准,自2003年推出以来,已经成为服务器(Server)和PC上的重要接口。今天为大家简单介绍一下PCIe的发展历史以及它的工作原理。

一、PCIe的由来

PCIe接口的全称是Peripheral Component Interconnect Express,原来的名字是“3GIO”,由Intel在2001年提出。PCIe的前身是PCI,PCI 使用的是并行传输方式,有较多的限制,并使用数据包(Packet)进行数据传输,数据报文在发送和接收过程中需要经过事务层、数据链路层和物理层多个层次。

PCIe串行总线标准被推出时,旨在替代旧的PCI、PCI-X和AGP总线标准,以实现更高的数据速率并简化系统设计。在交由PCI-SIG(PCI特殊兴趣组织)认证发布后改名为“PCI-Express”,简称“PCI-e”。此后,随着时间的推移PCIe不断改进以适应现代计算机的最新带宽需求。

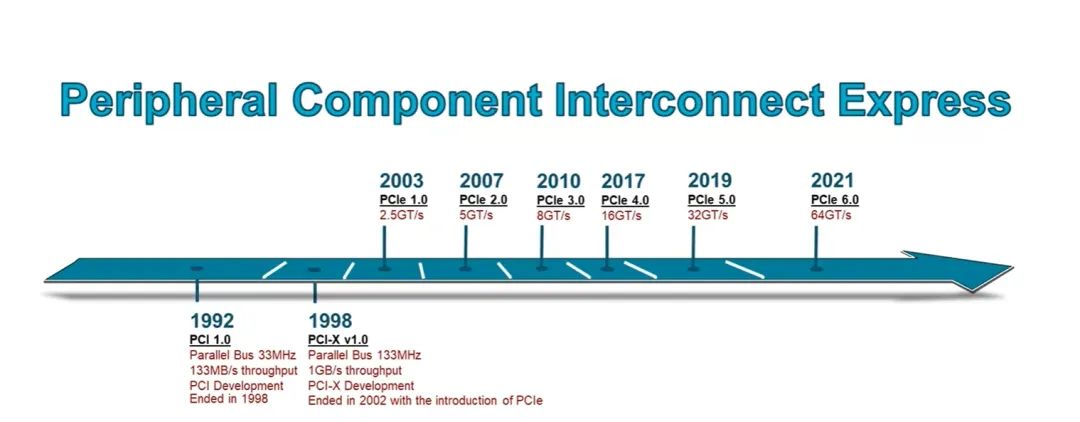

图1

2021年,PCIe 6.0 规范发布。每通道数据传输速率从PCIe 5.0的32 GT/s翻番至64 GT/s,PCIe 6.0*16通道的带宽高达256 GB/s,除了带宽和效率的提升外,PCIe 6.0还具有更低的延迟,是PCIe技术的又一大飞跃。

二、PCIe链路的常见设备

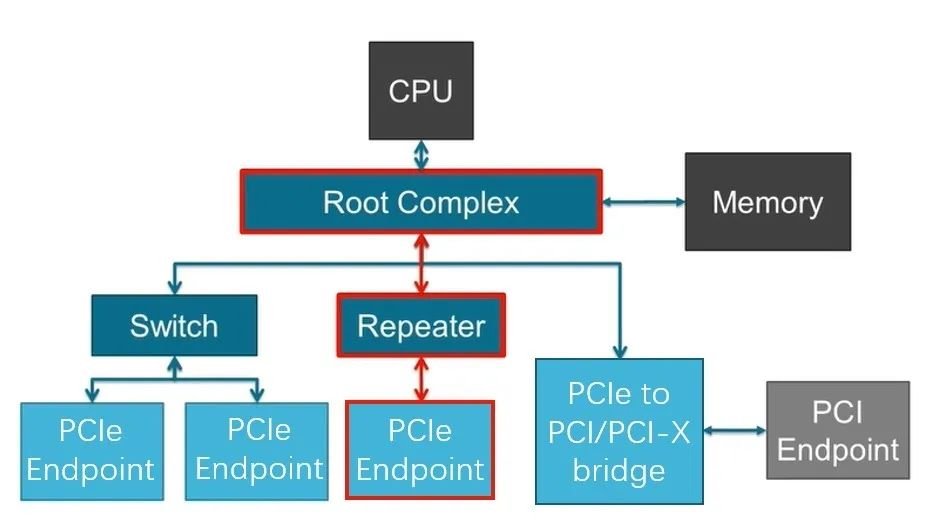

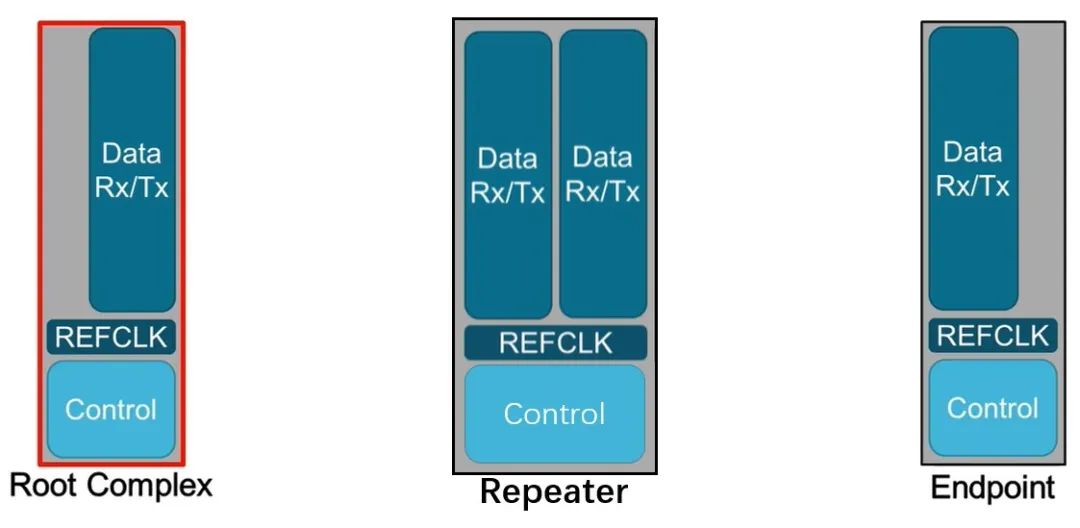

PCIe采用的是树型拓扑结构, 一般由根复合体(Root Complex),中继器(Repeater),终端设备(Endpoint)等类型的PCIe设备组成。

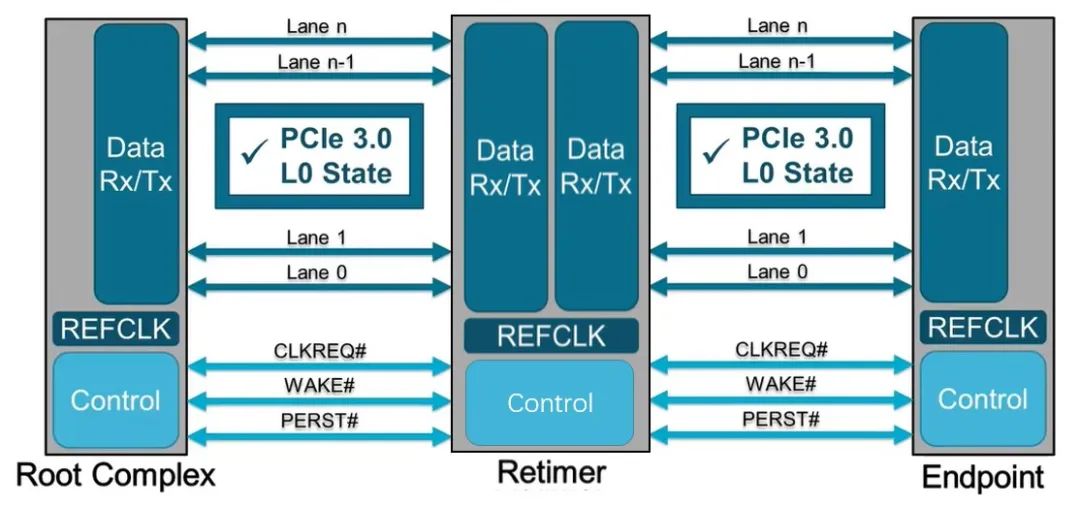

接下来将讲述PCIe如何通过下图突出显示的典型链路进行初始化和传输。

图2

Root Complex: 根复合体是CPU和PCIe总线连接的接口。主要负责存储器域到PCIe总线域的地址转换,随着虚拟化技术的引入,根复合体的功能也越来越复杂。根复合体把来自CPU的request转化成PCIe的4类request(configuration、memory、I/O、message)并发送给下面的设备。

Repeater:中继器是一种信号调节装置,可分为两类:Retimers和Redriver,两者都是常用的PCIe组件,Retimer通过内部时钟重构信号,再恢复后发送出去;Redriver则是通过信号均衡化和预加强等技术,重新加强再发送出去。在图示中,我们将使用PCIe 4.0兼容的Retimers举例。

PCIe Endponit: PCIe终端设备,是PCIe树型结构的末端节点。比如SSD,网卡、GFX卡等等。

图3

三、PCIe链路初始化

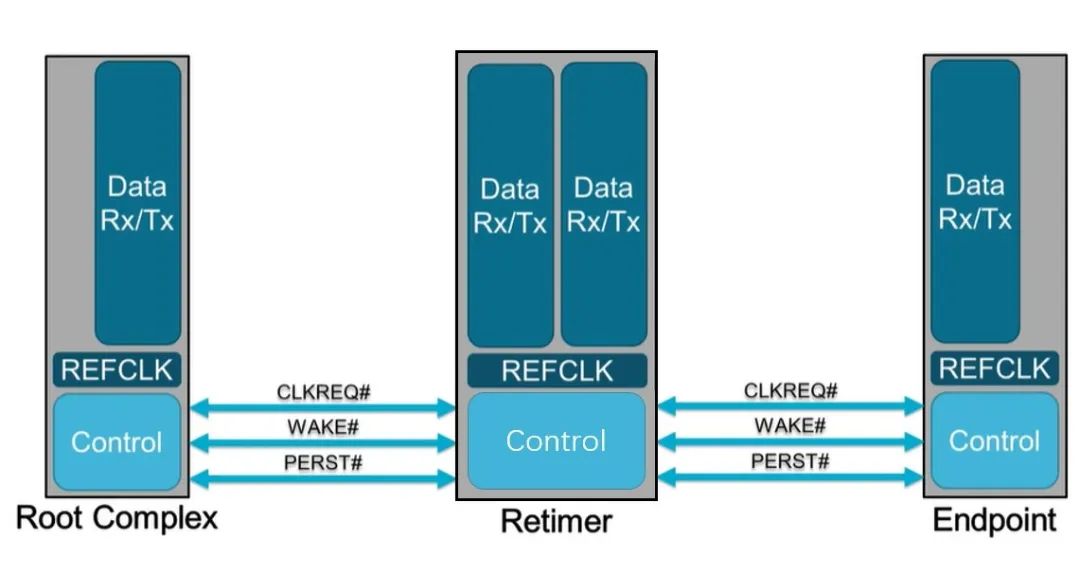

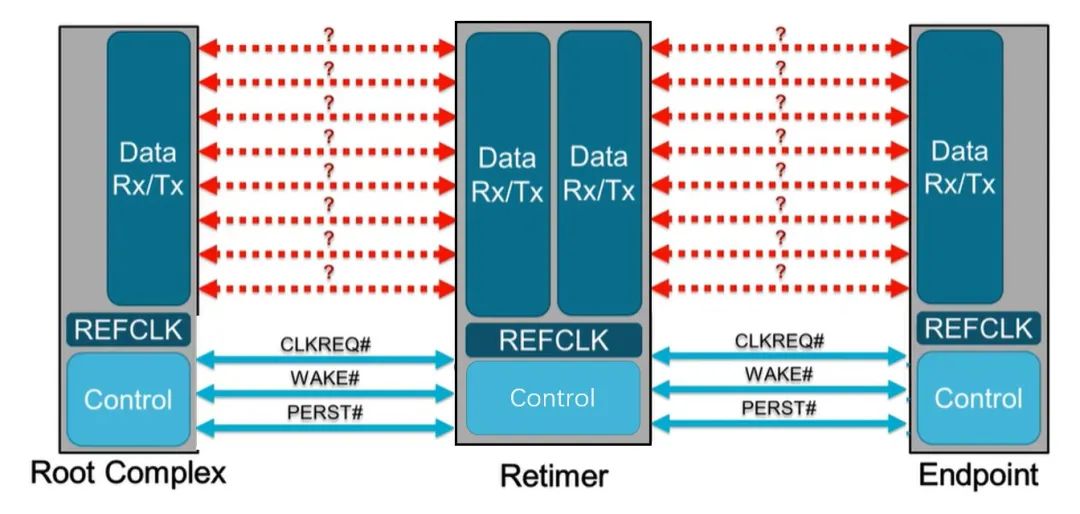

在了解PCIe链路是如何建立以及数据如何通过PCIe协议传输之前,我们先了解一下常见PCIe控制信号的功能。

图4

PERST#信号为全局复位信号,由处理器系统提供。处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑,当该信号有效时,PCIe设备将进行复位操作。

WAKE#和CLKREQ#信号都用于在本文讨论范围之外的低功率状态之间转换。

REFCLK#是PCIe设备开始数据传输的先决条件,PCIe设备通过使用REFCLK#提供的100 MHz外部参考时钟(Refclk),用于协调在两个PCIe设备间的数据传输。

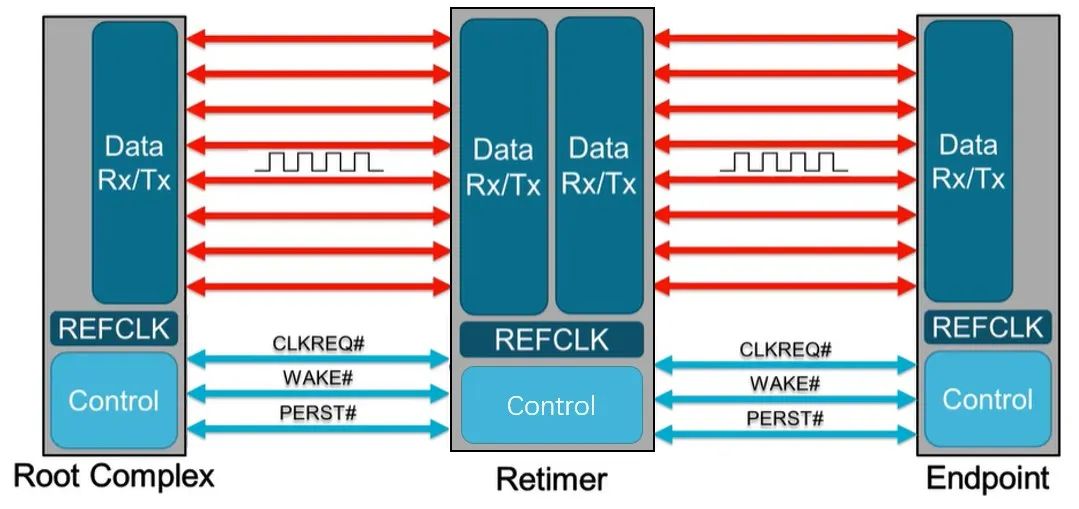

PCIe链路在初始状态时,需要检测对端设备是否存在,然后才能进行链路训练。所有PCIe设备通电并提供参考时钟信号后在每个通道上将拥有接收器检测电路(Receiver Detection circuit),该电路将允许PCIe设备确定是否有要配对的链路伙伴。假设PCIe Rx检测电路检测到另一个设备,则每个通道将开始以2.5 GT/s的速度进行传输串行数据。

图5

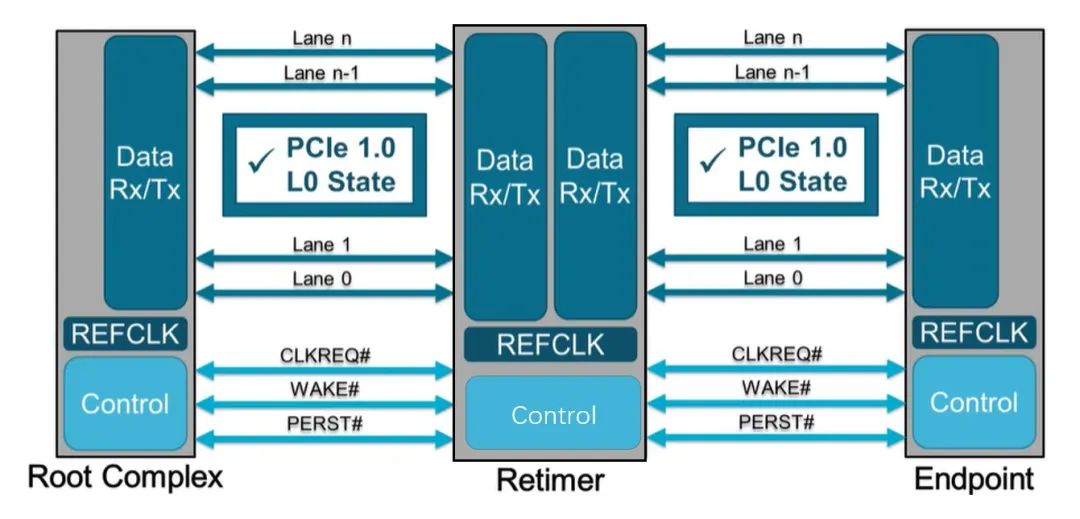

2.5 GT/s是第一代PCIe 1.0采用的数据速率,另外由于PCIe 1.0与任何PCIe设备兼容,因此每个PCIe链路都以相同的链路初始化过程开始。以下图为例,Root Complex、Retimer和Endpoint都以PCIe 1.0的速度开始传输。

图6

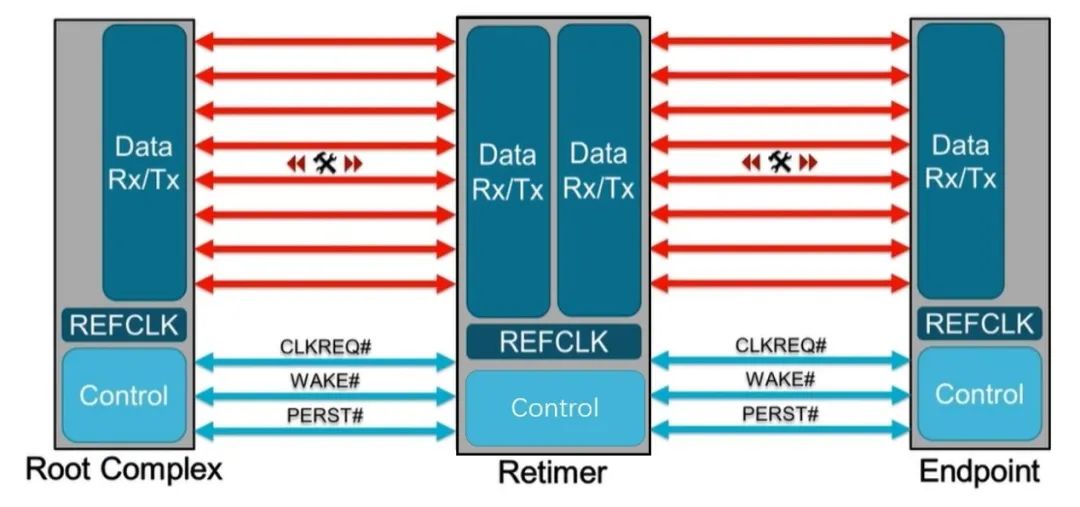

在经过PCIe链路初始化后,每个器件将能接收到数据并做出相应的响应。PCIe连接开始链路训练过程并进入配置阶段,在该阶段中,由于通道长度变化而导致数据中的任何偏差都能得到校准,PCIe链路的宽度、链路速率、链路翻转和链路极性也在此阶段确定。

图7

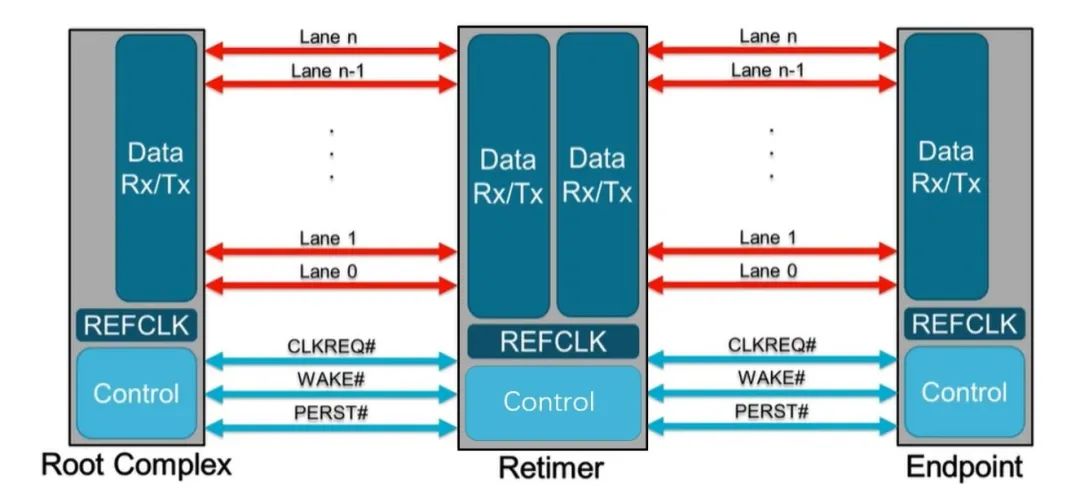

如果存在多条链路,则PCIe连接称为PCIe分叉。在示例中,有一个非分叉连接,即所有通道都分配给编号为0的链路。由于Retimer链路分为两部分,其两侧的链路分别进行链路初始化。在确定链路和通道号后,PCIe链路可以进入多种状态。

图8

以进入L0状态举例,这是发送和接收数据与数据包的正常操作状态。到达L0后Root Complex和Enpoint可相互通信,PCIe链路也可转换为多种低功耗状态或另一种链路训练状态。在此不做过多阐述。

图9

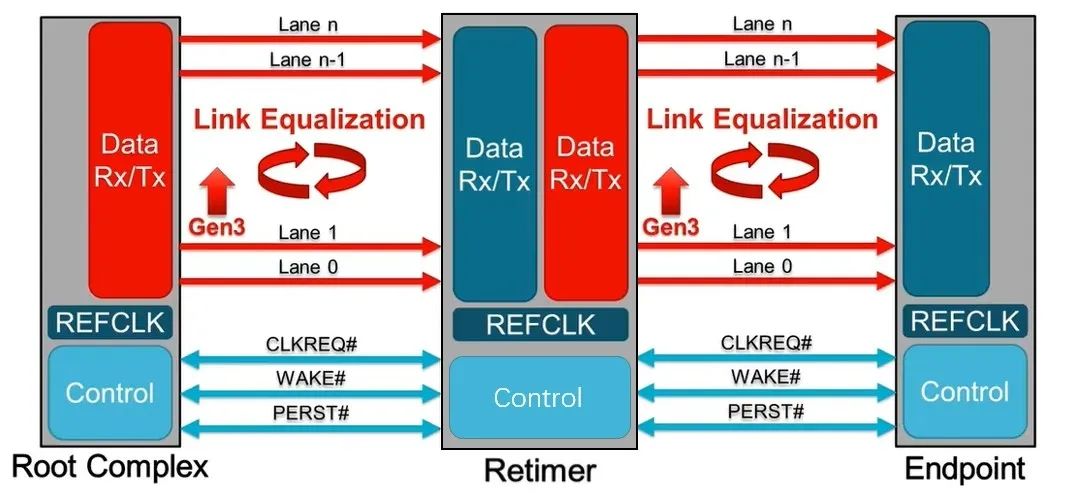

四、PCIe链路均衡

PCIe设备都支持PCIe Gen2,则链路速度也会随之提高。如果数据速率为PCIe Gen3或以上,PCIe链路将需要经历额外链路优化过程(称为链路均衡)。

链路均衡以建立设备间稳定的连接为目的。通过调节Tx (传输端)和Rx (接收端)的设置,提高信号质量,使PCIe链路以最稳定且更快的速率传输。由于PCIe在Gen3及以上的每一代均需优化连接,因此链路均衡过程可能发生多次。

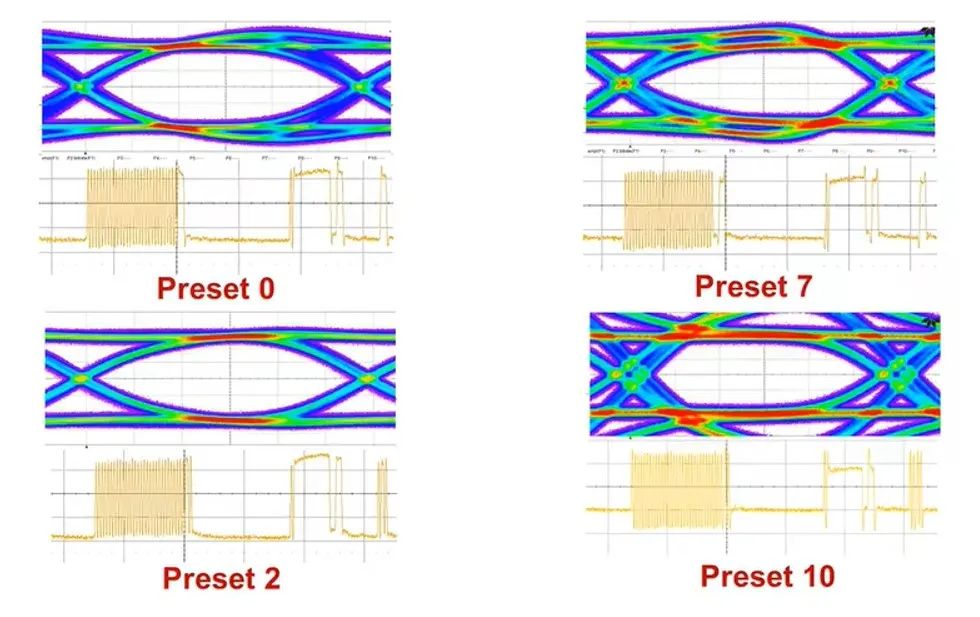

例如:若所有PCIe设备为Gen5,则有3次链路均衡过程(第1次:Gen1-Gen3;第2次:Gen3-Gen4;第3次:Gen4-Gen5)。链路均衡通过PCIe 规范中定义的preset值来实现,preset指不同的预过冲(Preshoot)和去加重(De-emphasis)的组合。对于Gen3和Gen4,有11个preset值,即preset0-preset10。对于不同的链路情况,系统要求Rx端发送Tx EQ preset设置请求给Tx端,让其做对应的preset均衡设置;Tx端发送Rx EQ均衡设置,要求Rx端做相应的设置,最终获得一个最优的均衡组合和Rx端的眼图。

图10

Phase0:第1阶段链路均衡涉及上游端口(Upstream port)和下游端口(Downstream port)之间的精确动态协商,下游端口通过向上游设备发送每个通道所需的发送器preset值来开始链路均衡,被称为第0阶段链接均衡。在接收到下游端口的请求后不久,上游端口增加到第3代(Gen3)链路数据速率,并开始使用所需preset将训练序列发送回下游端口。链路速度增加至Gen3(8 GT/s)后,链路均衡过程通过来回发送preset值来协商每个端口的preset配置,从而继续优化链路。

图11

Phase1:为了充分优化链路,以便能够交换训练序列(Training Sequences)并且完成用于精调目的的剩余链路均衡阶段,尽管有出现链路质量差的可能性,但相同的训练序列会被重复发送,来确保下游端口接收到正确的preset值。

图12

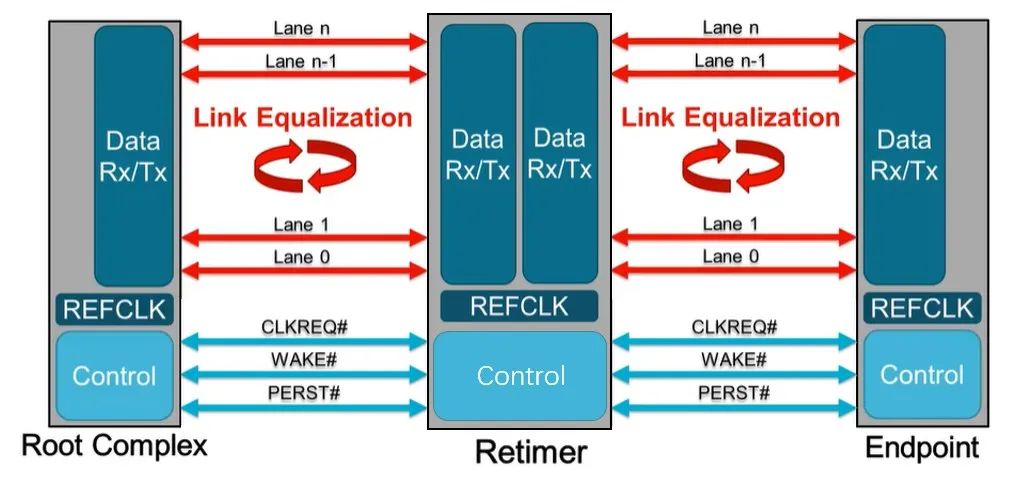

Phase2:在第1阶段链路的误码率实现BER≤10e-4后,进入到Phase 2,随后进一步优化上游端口的preset值,直至获得最优设置,链路的误码率应满足BER ≤ 1E-12。

Phase3:到第3阶段对下游端口执行相同的协商。上游端口通过训练序列发送均衡请求去调整下游端口的preset值,直至获得最优设置,链路的误码率应满足BER ≤ 1E-12。

当Phase3完成后,链路均衡也已完成,此时链路以Gen3的速率进入L0状态,并在该速率进行稳定通信。对于更高的传输速率,PCIe设备必须进行多次链路均衡过程。

图13

然而在某些主板设计中,尤其是那些具有长通道链路的主板,这种信号质量无法实现,可能需要另外的信号调节。在这种情况下,中继器(如ReDriver,ReTimer)则被用来做信号调节,并在PCIe设备和根复合体(在CPU,存储设备和PCIe设备之间的重要连接部分)之间提供高质量信号。

审核编辑:黄飞

-

PCIe简介、发展历史及架构2023-12-11 5644

-

Pcie串行总线介绍#高速接口我是Coder 2021-08-11

-

串行总线协议PCIe、ASI和sRIO之间有什么不同?2021-05-25 7169

-

学习常用接口总线的工作原理2021-08-23 1275

-

串行通信中的IIC总线工作原理是什么2021-12-08 1277

-

IIC总线AT24C02芯片工作原理2021-12-13 2565

-

IIC串行总线的组成及工作原理2022-02-23 1219

-

I2C总线的工作原理与应用2009-03-02 5955

-

串行端口工作原理2009-07-24 2375

-

通用串行接口(USB),USB的工作原理是什么?2010-03-19 3662

-

I2C串行总线的组成及工作原理的PPT课程2015-11-16 1055

-

什么是PCIe?2023-07-04 24859

-

I2C串行总线组成及工作原理2023-11-16 623

-

PCIe接口的工作原理 PCIe与PCI的区别2024-11-06 6386

-

PCIe总线授时卡的工作原理2026-02-03 187

全部0条评论

快来发表一下你的评论吧 !