一个设置改动噪底飙升27dB的原因分析

描述

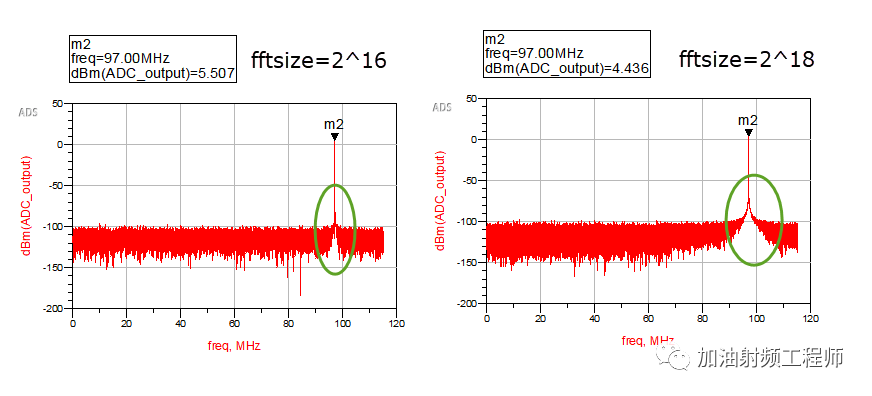

(1)问题的起因,是因为我更改了一下FFTSIZE的设置。

原来,我设置的是16,也就是打算让ADC采样2^16=65536个点的。

但是,在排查其他问题的时候,我把FFTSIZE改成18了。

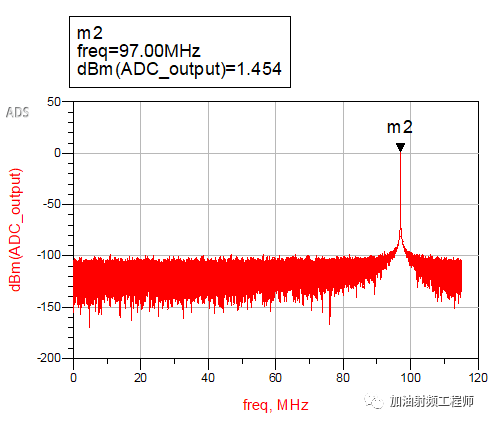

然后,就出现了下面这种情况,也就是信号那边抬上来了。

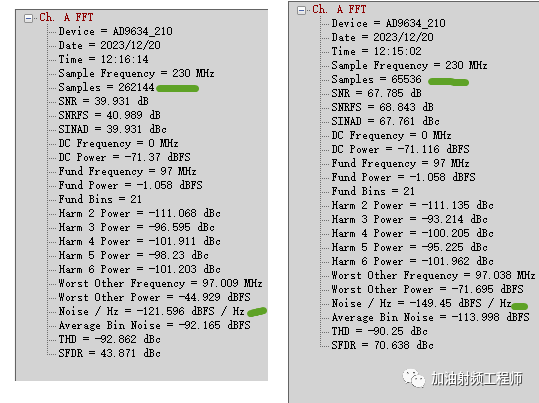

要是把code的数据,导入到VisualAnalog,看ADC的噪底的时候,发现噪底瞬间抬高27dB左右。

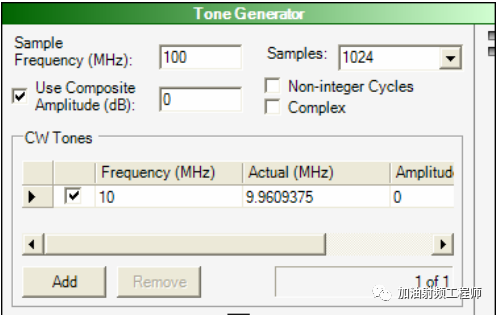

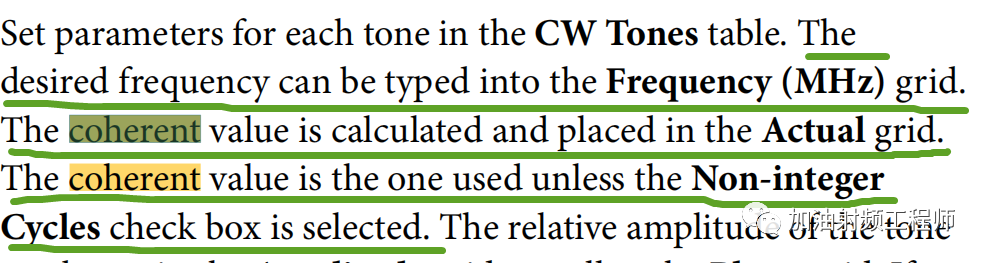

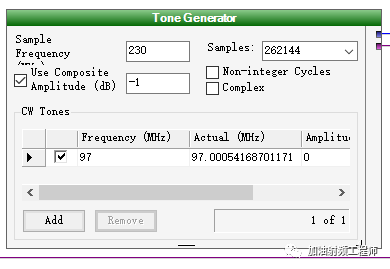

(2)ADI的VisualAnalog上,进行输入信号设置的时候,在Frequency旁边有一个Actual值,如下图所示。

看help文件,有这样一段话。

意思就是,Actual(MHz)下方的频率,才是实际的源的频率。这边有涉及到coherent sampling的概念。

(3)那ADS里面,仿真出现这个问题,会是这个原因么?

于是,我在VisualAnalog中设置了一下,算出一个Actual频率,并且把它代入ADS中。

但是,仿真出来的结果,并没有什么改变,仍然是抬高的。

所以不是这个原因造成的。

然后在ADS里面不断的更改设置,发现越改越茫然,发现仿真结果越来越不可控。

我好想变成一只鸵鸟,假装这一切都没有发生,我没有把FFTSIZE设置成2^18。

(4) 同时,又发现ADS里的AtoD的ADC模型,并不是不能在欠采样的情况下,折叠到第一奈奎斯特域,而是它对输入源有要求。

如果用Sinusoid作为输入,就能;如果用N_tone作为输入,就不能。

哎,把我整不会了。很惆怅~

(5) 昨天有报过课程的号友,发来消息说,有时候想回头看关于备课仿真的文章,但是发现从标题都看不出来哪些是。

其实,我把关于系统仿真探索仿真的文章,都放到了一个合集里,点这个就都能看到了。

审核编辑:汤梓红

-

TLV320AIC3101 ADC的底噪异常的原因?如何解决?2024-10-12 1416

-

请问音频底噪测试时,应该在音频信号分析仪上如何设置滤波器?2024-11-04 373

-

测试TLV320AIC3106时,发现在设置增益后有不同程度的底噪,为什么?2024-11-05 378

-

HMC702扫频模式噪底会比单点频输出时的噪底恶化10dB左右2018-08-22 1826

-

底噪的产生原因有哪些2021-07-28 3092

-

音频小音箱底噪分析2022-01-18 7277

-

为什么EMC测试中要求底噪比限值低6dB以上?2023-05-08 5817

-

AD9694底噪很高是什么原因造成的?2023-12-04 662

-

ADC AD9628-125输入功率增加到0dBm时,输出底噪随输入信号增加的原因?2023-12-06 604

-

可精确给出自身真实噪底的相噪分析仪Holzworth HA7000系列2021-01-04 6639

全部0条评论

快来发表一下你的评论吧 !