新型微电子封装技术问题及改进方案标准化研究

新型微电子封装技术问题及改进方案标准化研究

描述

欢迎了解

李彦林 丑晨 甘雨田

(甘肃林业职业技术学院)

摘要:

电子封装是将裸IC硅片用塑料包起来保护好并制作好外部引脚。外引线越来越多是微电子封装的一大特点,当然也是难点,引脚间距越小,再流焊时焊料难以稳定供给,故障率很高。多引脚封装是今后的主流,所以在微电子封装的技术要求上应尽量适应多引脚。但芯片的封装都是有一定规范的,假如每家封装厂都执行各自的标准显然芯片的通用性会大打折扣,也不可能造就半导体产业的繁荣。鉴于此,本文对不同电子封装技术问题展开讨论,分析电子封装技术存在的问题,设计具体改进方案,提高产品的可靠性,降低制造成本和安全风险。以期为微电子封装技术标准化生产提供借鉴和指导。

引 言

微电子封装是将一个或多个集成电路和倒装芯片键合连接,使之成为有实用功能的电子元器件或组件。本文探究对微电子封装技术的安全可靠性,通过技术攻关,攻克高密度窄间距小焊盘铜线键合工艺关键技术难题,提升铜线替代金线在小焊盘、窄间距 IC 芯片封装领域的工艺水平,促进企业技术创新和产品的自主开发能力,缩小与国外封装技术的差距,提升产品质量和标准化水平。

1 微电子封装技术和现状

电子封装技术涉及众多学科,涉及材料学、电磁学、热管理、微纳制造、电子器件等专业。随着微电子封装科学工作者对三维集成电路的研发逐步深入,电子封装正在从传统制造模式,向系统封装 (SOP - System On Package /SiP - System in Package)、三维封装 (3D Packaging) 模式转变,系统封装先进封装技术已经开始走向市场。而电子技术发展迅速,更新换代极快,三维封装 (3D Packaging) 目前尚无具体的国家技术标准,电子封装技术多采用国外研究的机构技术标准。封装的形式多种多样,以最普通的双列直插(DIP,dual in-line package)举例,DIP8 表示有8 个引脚,引脚的长度、间距、宽度等等都有严格的标准去执行,封装厂只会按照这个标准来执行,假如现在裸片只有 7 个 PAD 怎么办?当然还是要用 DIP8,只是一个引脚悬空,当然不可能随意的设计引脚个数,半导体产业各个方面都有标准,“无规矩不成方圆”,微电子封装技术从“原始生长”到“成熟发展”需要进行有机的规范。通过完善微电子封装技术相关标准,消除不同品牌的微电子封装技术硬件设备所采集的数据格式和数据质量存在差异,推动信息的流动和共享,消除数据孤岛成为新型微电子封装技术发展创新的迫切需求。

1.1 新型微电子封装技术

根据中华人民共和国国家质量监督检验检疫标准的要求 , 《微电子技术用贵金属浆料规范 (GB/T 17472-2008)》原标准适用范围,由厚膜微电子技术用贵金属浆料扩大至烧结型及固化型微电子技术用贵金属浆料;更注重浆料可焊性、耐焊性。 一般说来,微电子封装分为三级,包含组装和封装的多项内容。微电子封装所包含的范围应包括单芯片封装 (SCP) 设计和制造、多芯片封装 (MCM) 设计和制造、芯片后封装工艺、各种封装基板设计和制造、芯片互连与组装、封装总体电性能、机械性能、热性能和可靠性设计、封装材料、封装工模夹具以及绿色封装等多项内容。

1.2 新型微电子封装技术主要包括以下几种

发展微电子封装技术,旨在使系统向小型化、高性能、高可靠性和低成本目标努力,从技术发展观点来看,作为微电子封装的关键技术主要有:(1)3D 封装,在 2D封装的基础上,把多个裸芯片、封装芯片、多芯片组件甚至圆片进行叠层互连,构成立体封装,这种结构称作叠层型 3D 封装(2) 焊球阵列封装(BGA):阵列封装(BGA)以圆形或柱状焊点按阵列形式分布在封装下面,从而提高了组装成品率。组装可用共面焊接,可靠性高;(3) 芯片尺寸封装(CSP)是芯片级封装的意思。CSP 封装可以让芯片面积与封装面积之比超过 1:1.14,已经相当接近 1:1的理想情况。与 BGA 封装相比,同等空间下 CSP 封装可以将存储容量提高三倍;(4) 系统封装(SIP)即通过封装来实现整机系统的功能。

2 微电子三维 (3D) 封装技术问题分析

2.1 应用范围不够广泛

从微电子封装技术的材料可以看出,IC 芯片将向小型化、高性能并满足环保要求的方向发展。微电子封装技术应用范围不够广泛 , 在过去几年中已通用的高于 208 个管脚、256 个管脚、304 个管脚,间距 0.5mm 款式、包括间距 0.4mm 款式 QFPs,其 QFPs 材料多为塑料和陶瓷壳体,通常各类塑料型器件适合于较高的引线数。

2.2 传统铜线键合工艺问题

由于传统铜线键合工艺的极限能力为芯片焊盘尺寸≥ 50μm×50μm、焊盘间距≥ 60μm,对此尺寸以下的芯片只能采用金线工艺,而在研究过程中,要实现此金线工艺被合理替代,必须解决小焊点、窄间距铜线键合所面临的以下问题:

第一:铜线键合空气球防氧化技术;

第二:防止铜线键合焊盘损伤和对“铝飞溅”控制键合技术;

第三:第二焊点键合强度的研究;

第四:铜线键合防裂纹和弹坑技术。

随着 QFP 封装引线数的增加,其壳体尺寸急剧地增加,可以替代封装尺寸增加的是更进一步缩减引线间距。因此,要对高密度窄间距封装技术进行研发与技术改进。

3 具体改进方案

为了解决微电子三维 (3D) 封装技术方面的问题,我们制定了以下方案:芯片焊盘尺寸为 38μm×38μm,焊点间距为 43μm 的芯片;焊线材料:普通铜线,直径为0.7mil。开展不同保护气体中空气球尺寸的稳定性研究。

3.1 技术路线方案论证

3.1.1 技术路线

前期调研、规划→确定工艺流程→关键技术攻关→工程批试验→可靠性考核→风险批试生产→小批量生产→转入量产。

3.1.2 技术方案

为了解决以上问题,我们制定了以下二种方案:

A. 方案一

(1)铜线键合空气球防氧化研究

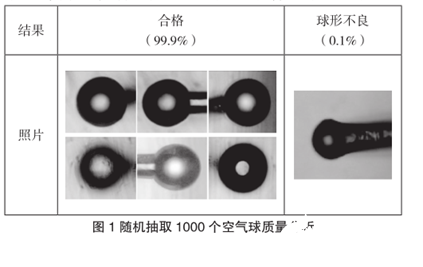

在氢氮混合保护气体(流量:0.4 ~0.7L/min)下,随机抽取 1000 个空气球对比结果如下:在 N2+H2 保护气体条件下,0.7mil 普通铜线烧球有 20.03% 的空气球表面有氧化和桃形球,非对称球、凹凸球、孔洞球等球形不良比例达到 40% 左右。

(2)第一焊点研究实验

第 一 焊 点 研 究 实 验 结 果 为 : 在 焊 盘 尺 寸 为38μm×38μm、焊点间距为 43μm 的芯片上进行铜线键合试验,球形不良(高尔夫球)占 57%,键合强度(不粘和失铝)不满足质量要求占 6.77%;图 1 随机抽取 1000个空气球质量分析 . 球形不良(0.1%)合格(99.9%)。

B. 方案二

芯片焊盘尺寸为 38μm×38μm,焊点间距为 43μm的芯片;

焊线材料:镀钯铜线(Pd coat Cu Wire),线径为0.7mil

(1)铜线键合空气球防氧化研究

通过对不同保护气体中空气球尺寸的稳定性、不同保护装置(Kit)中空气球形状的稳定性、保护气体流量(Froming Gas)对空气球影响的研究,达到了铜线键合工艺标准。

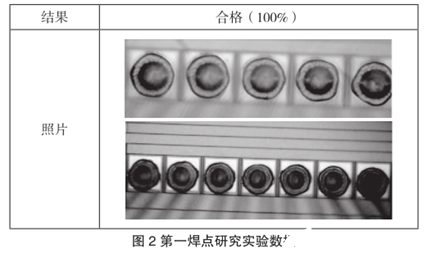

(2)第一焊点研究实验

选择配套设备和匹配的劈刀型号,对键合工艺参数进行研究,通过对功率、冲击力、X/Y 方向摩擦力、旋转摩擦力等参数进行优化试验,最终确定了一组较为理想的工艺参数。另外,联合芯片商对芯片铝垫进行了改善,并建立了铜线制程能力评估规范,使焊盘“铝飞溅”、失铝(Peeling)得到有效的控制,最终符合铜线键合工艺标准,第一焊点研究实验数据合格(100%)图 2 所示。

(3)第二焊点研究实验

通过优化劈刀的设计,选择合适的劈刀型号,增大了第二点接触的面积和鱼尾厚度;通过优化线弧参数,使鱼尾和 Lead 更贴合; [2] 通过优化焊接参数,增大了第二焊点功率、压力,必要时使用研磨参数,可增强第二焊点拉力并稳定线尾(Wire Tail Length);通过以上第二焊点键合质量的深入研究,达到了铜线键合质量标准。

(4)铜线键合防裂纹和弹坑研究

通过铜线材防氧化措施,焊盘铝层厚度、成分的控制,铜线键合快速确认焊盘铝残留厚度的研究,最终使铜线键合裂纹和弹坑得到了有效控制。

结论通过以上研究,使镀钯铜线键合能力满足工艺要求,达到了高密度窄节距(43μm)小焊盘(38μm×38μm)IC 芯片的封装要求。实现了 SEMI( 国际半导体设备与材料协会 ) 等国际标准化组织在电子封装领域内电镀技术的标准化要求。

4 结论

该方案采用焊盘尺寸为 38μm×38μm、焊盘间距为43μm、铝垫厚度为 0.9μm、介质结构为 FSG(氟硅酸盐玻璃)的芯片研究了铜线键合技术,建立了线径为 0.7mil高可靠性镀钯铜线键合工艺的制程能力,有效保障了小焊盘(38μm×38μm)窄间距(43μm)的铜线键合封装技术在 LQFP、TQFP 、eLQFP、多圈 QFN 系列产品中的推广应用。因此,本设计方案能实现该项目的技术指标,达到研究的目的和意义,为标准化生产提供了技术保障。

审核编辑 黄宇

-

哪些财务分析工具有标准化方案?2022-12-13 11028

-

关于新型微电子封装技术介绍的太仔细了2021-04-23 3040

-

中国电子技术标准化研究院召开数字孪生标准化工作研讨会2021-04-09 3526

-

AI技术应用标准化研究基地在厦门正式揭牌成立2019-01-30 3562

-

PCB设计和制造数据交换技术及标准化2018-11-22 3064

-

新型微电子封装技术的发展和建议2018-09-12 3593

-

国内标准组织启动量子通信标准化预研2017-06-19 3393

-

封装如何标准化2016-11-07 3825

-

微电子封装技术2013-12-24 6363

-

微电子封装及微连接技术.pdf2012-08-19 5259

-

国内LED照明产品零部件的标准化2011年底完成2011-09-15 3019

-

探讨新型微电子封装技术2011-01-28 4512

-

EPON标准化进展2010-04-24 2050

-

PROFIBUS 技术及标准化及技术来由2009-11-17 3251

全部0条评论

快来发表一下你的评论吧 !