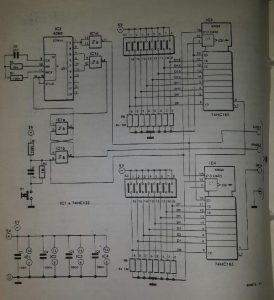

串行数据发生器电路原理图

描述

使用数据发生器测试电路

数据生成器提供了一种简单的电路测试方法,无需复杂的软件。所有必要的组件都很容易接近。该电路设计围绕 SDA3002 型电路的时序进行构建,采用三线连接而不是两线 I2C 格式。在仅需要单个固定数据字的情况下,可以省略 DIP 开关 S2 和 S3 以及八倍拉电阻阵列。这导致 IC3 和 IC4 的输入保持在固定电平。该发生器的基础是两个级联移位寄存器(IC3 和 IC4),用作与串行转换器并行运行的 16 位寄存器。

时钟生成和初始化

IC2 提供时钟,通过使用按钮开关 S1 设置双稳态 IC1a.b 来启动。按下 S1 后,通过微分网络 R1 和 C1 施加 100 脉冲以设置双稳态的输入。电容器通过 R2 放电。值得注意的是,即使按住 S1,脉冲持续时间也保持恒定。这对于防止时序差异至关重要,因为超过半个时钟周期可能会导致问题。 IC1b 的输出用作被测电路的使能信号。启动脉冲还有助于将用 DIP 开关配置的逻辑电平加载到移位寄存器上。只要引脚 1 处的信号为低电平,寄存器就接受并行数据,这强调了短启动脉冲的必要性。

测试周期启动和时钟生成

整个测试周期的开始由启动信号标记。参见图2的时序图,IC2的输出23经过IC1d反相,作为移位寄存器的时钟源。这种安排可确保 D0 在整个时钟周期内保持在输出状态,持续 1.25 ms。当达到高输出 18 次时,双稳态复位,IC1 的输出 23(与 IC2 的输出 25 和 28 连接)将启用线拉低,结束周期。

可变位移位和双稳态加法

在此图中,总共 18 位经历了移位。两个最高有效位 (MSB) 受 IC3 串行输入的影响。如果该输入寄存器为高电平,则 D16 和 D17 被设置为“1”。如果需要灵活地使这些位成为变量,则必须引入一个或两个作为移位寄存器连接的附加双稳态。当所有位都为高电平时,发生器的电流消耗(主要由下拉电阻决定)仍然非常低,约为 80。按下 S1 后,振荡器会短暂激活,使电流加倍。

-

脉冲发生器的电路原理图免费下载2021-03-17 1882

-

请问有直流高压发生器电路原理图吗?2019-09-18 2180

-

信号发生器电路图免费下载2019-01-09 2340

-

波形发生器原理图+电路图+程序2017-11-23 11652

-

脉冲发生器原理图2016-05-11 1353

-

臭氧发生器电路原理图2011-07-04 30954

-

负离子发生器电路原理图2011-04-04 46709

-

声频噪声发生器电路原理图2009-12-07 2459

-

串行数据输出倾角传感器电路方块电路图2009-07-03 742

-

波形发生器,含原理图+电路图+源程序2009-06-11 7725

-

三角波发生器电路原理图2009-05-08 19029

-

直流高压发生器电路原理图2009-05-06 7897

-

延时发生器原理图2009-03-28 1032

全部0条评论

快来发表一下你的评论吧 !