D型触发器(延时电路)应用电路图解析

描述

使用D触发器的移位寄存器

D触发器的移位寄存器是一种重要的数字系统和计算机中应用很广泛的基本逻辑部件,它不只可以寄存数码,而且在移位脉冲的作用下,可以根据需要使寄存器中的数码向左或向右移动。具体来说,移位寄存器是由多个D触发器构成的,每个触发器可以存储一位数据,因此对于n位移位寄存器,就需要n个触发器。

根据具体的设计需求,移位寄存器可以实现不同的功能。例如,当要求上升沿触发,具有异步复位功能时,可以在Logisim中构建由4个D触发器构成的右移移位寄存器。此外,如果需要实现数据的并行输入或串行输入和串行输出或并行输出,也可以在设计时进行相应的调整。

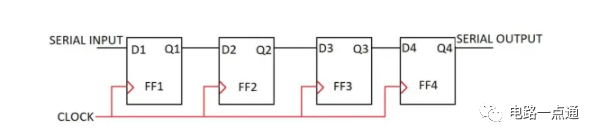

使用 D 触发器的串行输入串行输出移位寄存器

在这种类型的寄存器中,输入是一次一位串行,输出也是串行一位。

带D触发器的串行输入串行输出移位寄存器设计

每个触发器一次只能存储一位,因此对于 4 位移位寄存器,需要四个触发器。如上所示,串行数据通过第一个触发器的 D 应用到所有剩余的触发器。当一系列数据输入寄存器时,每一位都随着时钟脉冲的每个正沿提供给下一个触发器,并且随着每个时钟脉冲,串行数据从一个触发器移动到下一个触发器。

8位寄存器D触发器

8位寄存器D触发器是一种重要的数字系统和计算机中应用广泛的基本逻辑部件,它由8个D触发器构成,每个触发器可以存储一位数据。在具体的设计中,D7—D0为寄存器的输入,q7—q0为寄存器的输出,cp则是寄存器的时钟脉冲。

根据具体的设计需求,这种8位的寄存器D触发器可以实现不同的功能。例如,可以通过调用写好的D触发器来构建一个寄存器,并通过一个顶层模块将整体穿起来,实现所需的功能。此外,如果需要实现数据的并行输入或串行输入和串行输出或并行输出,也可以在设计时进行相应的调整。

8位寄存器可以设计一个8D触发器。

用D触发器设计的8位通用移位寄存器示意图

使用D触发器的3位同步计数器

三位同步计数器是一种数字电路,它利用D触发器和适当的逻辑门电路来实现同步加法计数的功能。这种计数器的工作原理是通过三个D触发器进行级联连接,每个D触发器代表一个二进制位。当时钟信号到来时,首先将输入的值加1,将其结果通过逻辑门传递给相邻的D触发器,同时也将时钟信号传递给下一个级联的D触发器,以确保计数器的同步性。

在设计上,可以将这三个D触发器的输出端连接到一个3位数码管显示计数结果。此外,如果需要实现数据的并行输入或串行输入和串行输出或并行输出,也可以在设计时进行相应的调整。

用 D 触发器设计的 3 位二进制计数器示意图

-

D触发器不同应用下的电路图详解2023-01-06 9562

-

rs触发器电路图与rs触发器内部电路图2022-10-19 34453

-

图文并茂:D型触发器电路设计教程2021-02-03 13658

-

如何用JK触发器构成D触发器 电路图2011-11-14 45644

-

J-K触发器组成D触发器电路图2010-09-24 8879

-

D触发器组成T和J-K触发器电路图2010-09-20 21900

-

双D触发器延时熄灯控制电路图2009-06-13 2355

-

D触发器的制作及电路图2009-05-19 3941

-

时基触发器电路图2009-05-18 589

-

T触发器电路图2009-05-08 10552

-

长延时电路图解2009-04-13 1084

-

D触发器2008-10-20 2802

全部0条评论

快来发表一下你的评论吧 !