AI在半导体器件生产测试中的应用

描述

“时间就是金钱”这句话在半导体器件的生产测试中尤为贴切。

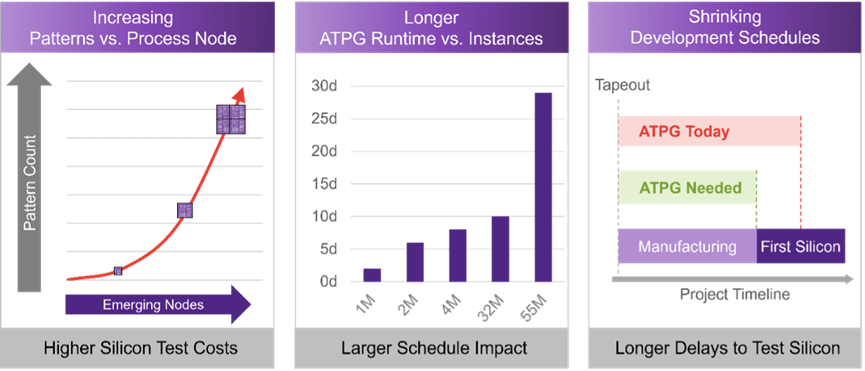

因为只有晶圆或芯片测试完毕后,其他部件才能开始测试。测试速度越慢,就越需要更多的自动化测试设备(ATE)来满足生产测试吞吐量要求。最近几代的先进工艺节点器件有更多的测试引脚数、更快的测试通道和更大测试向量存储容量导致ATE硬件的价格大幅上涨。

此外,由于芯片功能的不断增加,需要测试的逻辑增加,因此需要更多的测试向量和测试仪内存,成本也随之增加。更多的测试向量还需要更长的测试运行时间,为了保持吞吐量,就需要增加测试仪数量。

所以说,如果测试速度不够快,芯片生厂商的成本会越来越高。

自动测试向量生成(ATPG)广泛用于生成在生产测试仪上运行的程序。现代芯片的复杂性也给测试过程带来了压力,通常需要较长的运行时间,这可能会导致生产测试推迟。

特别是对于需要测试数百万芯片的大批量产品而言,每节省一秒钟的测试时间都会带来巨大的收益。然而,在减少测试向量的同时,必须保证尽可能高的测试覆盖率或向客户交付的产品质量。因此,有效的高效ATPG解决方案对生成的测试程序乃至生成过程都有很高的要求。

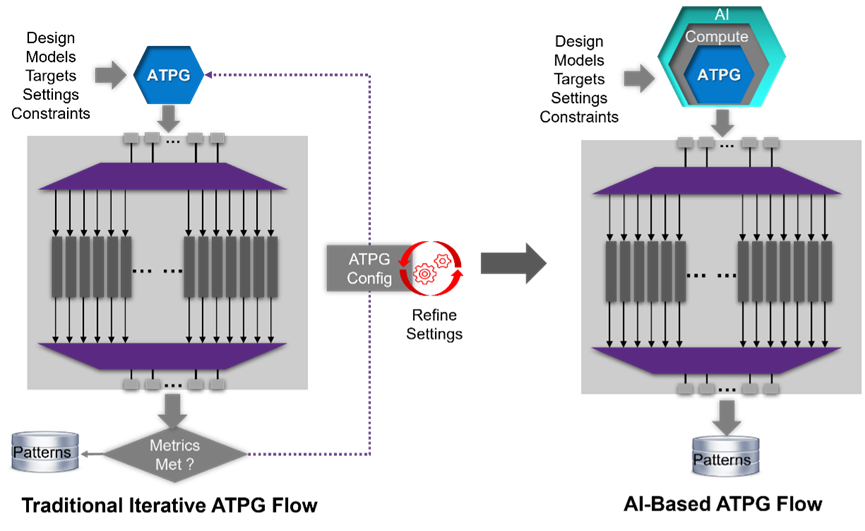

传统的向量生成流程是一个迭代的手动循环,开发者首先要设置典型的ATPG工具参数,如提供故障模型、定义设计约束、指定所生成测试的ATPG指标目标等。然后,开发者对达到目标结果质量(QoR)所需的工具设置做出尽可能准确的估计,并运行测试向量生成。

第一次尝试很可能无法达到ATPG目标,通常需要大量的专业知识和多次尝试,而且开发者需要对工具设置进行反复微调,才能收敛到可接受的结果。之所以会出现这种情况主要是由于多个ATPG工具参数之间的相互依赖关系及其对ATPG QoR的影响,使得手动管理变得非常复杂。即便是测试专家,也需要更长的时间才能获得理想结果。

即使使用这样的流程达到了预期的结果,也无法保证设计之间的可重复性,因此周转时间和测试向量签核时间表拥有一定的不可预测性。这可能意味着,当芯片从晶圆厂运回进行测试时,测试向量可能还没有准备就绪,从而使ATPG在关键路径上和设计进度上面临风险。

引入人工智能(AI)是满足现代测试向量生成流程要求的一种创新方法。基于人工智能的ATPG解决方案可以通过并行运行的方式,不断学习设计特性、ATPG引擎行为、用户约束/目标以及可用的设置。在优化设置时,通过对结果进行相关性分析,了解哪些有效、哪些无效,这正是人工智能擅长的工作。在这个工具内部,无需任何手动迭代或设置操作,即可收敛至测试覆盖率目标,从而实现一次就正确的结果。

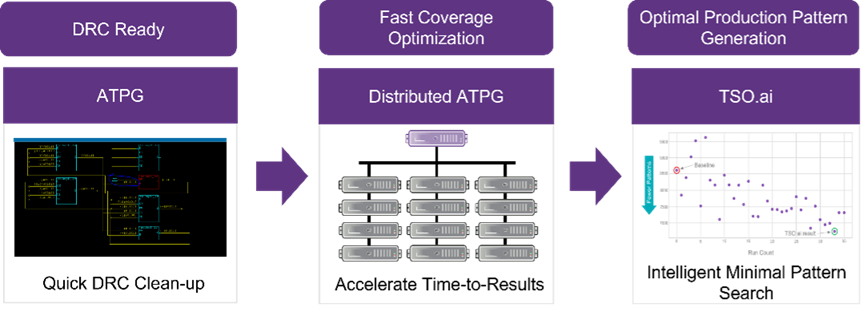

以下是我们建议的流程:使用标准ATPG进行初始运行,以获得干净的设计DRC,然后使用分布式ATPG运行,通过网表下降和/或ATPG更改来分析、优化和验证目标测试覆盖率,运行时间非常短。在达到所需的测试覆盖率后,可以利用人工智能尽量减少芯片进入生产测试前所需的测试向量。这一流程可以在保证设计进度的同时,得到低成本高质量的测试向量,并实现快速周转。

新思科技TSO.ai(测试空间优化)是一种人工智能驱动型ATPG解决方案,可学习和调整设置,持续生成尽可能少的测试向量,同时消除不必要的迭代,加快任何设计的结果生成时间。在一些情况下,当测试仪内存有限时,它还能在固定测试向量数量下实现更高的测试覆盖率。该技术可用于最大限度地减少最终流片网表或已投入生产的设计所需的测试向量,以快速节省测试成本,同时也可在整个设计过程中通过网表下降进行学习,以缩短最终向量减少过程的周转时间。

事实表明,这种方法可在所有应用领域实现一致的测试成本降低,通常情况下向量数量会减少20%至25%,在某些情况下甚至超过50%。这加快了生产测试的速度,节省了时间和成本,同时减少了特定产量所需的测试仪数量。

审核编辑:汤梓红

-

BW-4022A半导体分立器件综合测试平台---精准洞察,卓越测量2025-10-10 893

-

「聚焦半导体分立器件综合测试系统」“测什么?为什么测!用在哪?”「深度解读」2026-01-29 5097

-

仿真技术在半导体和集成电路生产流程优化中的应用2009-08-20 3209

-

半导体器件生产中的静电2013-07-03 2915

-

半导体生产中的静电问题2013-07-23 4013

-

SPC在半导体在半导体晶圆厂的实际应用2018-08-29 4482

-

【基础知识】功率半导体器件的简介2019-02-26 11486

-

是不是所有的半导体生产厂商对所有的器件都需要进行老化测试?2019-08-02 4245

-

半导体功率器件的分类2021-07-12 5196

-

什么是基于SiC和GaN的功率半导体器件?2023-02-21 10222

-

霍尔效应在半导体性能测试中的作用2023-12-25 3737

-

安泰高压功率放大器在半导体测试中的应用2024-01-15 1217

-

半导体在热测试中遇到的问题2025-01-06 1949

-

是德示波器在半导体器件测试中的应用2025-07-25 952

-

半导体器件的通用测试项目都有哪些?2025-11-17 2846

全部0条评论

快来发表一下你的评论吧 !