浅谈存储芯片的分类

描述

DRAM芯片全称是动态随机存储器,是一种随机存储器(RAM),与CPU直接交换数据,可随时读写且速度快,断电后存储数据丢失,是易失性存储器,也就是俗称的“内存”。

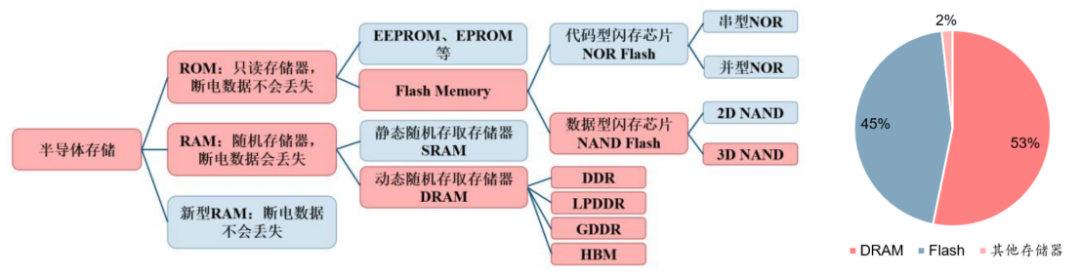

一、存储芯片的分类:随机存储器(RAM)、只读存储器(ROM)

(一)存储芯片大类:RAM、ROM

半导体存储芯片可以分为随机存储器(RAM)和只读存储器(ROM)两大类:

1、随机存储器(RAM):是易失性存储器,即断电后存储数据丢失,可理解为内存,未保存下关机重启进程会丢失;

2、只读存储器(ROM):是非易失性存储器,即断电后所存数据不会丢失,但只能读取事先存储的信息,可理解为硬盘、U盘、存储卡,保存后文件内容都存储在芯片中。

随机存储器(RAM)中,以DRAM为主流;只读存储器(ROM)中,以Flash为主流,两者占整个半导体存储芯片的98%,也是我们日常使用最多两个参数的4GB/8GB/16GB+64GB/128GB/256GB所形容的两类芯片。

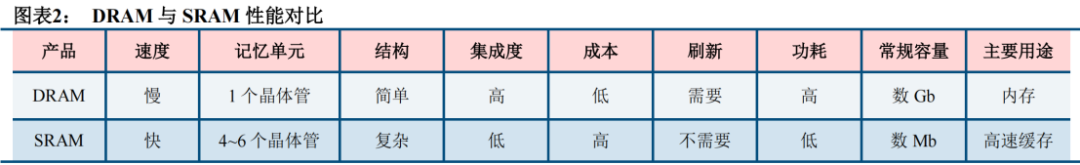

(二)RAM分类:DRAM动态随机存取存储器、SRAM静态随机存取存储器

在RAM中有动态随机存取存储器(DRAM)和静态随机存取存储器(SRAM)。DRAM用作内存,需求量远高于SRAM。SRAM速度很快但成本高,一般用于作CPU的高速缓存。

(三)同步DRAM分类:DDRSDRAM、LPDDR、GDDR

DRAM的工作原理是利用电容内存储电荷的多寡来代表一个二进制比特(bit),具备运算速度快、掉电后数据丢失的特点,常应用于系统硬件的运行内存,主要应用于服务器、PC和手机等。

在结构升级方面,DRAM分为同步和异步两种,两者区别在于读/写时钟与CPU时钟不同。传统的DRAM为异步DRAM,已经被淘汰,SDRAM(SynchronousDRAM,同步动态随机存储器)为DRAM的一种升级,读/写时钟与CPU时钟严格同步,主要包括DDR、LPDDR、GDDR、HBM等。

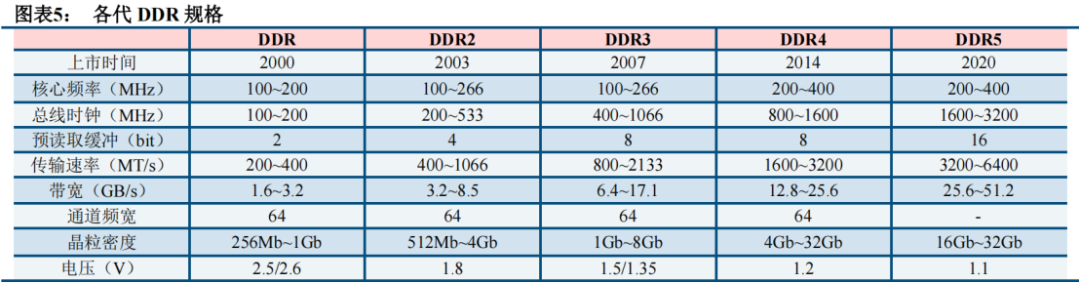

1、DDRSDRAM(双信道同步动态随机存取内存)

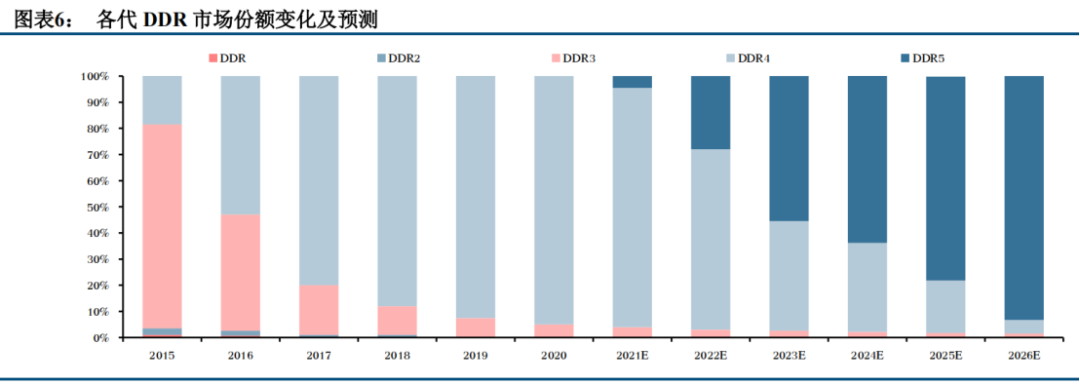

可以在一个时钟读写两次数据,使得传输数据加倍,目前已发展到第五代,每一代升级都伴随传输速度的提升以及工作电压的下降。根据Yole预测,随着DDR5的上市,市场将快速进行产品升级换代,预计2025年DDR5的份额将接近80%。

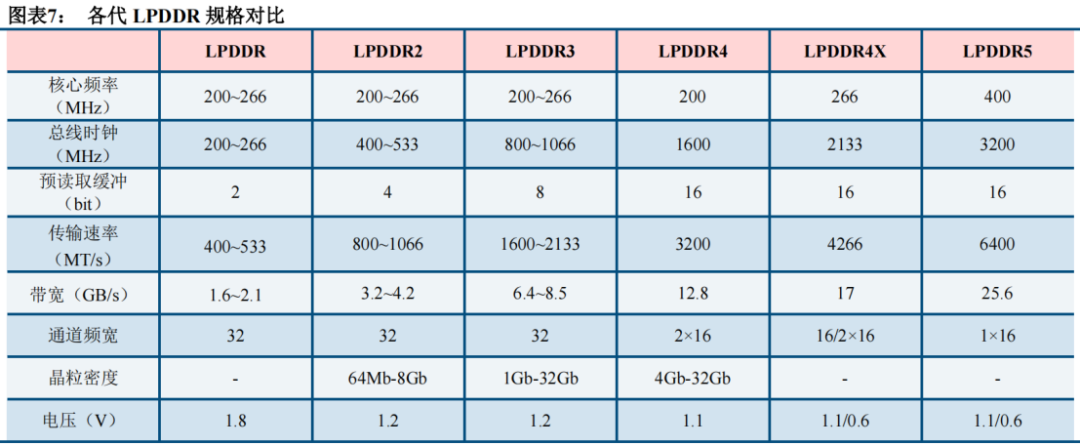

2、LPDDR(低功耗双信道同步动态随机存取内存)

通过与处理器紧邻(焊接在主机板上而非插入或以封装层叠技术直接堆在处理器上方)、减少通道宽度以及其他一些牺牲部分反应时间的方法来降低体积和功耗。LPDDR内存多用于智能手机、笔记本、新能源车上,而DDR多用于服务器、台式机、普通笔记本上。

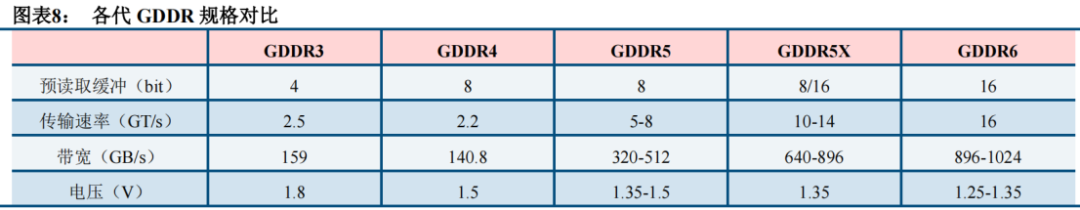

3、GDDR(绘图用双信道同步动态随机存取内存)

为专门适配高端绘图显卡而特别设计的高性能DDR储存器。GDDR与一般DDR不能共用,时钟频率更高,发热量更小,一般用于电竞终端和工作站。

二、DRAM的发展趋势:高性能低功耗、从2D架构转向3D架构

(一)高性能和低功耗是性能升级的两大主要趋势

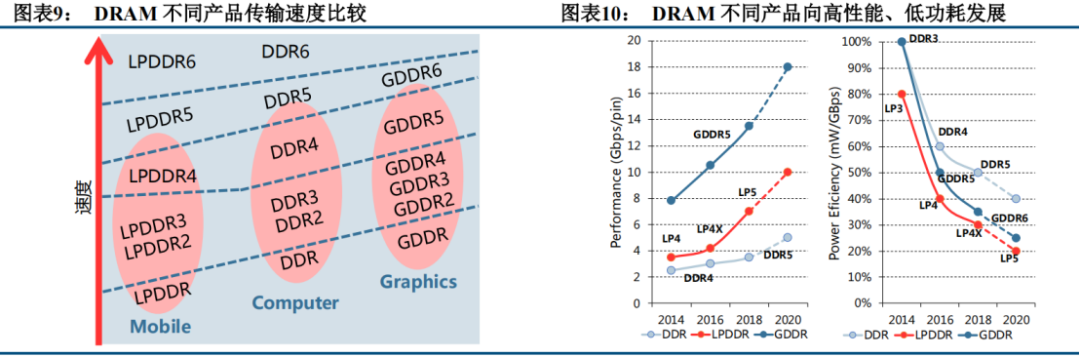

一般来说,绘图用DRAM数据传输速度高于计算机用DRAM,计算机用DRAM高于手机用DRAM。近年来,各类DRAM更新迭代快速,高性能和低功耗是两大主要趋势,目前DDR、LPDDR、GDDR已发展至第5-6代,较前一代传输速率大幅提升,功耗大幅度降低。手机DRAM方面,目前业内已量产LDDR5;计算机用DRAM方面,目前已演进至DDR5;绘图用DRAM方面,最新一代的GDDR6已商用数年。

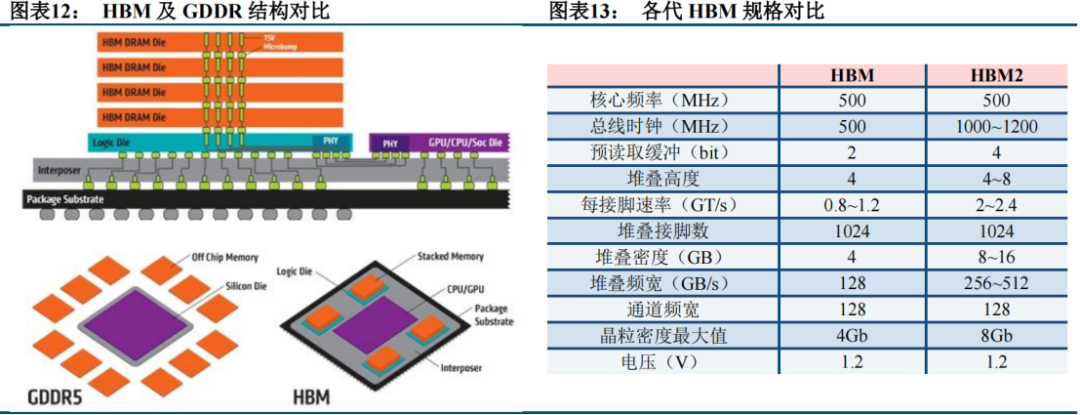

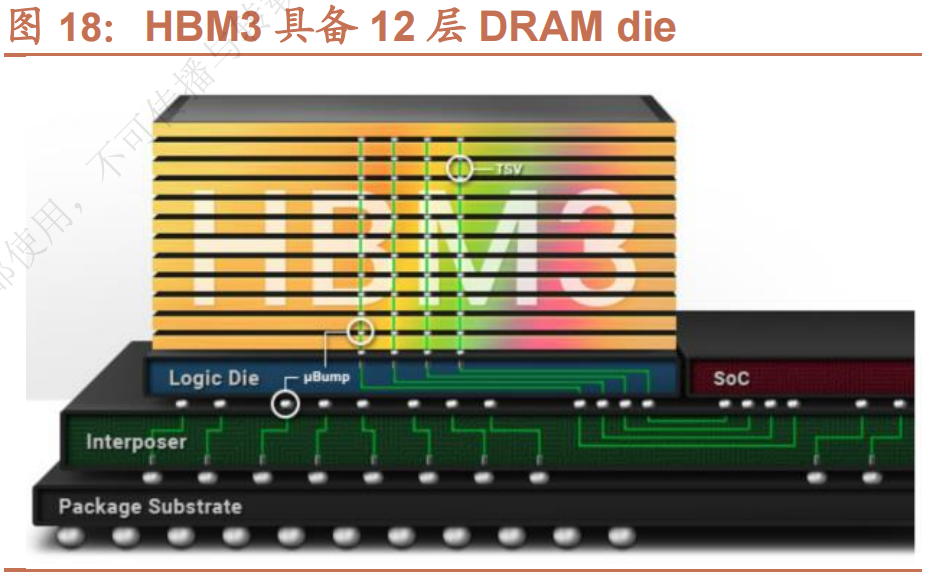

(二)从2D架构转向3D架构:HBM

DRAM从2D架构转向3D架构演变的典型产品为HBM。HBM(HighBandwidthMemory,高带宽储存器)是AMD和SK海力士推出的一种基于3D堆栈工艺的高性能DRAM,适用于高储存器带宽需求的应用场合,如图形处理器、网络交换及转发设备(交换机、路由器)等。

HBM将原本在PCB板上的DDR内存颗粒和GPU芯片同时集成到SiP封装中,使内存更加靠近GPU,DDRDie采用堆叠方式,通过增加单个DDR容量和层数来实现内存容量和带宽的提高。

目前最先进的HBM为第五代HBM3以及第六代HBM3E,封装的DRAMDie层数达到12层。

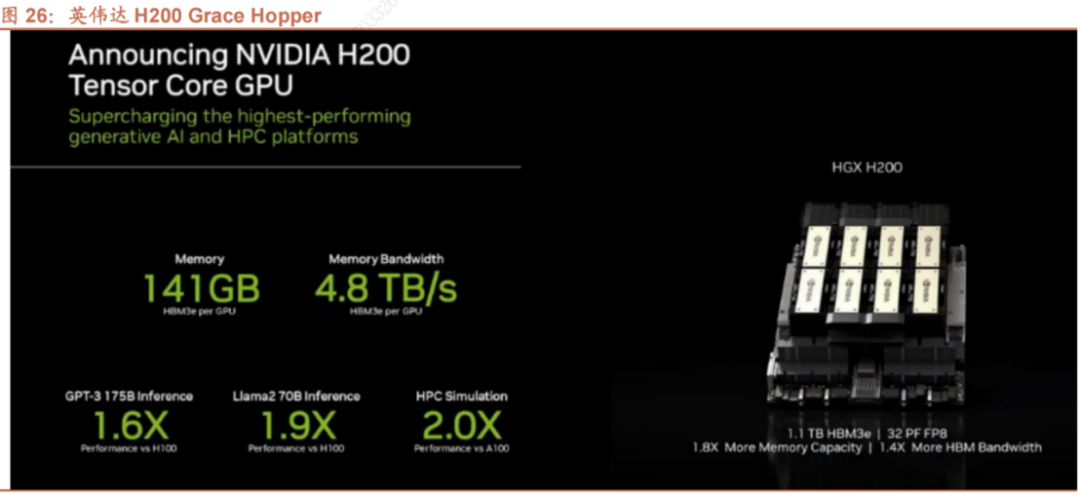

HBM已普遍搭配主流AI训练芯片使用,相较GDDR带宽显著提升。例如英伟达的DGXA100单GPU搭载了总计80GB容量的HBM2E,DGXH100单GPU搭载了总计80GB容量的HBM3存储,单个HBM3存储带宽最高可达819GB/s,较单个GDDR带宽提升10倍以上,H200更是搭载了共141GB的HBM3e内存,总HBM容量较H100提升76%,总带宽提升约43%。

英伟达于11月13日上午在“Supercomputing23”会议上正式发布了全新的H200GPU和改进后的GH200,每个H200GPU搭载HBM3e容量进一步提升至141GB。

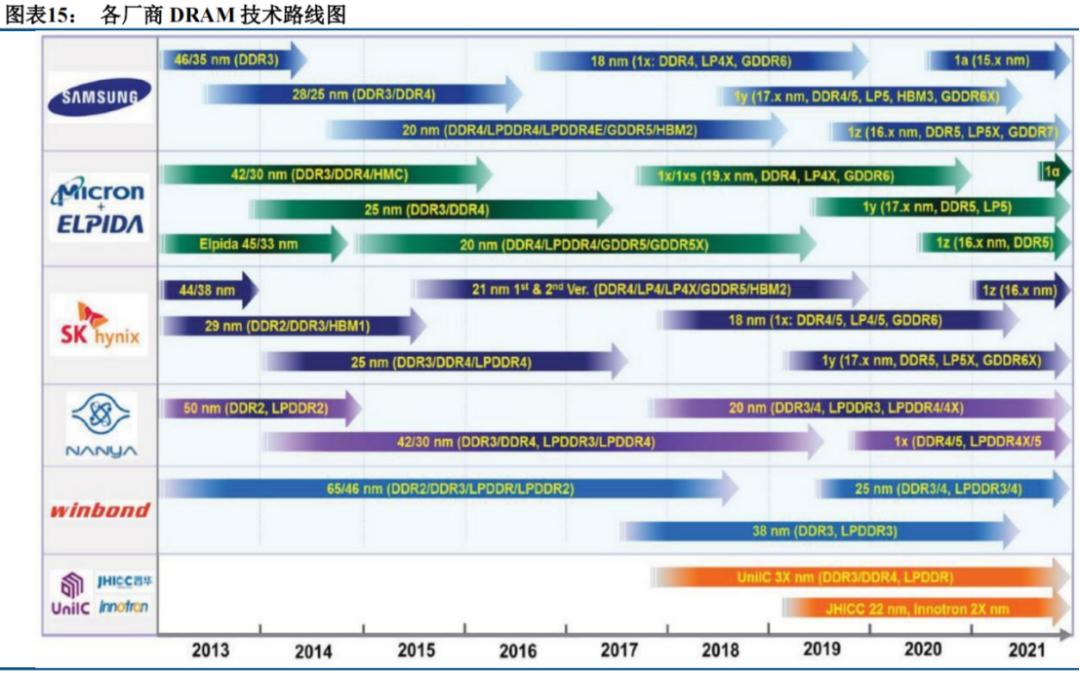

(三)制程演变:演进至10+nm

DRAM工艺制程演进至10+nm,将继续向10nm逼近。DRAM的制程接近10nm,各厂家都处于10nm+阶段。

业界命名DRAM前三代10nm+制程分别为1X(16-19nm)、1Y(14-16nm)、1Z(12-14nm)。行业龙头三星电子、SK海力士和美光在2016~2017年期间进入1Xnm阶段,2018~2019年进入1Ynm阶段,2020年后进入1Znm阶段。最新的1αnm仍处于10+nm阶段,三星于2020年3月率先完成技术开发,美光和海力士紧随其后,各家大厂将继续向10nm逼近。

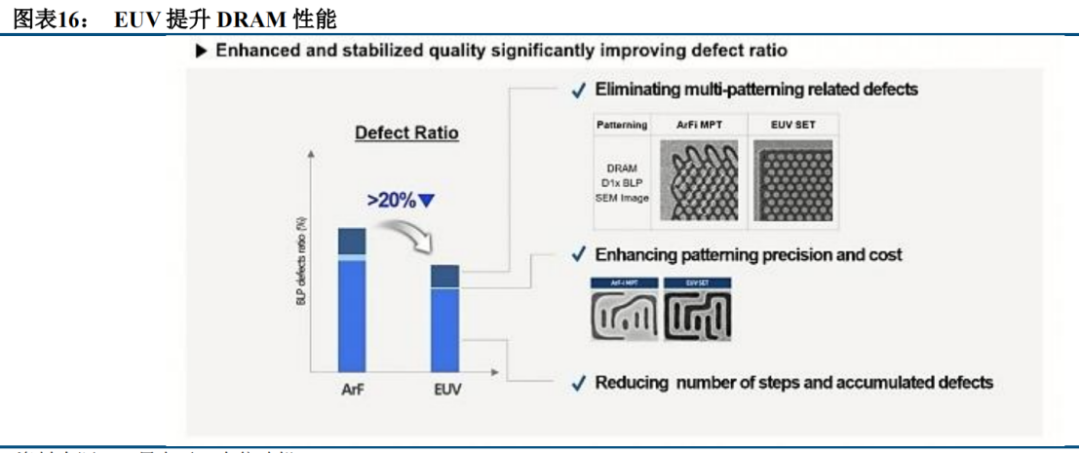

从光刻技术上看,由DUV转向EUV。目前DRAM使用最为成熟的光刻技术是193nm的DUV光刻机,EUV光刻机使用13.5nm波长,可通过减少光罩次数来进一步压低成本,提高精度和产能。在工艺制程达到14nm后,采用EUV的经济性开始显现,而DUV需使用多重曝光(SAQP)技术才能形成更细线宽的电路,因此成本上处于劣势。

目前DRAM厂商仍可通过工艺改进使用DUV生产10+nmDRAM,未来DRAM生产转向EUV将是必然。三星、SK海力士分别于2020年和2021年引入EUV技术来制造DRAM,美光预计在2024年生产基于EUV的DRAM。

三、DRAM下游行业及推动力:主要用于计算,AI算力提升推动DRAM需求

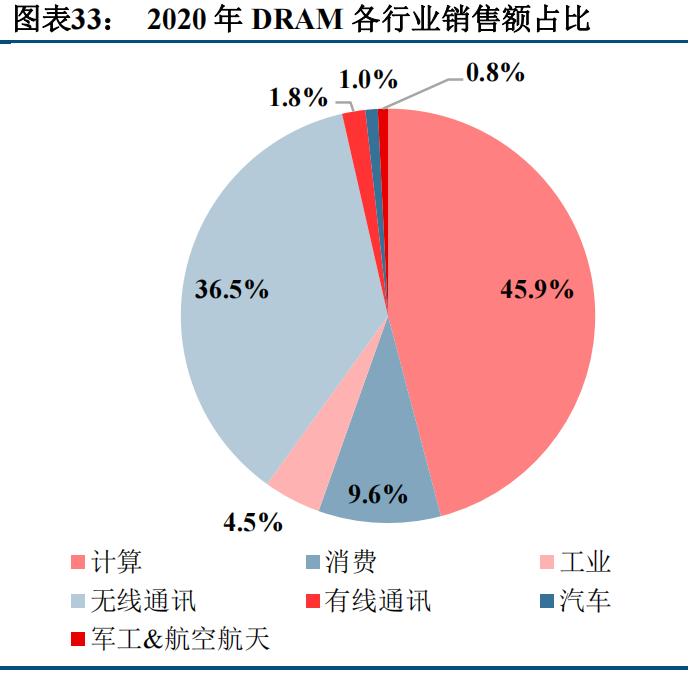

2020年DRAM下游市场中,计算、无线通讯、消费和工业分别占45.9%、36.5%、9.6%、4.5%。随着CPU主频、核心和线程数量的不断提升,CPU运算处理的速度已经远超硬盘的读写速度,因此需要CPU内存作为桥梁来暂时存放CPU中的运算数据,并与硬盘等外部存储器交换数据。

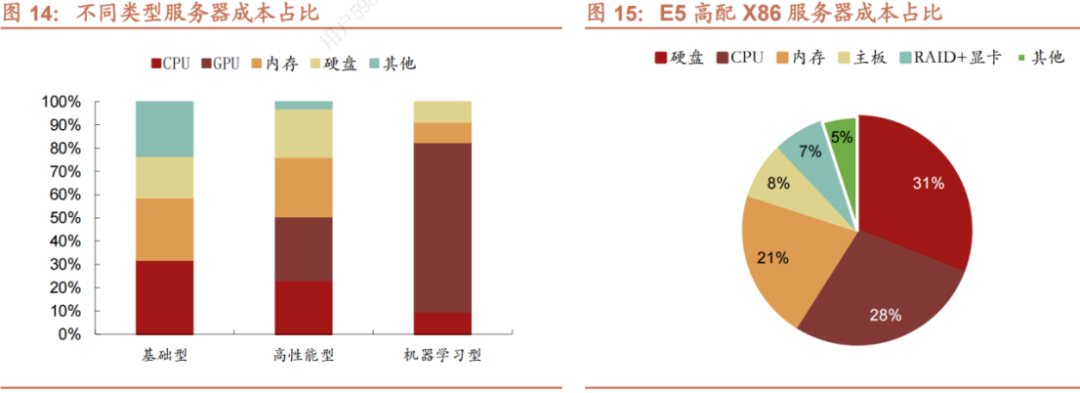

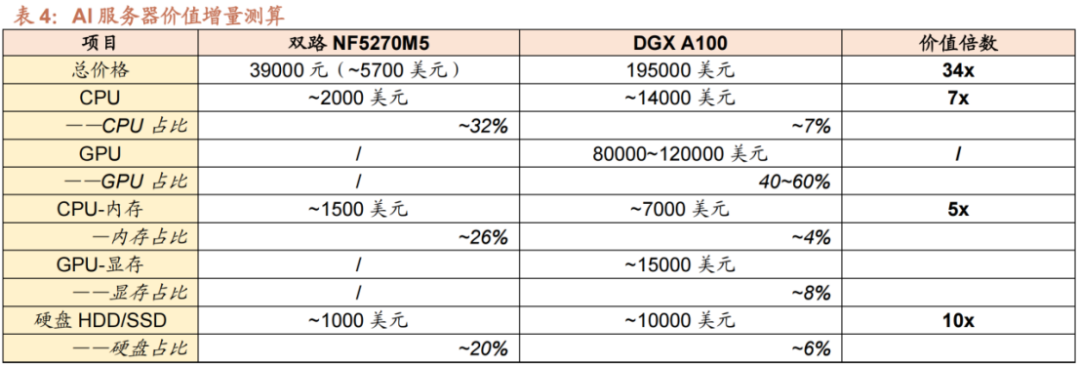

根据招商证券测算,从容量上看,按照普通服务器CPU内存320-640GB容量计算,AI服务器对DRAM容量的提升大约为4-8倍;按照高性能服务器CPU内存1TB容量计算,AI服务器对DRAM容量的提升大约为2.5-3倍。从价值量来看,AI服务器中CPU内存和SSD的价值量相较于普通双路服务器预计均提升5倍左右,GPU显存为纯增量市场。

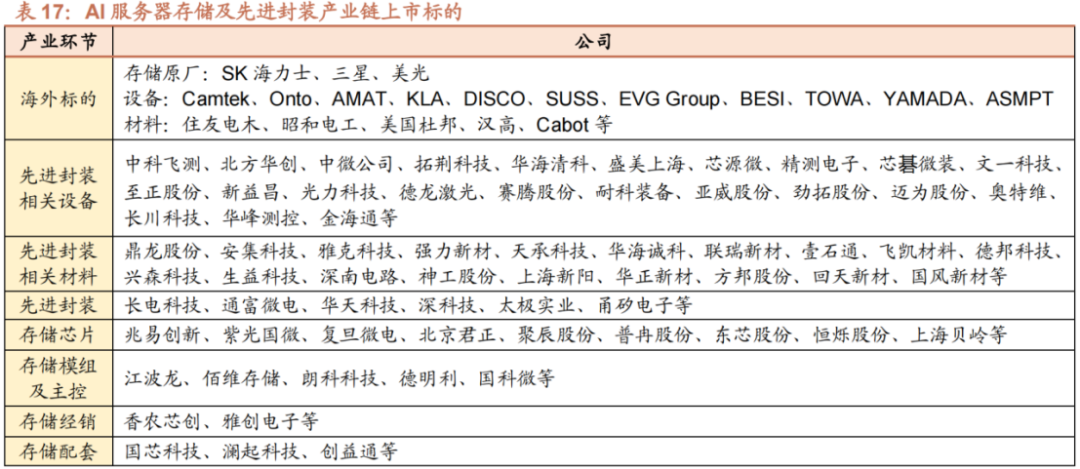

四、相关标的

1、存储芯片:兆易创新、北京君正、东芯股份

2、存储经销:香农芯创、雅创电子

3、AI服务器及HBM配套:国芯科技、澜起科技、创益通

附:AI 服务器存储及先进封装产业链上市标的

资料来源:中信建投电子、招商证券电子

审核编辑:汤梓红

-

@硬声小助手 浅谈国产存储芯片替换硬声何同学 2021-07-27

-

雷军都喊贵!存储芯片涨价风暴,手机电脑集体涨价#芯片#存储芯片#AIjf_15747056 2025-10-28

-

存储芯片入门漫谈2016-08-16 10769

-

存储芯片扇区2017-06-30 3642

-

存储芯片封装分类及作用是什么?2021-06-18 5364

-

存储芯片厂商有哪些_八大存储芯片厂商排名2018-04-08 116399

-

长江存储128层NAND flash存储芯片 中国存储芯片国际领先2020-04-14 15681

-

浅谈存储芯片分类及主要市场格局2023-04-06 6316

-

存储芯片的原理_分类及应用2023-06-02 19828

-

车载存储芯片介绍2023-06-09 2385

-

关于存储芯片必须要知道的一些基础知识!2022-07-26 5793

-

存储芯片是什么 存储芯片的分类及发展历史2023-07-07 19905

-

什么是存储芯片?有什么作用呢?2024-02-29 6357

-

存储芯片有哪些类型2024-07-24 11687

-

什么是DRAM存储芯片2026-01-13 1800

全部0条评论

快来发表一下你的评论吧 !