MCU厂商推荐的外围敏感电路设计

描述

一,晶振

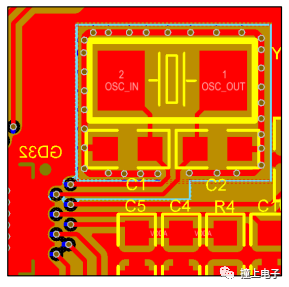

晶体要尽量靠近芯片Pin,远离诸如功率电感的磁感应器件与诸如天线的辐射器件,与同层其他信号走线利用GND铺铜及VIA隔离。晶体输入输出走线要尽可能短且少弯折,不可跨层或交叉走线。两边负载电容与晶体各自的GND和PAD可以相连,并摆放多个GND和VIA以提高散热保障。晶体下方尽量不走任何传输线,保留完整的GND铺铜。晶振电路走线以及匹配电容应该与晶振在同一侧,尽量不穿层。布局应该使晶振靠近MCU,晶振电路走线不能太长,不要超过12mm。在晶振同层以及下一层与其他电路间隔开,晶振电路周围也使用接地 VIA 形成保护环。

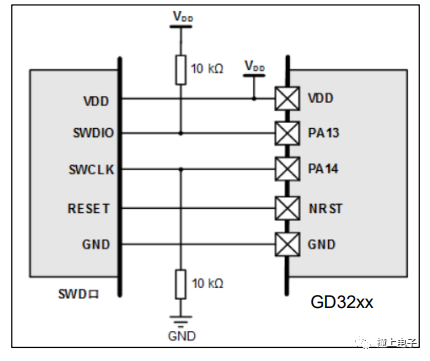

二,下载口

MCU的 SWD 烧录口走线应尽量短,远离板边 12mm。有以下几种方式可以提高SWD下载调试通信的可靠性,增强下载调试的抗干扰能力。缩 短SWD两个信号线长度,最好15cm以内;将SWD两根线和GND线编个麻花,缠在一 起;在SWD两根信号线对地各并几十pF小电容;SWD两根信号线任意IO串入100Ω~1KΩ 电阻。

三,复位电路

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是敏感电阻呢?敏感电阻包含哪些电阻器呢?2024-03-06 4247

-

通过Intel Curie进行运动敏感电路控制2023-06-19 704

-

IoT (Internet of Things)物联网 功能框图及外围电路设计2023-06-07 2204

-

DN497 - 为敏感电路提供过压及电源反接保护2021-03-19 1309

-

无需隔离二极管就可保护敏感电路的解决方案2021-03-18 716

-

什么是敏感电阻,敏感电阻的种类特点是什么2020-12-31 2507

-

什么是敏感电阻_敏感电阻种类特点2020-04-16 6008

-

低噪声硅微陀螺敏感电容电荷读出电路设计_卢月娟2017-03-19 696

-

电路设计--含有耦合电感电路的计算2017-02-28 1107

-

MCU电路设计经验2016-06-17 905

-

电压控制端的外围电路设计2015-12-25 960

-

怎么学习外围电路设计2012-10-21 2741

-

单片机外围电路设计2010-03-29 1258

全部0条评论

快来发表一下你的评论吧 !