低功耗仿真实战

描述

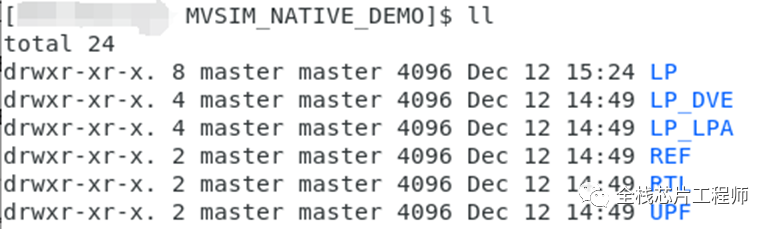

将MVSIM_NATIVE_DEMO文件夹拷贝出来,如下所示,LP、LP_DVE、LP_LPA文件夹分别存放的是仿真环境,REF文件夹是不带UPF的参考对比仿真环境,RTL和UPF文件夹分别用来存放设计代码和UPF文件。

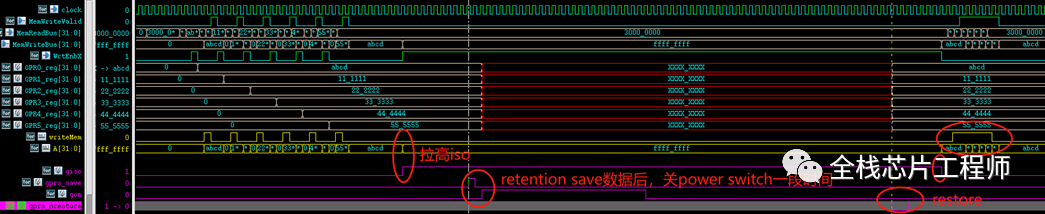

直接上干货,低功耗的关闭、打开仿真流程如下:

拉高isolation -> retention save -> 关闭power switch -> 打开power_switch-> retention restore -> 拉低isolation

仿真波形如下:

SoC训练营学员问为何低功耗cell没有插入网表?

虽然提问题是值得鼓励的,但是我们在遇到问题时,还是先主动思考,主动解决问题,实在解决不了我们再求助,这样成长更快。

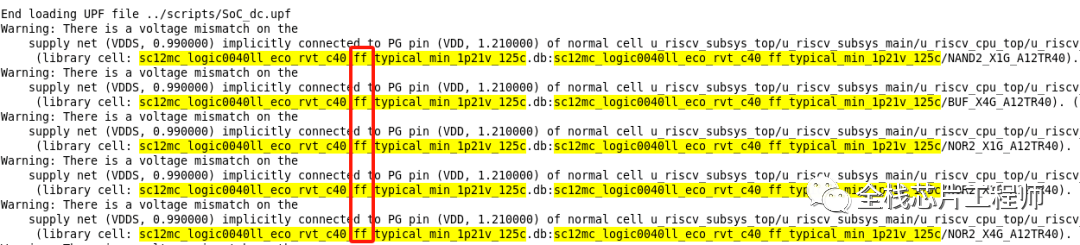

首先,小编拿到这问题,就打开log,查看log是一种IC设计美德!发现EDA工具吃进UPF文件后,报了warning如下,用到了很多ff库。

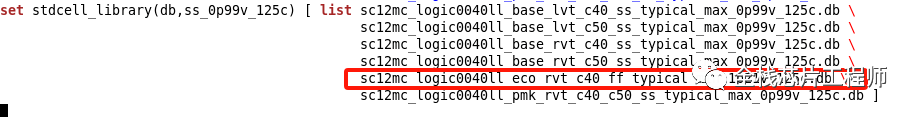

上图报错UPF指定电压是0.99V,而CELL是1.20V,电压不匹配,导致逻辑综合出来的网表没有插入MV CELL。注意,综合时,我们用的ss库,怎么会是ff库呢?打开约束脚本发现如下bug:

于是,更改约束,将ff换成ss即可。再次run一下,结果就出来了:

低功耗设计部分,设计里面我会留一点小bug在里面 非常简单,我不会公布答案,大家一定要多思考、多动手跑跑,这样才学的深刻。

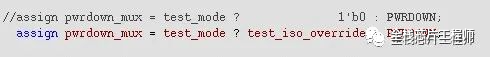

培训学员请注意,景芯SoC用always on的power domain电压域的pwrdown_mux信号作为power switch cell的switch控制信号,但是设计里面有个小问题,不太算bug的bug,但对upf低功耗flow而言,毫无疑问就是bug!

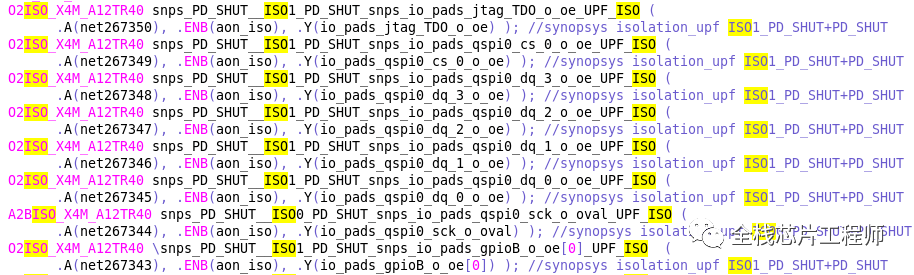

培训学员请登陆服务器追踪一下pwrdown信号,注意其负载情况,RTL代码如下:

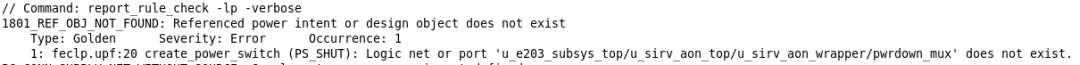

结合PR输出的netlist, 我们做个clp低功耗检查,脚本参见服务器。可以发现,clp报错说power switch的switch控制信号找不到。

不得不说,clp检查对低功耗而言多么重要,对芯片设计而言多重要!景芯SoC的价值就在把芯片设计全流程的这些细小的知识点,全部串接起来!犹豫啥?抓紧报名加入吧!

在芯片设计中端流程时,景芯SoC会插入UPF约束中的isolation等cell,但是无法插入power switch等cell,因此,作为power switch cell的控制信号pwrdown_mux在没有负载的情况下,会被裁员掉(优化掉),因此需要设置上面MUX器件为dont_touch或者使pwrdown_mux成为module的port并禁止auto_ungroup(并设置no_boundary_optimization),这样这个信号才能保留给后端,供后端实现power switch控制。

请学员完成代码修改,基于全套flow环境完成如下任务:

lint检查、前端仿真,

完成中端、后端flow,

完成clp检查, 完成后仿真

审核编辑:汤梓红

-

解锁物联网摄像头潜力:低成本低功耗硬件设计实战技巧!2025-09-20 1454

-

低功耗单片机怎么仿真?2023-10-20 563

-

STM32Lx低功耗实战设计2023-09-11 608

-

微型/超低功耗 E7 仿真器用户手册2023-05-05 439

-

投稿 | 基于IAR仿真RA低功耗2022-11-04 2287

-

#硬声创作季 #STM32 手把手教你学STM32-044 待机唤醒实验-低功耗-M4-2水管工 2022-10-29

-

电磁仿真实例教程2021-04-21 1211

-

ewb的仿真实例2016-07-26 1105

-

Zigbee低功耗管脚怎么设置2016-04-26 2747

-

Simulink建模仿真实例快速入门2015-12-28 2957

-

PSpice教程:PSpice仿真实践2013-04-07 2202

-

低功耗仿真实例-零基础学单片机视频教程-10讲2010-09-08 2522

-

PSpice仿真实践2006-03-12 10441

全部0条评论

快来发表一下你的评论吧 !