使用Cauer网络仿真热行为与对开关损耗影响的评估

描述

过去,仿真的基础是行为和具有基本结构的模型,它们主要适用于简单集成电路技术中使用的器件。但是,当涉及到功率器件时,这些简单的模型通常无法预测与为优化器件所做的改变相关的现象。现在,通过引入物理和可扩展建模技术,安森美(onsemi)使仿真精度进一步提升到更高的水平,此前我们为大家介绍了物理和可扩展仿真模型功能的相关内容,本文将继续为大家介绍使用 Cauer 网络仿真热行为以及评估各项因素对开关损耗的影响。

使用 Cauer 网络仿真热行为

所有仿真模型都可以使用两个(或更多)额外节点,借助热电等效关系提供有关热行为的信息。在此等效关系中,对于一个节点,电压代表温度,电流代表功率耗散。

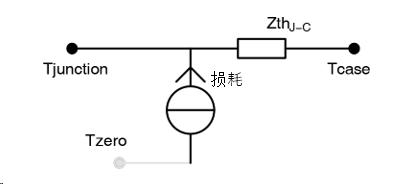

图 18. 内部热电结构

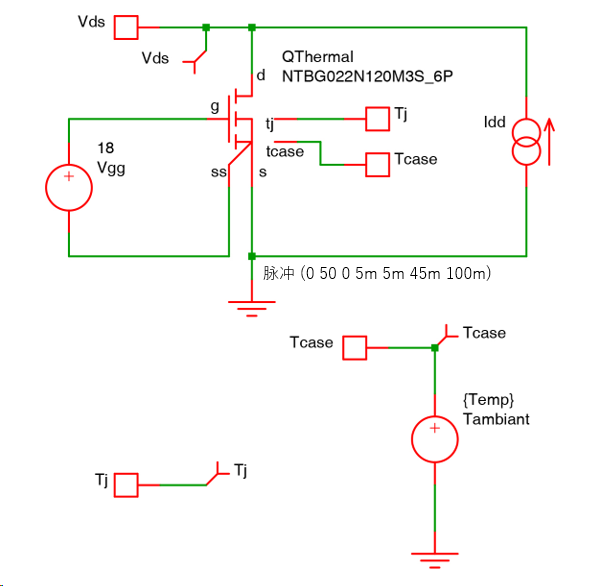

将 Tcase 引脚连接到固定电压源(应用的环境温度或最高外壳工作温度),我们可以获得外壳和结之间的温差。只需测量 Tj 引脚电压即可获得。(参见图 19)

图 19. 电-热简单方法

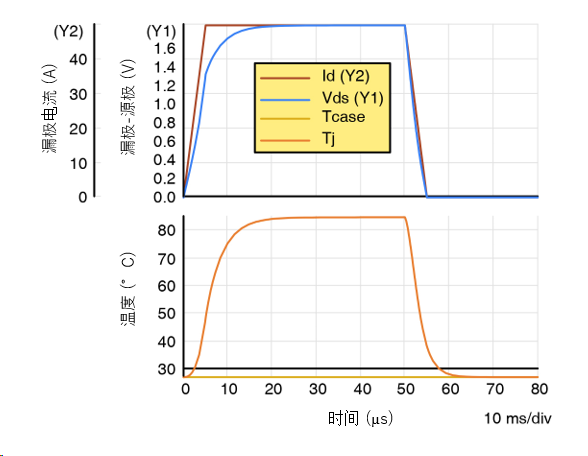

图 20. 结到外壳的温差

在上图中(图 20),我们使用电流脉冲来加热芯片。我们可以看到结温随着时间和芯片中功耗增加而升高。通过观察电流已经达到最大值时漏极-源极电压的缓慢斜率或指数斜率,还可以了解 RDS(on) 随温度变化的情况。

在下一个练习中,我们将使用一个 D2Pack-7 引脚封装的 SiC MOSFET,将其安装在 1 平方英寸接地平面(用作散热器)的印刷电路板 (PCB) 上。

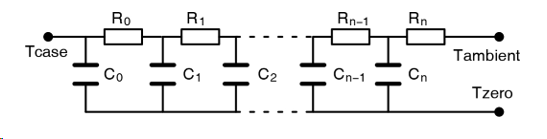

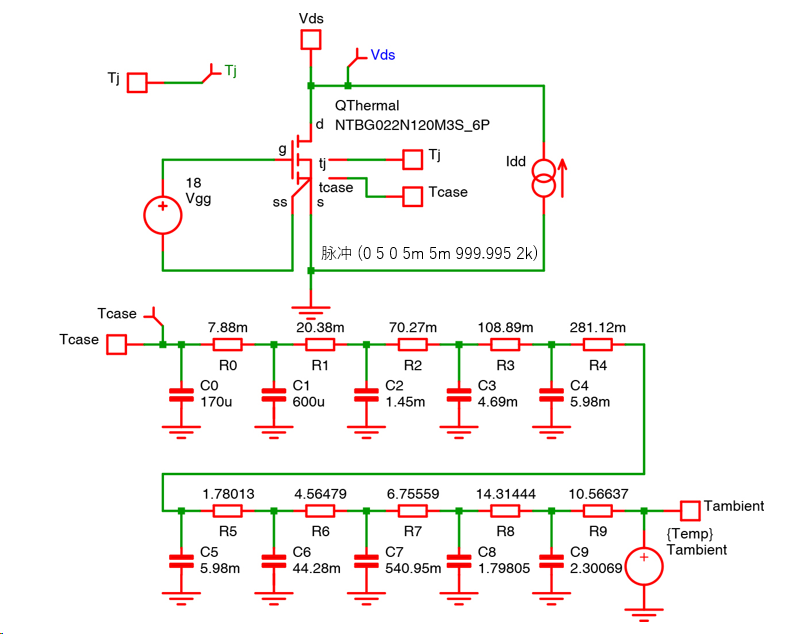

较复杂的部分是找到代表此 PCB 散热器动态性能的 Cauer 网络(图 21)。为了获得此网络,我们安森美使用有限元仿真工具对组装进行建模,提取其性能数据及等效 Cauer 网络。下面的原理图给出了我们将使用的等效 RC 网络。

图 21. 1 平方英寸 PCB 的 Cauer 网络

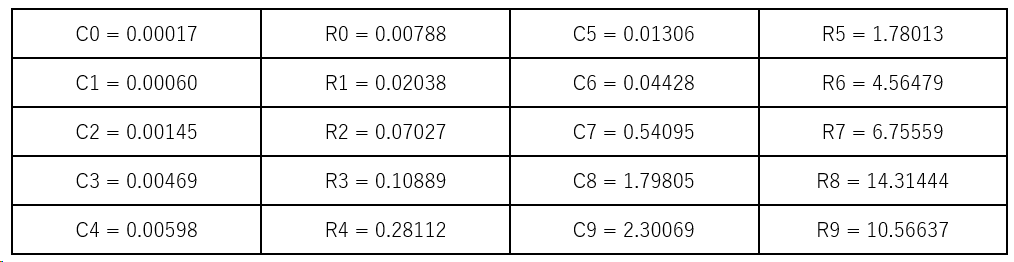

表 1 提供了 1 平方英寸 PCB 的网络值。

表 1.1 平方英寸 PCB 散热器的 Cauer 网络值

然后,我们在仿真原理图中加入该网络,并将其与额外的“热”节点连接,如图 22 所示。

图 22. Cauer 网络仿真原理图

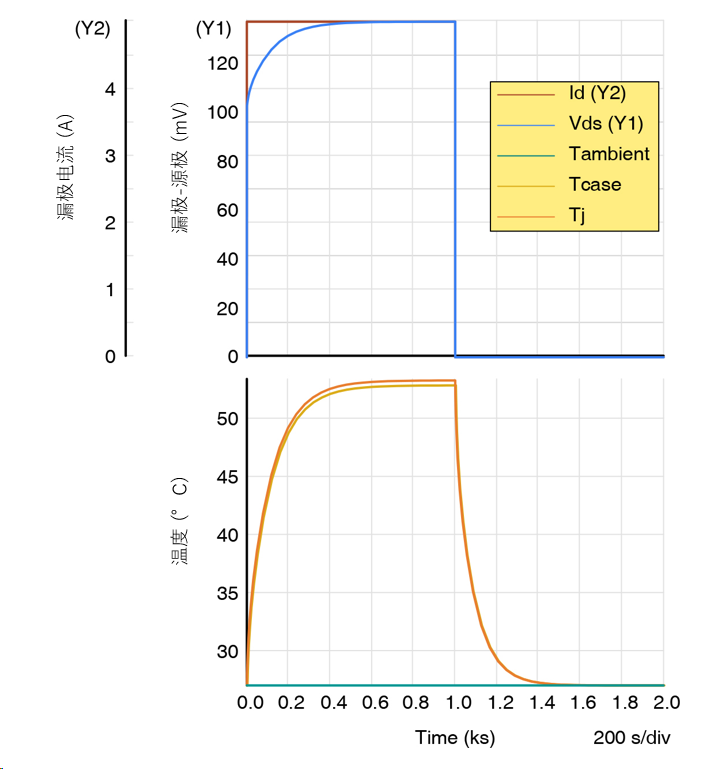

现在,我们可以运行仿真并查看散热器如何散热。我们不仅可以读取壳温和结温,还可以绘制仿真模型所提供的结和外壳节点的电压曲线(参见图 23)。

图 23. 热电仿真结果

栅极、驱动和电压电平对开关损耗影响的评估

在本小节中,我们将采用具有不同封装的同一芯片。为了评估封装寄生效应的影响,我们将比较开关损耗。

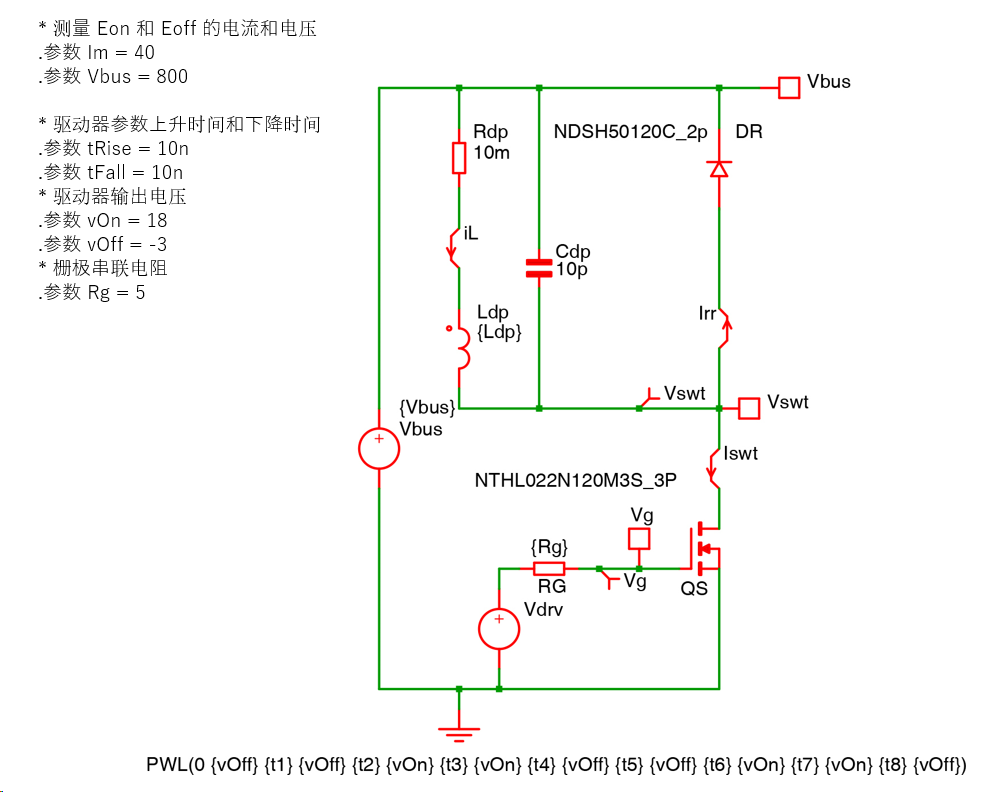

众所周知,双脉冲测试仪(图 24)可用来测量开关性能,它可以提取开关事件中的导通和关断能量。由于续流大多存在于短路状态,因此电流值在关断事件和导通事件之间几乎保持不变。

图 24. 双脉冲测试仪仿真原理图

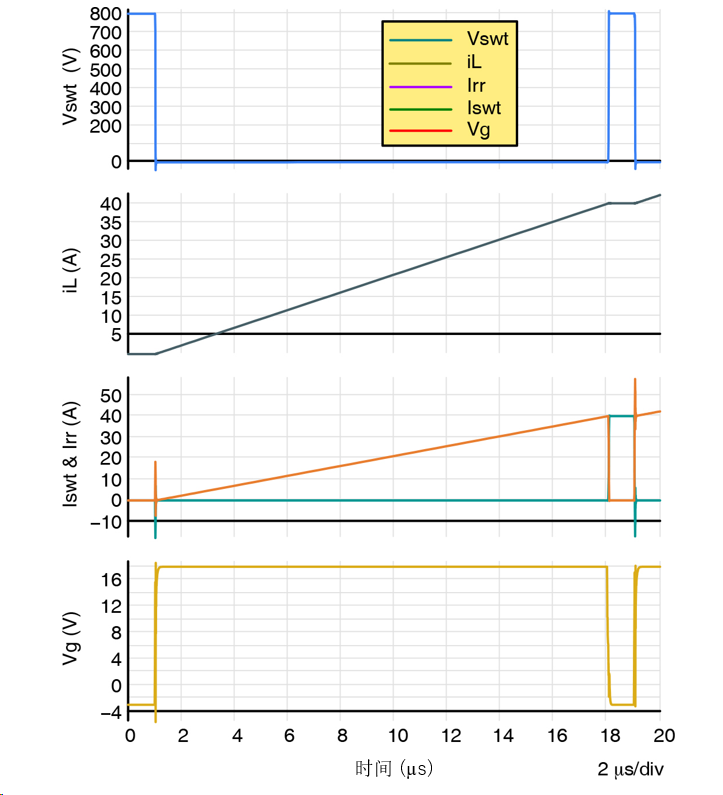

运行此测试仪仿真将获得下面图 25 中绘制的波形。

图 25. 双脉冲测试波形

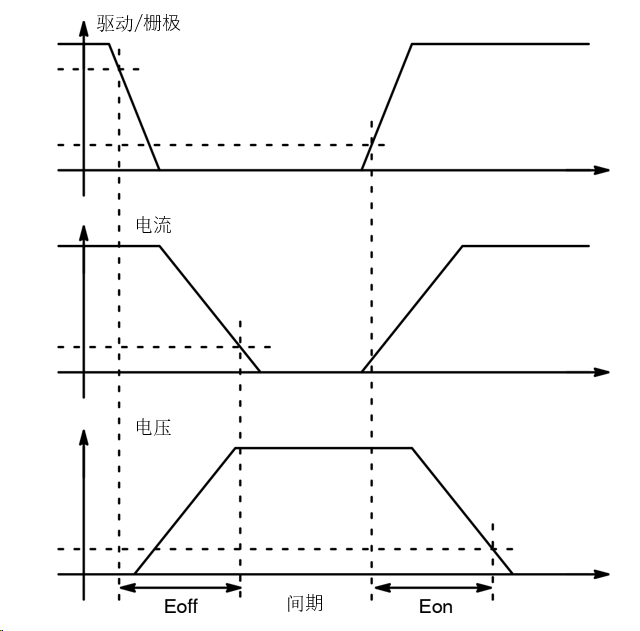

为了测量开关损耗和所有参数(如导通延迟和上升时间等),我们使用下面图 26 中所示的约定时序。

图 26. 导通和关断能量测量

我们可以直接在原理图上使用一些其他公式计算损耗,并使用光标进行测量。但是,如需多次执行此操作,建议创建一个简单的执行脚本。

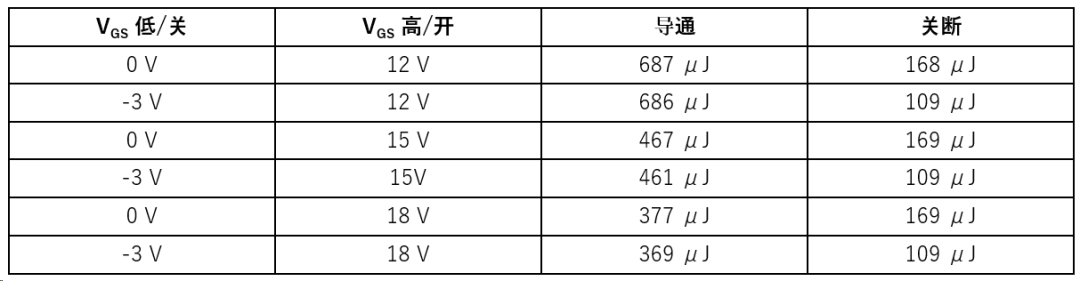

我们将查看几个栅极电压最小值和最大值,以了解其在相同设置下对开关损耗的影响。

我们将不讨论 RDS(on) 随栅极电压的变化——这部分在数据手册的导通区域曲线图中已涵盖。

使用新一代 NTH4L022N120M3S(22 mΩ,1200 V,M3S)MOSFET 和 5 Ω 外部栅极电阻及 NDSH50120C(50 A,1200 V,D3)二极管,我们获得下表中列出的数值。总线电压设置为 800 V,电感电流为 40 A。表 2 显示了如下结果。

表 2.不同栅极驱动电压的导通和关断能量

正如预期,在导通期间增加栅极电压会降低导通损耗,对关断损耗几乎没有影响。同样与预期一致的是,在关断期间提供负栅极电压可降低关断损耗,对导通损耗的影响可以忽略不计。

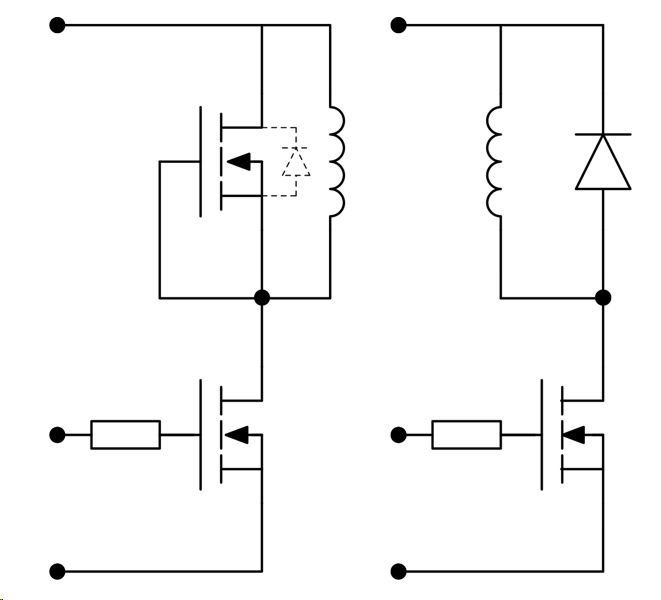

评估半桥结构对开关损耗的影响

在本小节中,我们将始终采用同一器件作为低压侧开关,改变高压侧器件,了解该高压侧器件如何影响低压侧器件的损耗。实际上,双脉冲测试仪测量是在低压侧开关上进行的,因为驱动低压侧开关并在低压侧进行测量更容易实现,而在高压侧测量将获得相同的结果。

通常,有两种类型的 SiC 二极管:肖特基或 P-N 结。肖特基是分立器件,而 P-N 结是 SiC MOSFET 的体二极管(参见图27)。我们将分析这两种二极管类型的开关损耗。

图 27. 半桥和四分之一桥结构

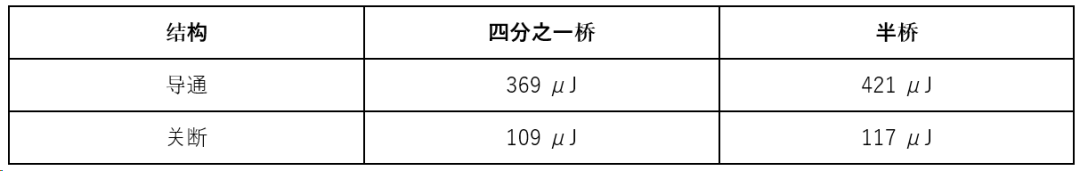

使用新一代 NTH4L022N120M3S(22 mΩ,1200 V,M3S)MOSFET,并采用相同的设置,5Ω 外部栅极电阻,总线电压设置为 800 V,电感电流设置为 40 A,我们获得表 3 中的结果。续流器件的半桥架构使用相同的器件,四分之一桥架构则使用新一代 NDSH50120C(50 A,1200 V,D3)。

表 3.相同芯片尺寸的导通和关断能量(10 m,1200 V,M3S)

正如预期,使用 SiC 肖特基二极管,其电容和反向电流效应(或损耗)比 P-N SiC 体二极管恢复效应(或损耗)小得多,此时的 SiC MOSFET 开关损耗要低于使用一个独立的 SiC 二极管。

评估封装对开关损耗的影响

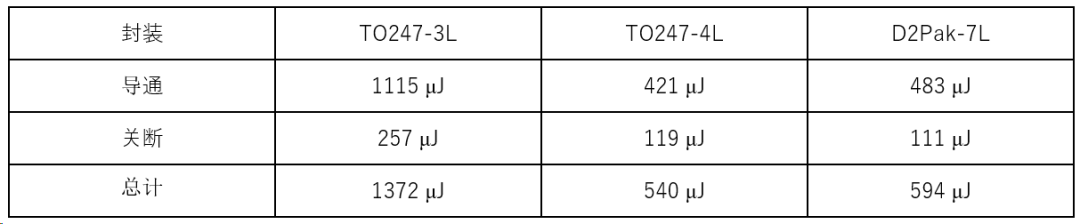

我们将查看采用不同封装具有相同 RDS(on) 的器件的损耗。我们将采用半桥架构以及与之前相同的条件,在高压侧使用相同的器件。表 4 显示了结果。

表 4.相同 RDS(on)(22 mΩ,1200 V,M3S)器件的导通和关断能量

TO247-4L 封装比较理想,具有低寄生损耗。但是,由于 D2Pak-7L 的寄生(或引脚 + 键合)电感比 TO247-4L 小,特别是在漏极侧,这些较低的电感会导致导通期间的漏极电流增加得更快,漏极-源极电压下降得更慢,所以导致 D2Pak-7L 的损耗将更高。

数据手册值高于此处的测量值,因为实际测试设置比这个简易仿真中的寄生效应更多,所有额外的寄生效应都会影响导通和/或关断期间的损耗。

审核编辑:汤梓红

-

基于LTSpice的GaN开关损耗的仿真2025-03-13 3046

-

影响MOSFET开关损耗的因素2024-09-14 2774

-

使用仿真模型进行拓扑分析2024-01-05 2187

-

MOS管的开关损耗计算2023-07-23 6599

-

DC/DC评估篇损耗探讨-同步整流降压转换器的开关损耗2023-02-23 2105

-

PFC MOSFET的开关损耗测试方案2022-10-19 2937

-

准确测量开关损耗的几个方式2021-11-18 4300

-

开关损耗原理分析2021-10-22 1589

-

如何更加深入理解MOSFET开关损耗?2021-04-07 3483

-

【干货】MOSFET开关损耗分析与计算2021-01-30 5493

-

全SiC功率模块的开关损耗2018-11-27 4778

-

基于CMM下开关损耗和反激开关损耗分析以及公式计算2018-01-13 11034

-

开关损耗测试在电源调试中重要作用2017-11-10 7243

-

MOSFET开关损耗分析2016-01-04 994

全部0条评论

快来发表一下你的评论吧 !