服务器架构:内存接口及互连芯片

存储技术

描述

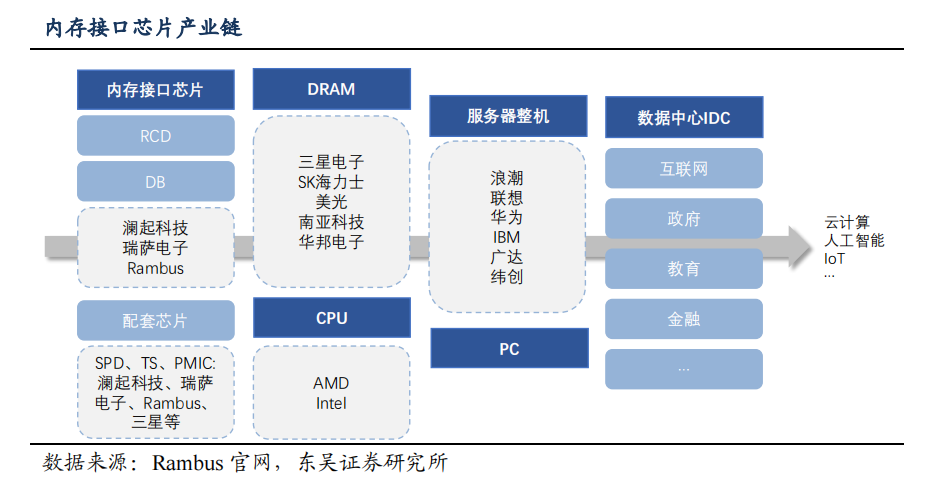

本文来自“深度报告:从Rambus看内存接口芯片机会”。CPU 和 DRAM 是服务器的两大核心部件,内存接口芯片集成于 DRAM 模组中,是服务器内存模组的核心逻辑器件,其主要作用是提升内存数据访问的速度及稳定性,满足服务器 CPU 对内存模组日益增长的高性能及大容量需求。由于 CPU 比内存处理数据速度快,因此需添加接口芯片以满足 CPU 对运行速度、信号完整性和稳定性方面要求。

由于内存接口芯片的大规模商用要经过下游厂商的多重认证,还要攻克低功耗内存接口芯片的核心技术难关,从 DDR4 世代开始,全球内存接口芯片厂商仅剩 Rambus、澜起科技和瑞萨(原 IDT)三家厂商。

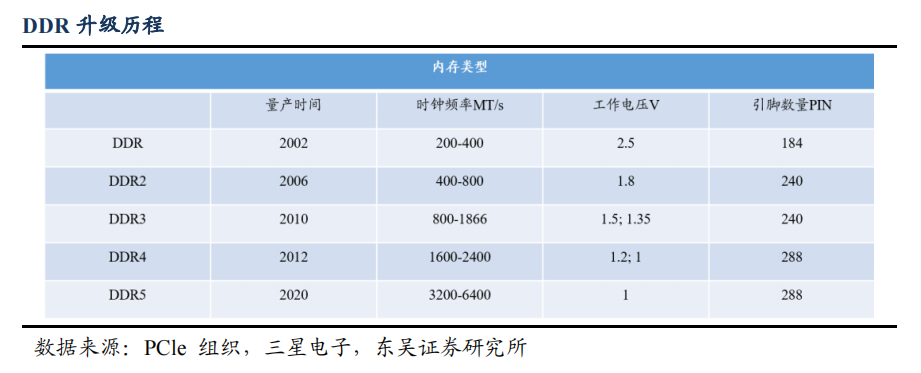

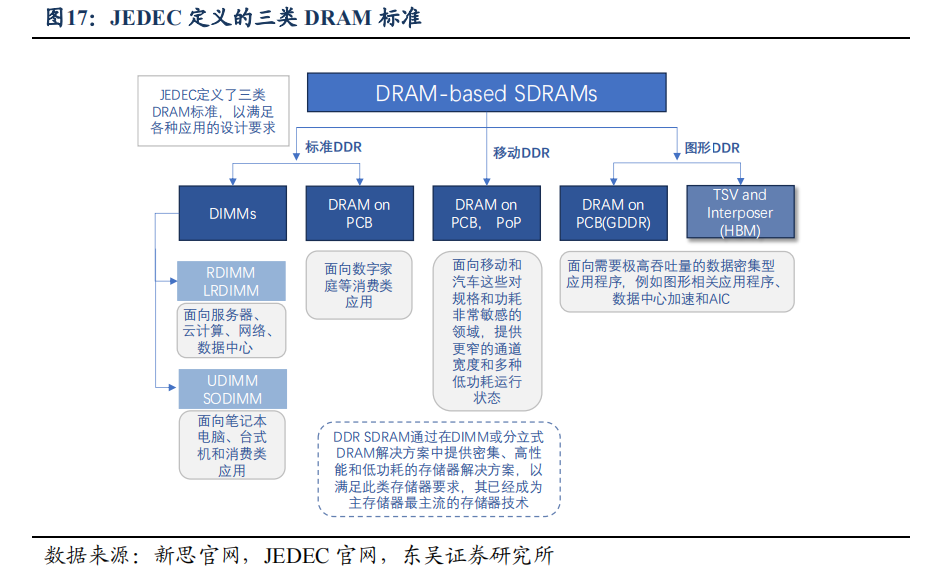

DRAM 由于其结构简单,设计体积小,在服务器的内存中占主导地位,并得到了长足的发展,从 DRAM 逐渐演进到 SDRAM 再到 DDR SDRAM 系列。SDRAM为同步的动态随机处理器,同步指的是存储器的工作参考时钟,SDRAM 只能在信号的上升沿进行数据传输,其内核工作频率、时钟频率和数据传输速率三者相同,最高速率可达 200MHz。DDR SDRAM(Double Data Rate Synchronous DRAM)双倍速率同步动态随机存储器,可以在信号的上升沿和下降沿都进行数据传输,所以 DDR 内存在每个时钟周期都可以完成两倍于 SDRAM 的数据传输量。随着人工智能大热,各云服务内存数据的传输速率越来越跟不上 CPU 算力的发展。为了提高内存数据传输速率、减小功耗,DDR SDRAM 也逐代演变出了 DDR1-DDR5 系列。

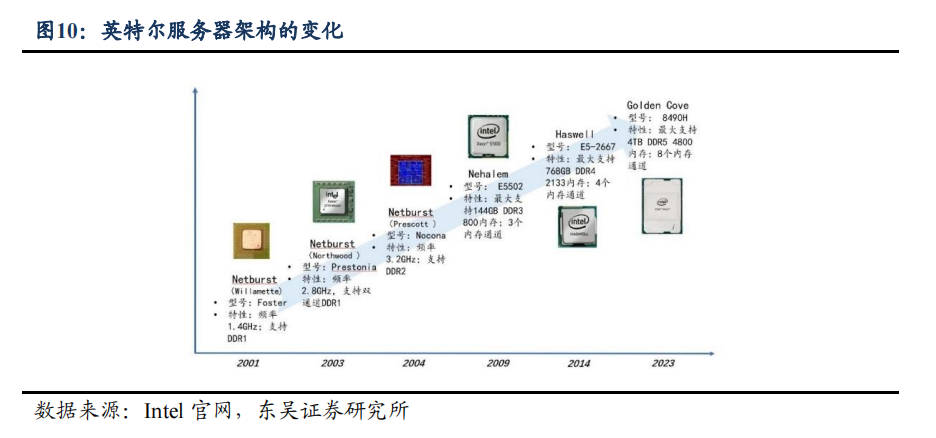

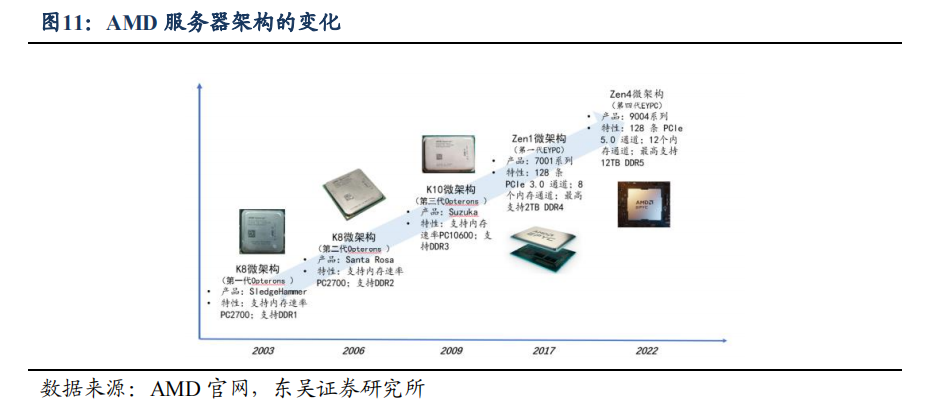

全年来看,新一代服务器 CPU 的推出有望刺激服务器换机需求。CPU 作为服务器进行运算处理的核心“大脑”,是影响服务器性能的最重要硬件之一。Intel 和 AMD 作为服务器市场两大巨头接连在今年推出支持DDR5 的最先进服务器,Intel 最新推出的第四代至强(XEON)处理器 8490H 和 AMD推出的第四代霄龙(EYPC)处理器分别支持 8 通道 DDR5 和 12 通道 DDR5。

通常每一代 DDR 在上量后第一年末渗透率可达到 20-30%左右,第二年末渗透率可达到 50-70%左右,第三年末基本上就完成了市场绝大部分的渗透。虽然 2022 年 DDR5的渗透率不及预期,但是预计 2023 年后将进入快速放量期,预计 2023 年 DDR5 在服务器部署方面的比例将不足 20%,到 2025 年将达到 70%左右。

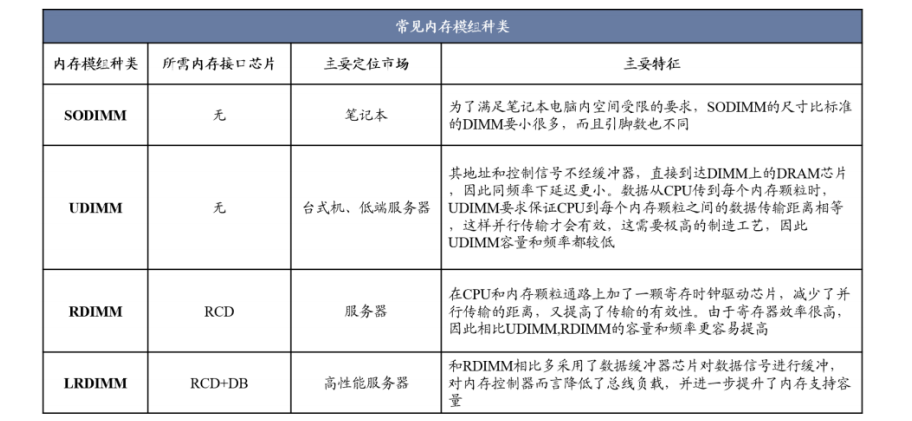

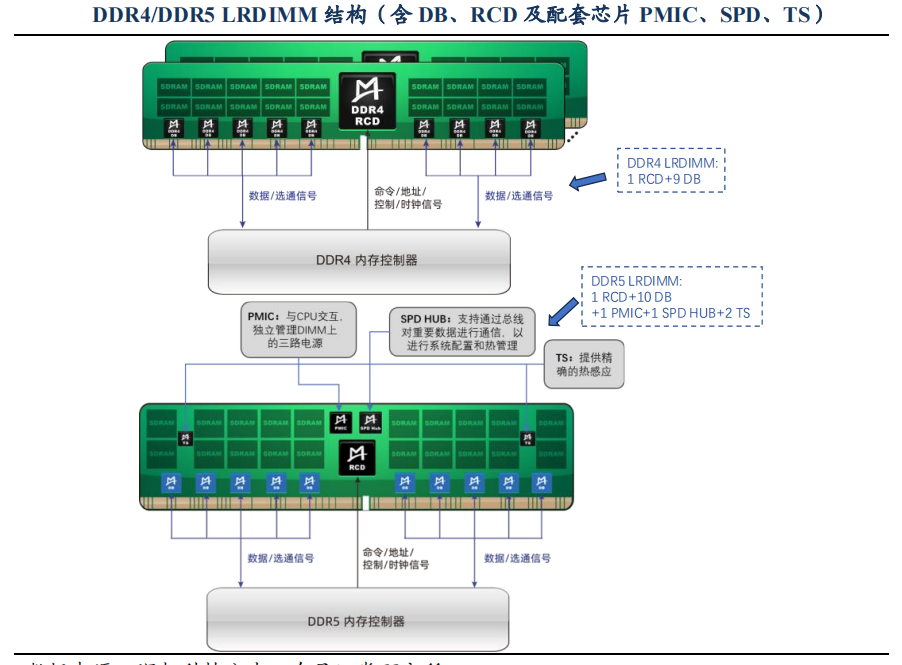

内存接口芯片按功能可分为两类,一是寄存缓冲器(RCD),用来缓冲来自内存控制器的地址/命令/控制信号;二是数据缓冲器(DB),用来缓冲来自内存控制器或内存颗粒的数据信号。仅采用 RCD 芯片对地址/命令/控制信号进行缓冲的内存模组通常称为RDIMM,而采用了 RCD 和 DB 套片对地址/命令/控制信号及数据信号进行缓冲的内存模组称为 LRDIMM。

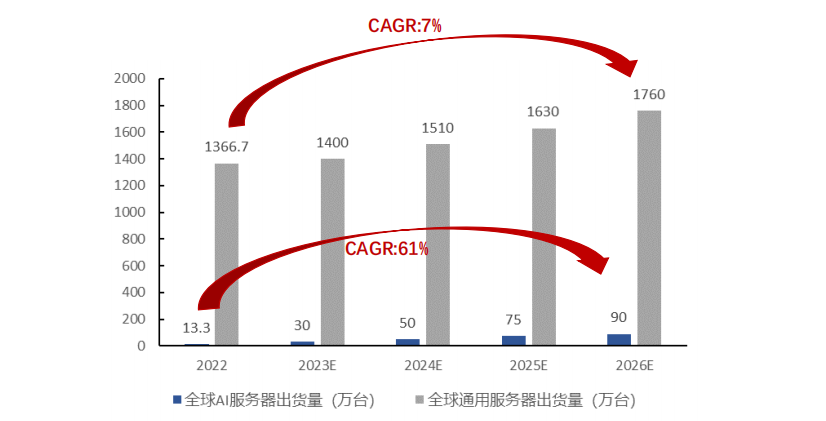

1)服务器需求回升,单台服务器 CPU 配置提高。根据 IDC 数据,全球服务器市场在经历了 2019-2021 年的持续低迷期后迎来反弹,2022 年全球服务器出货量达到 1380万台。服务器可分为 AI 服务器和通用服务器,其中 AI 服务器起步较晚,但是增速惊人,2022 年 AI 服务器出货量约为总体的 1%,预计 2023-2025 年可以实现 60%左右的 CAGR;通用服务器预计后续实现平稳增长,CAGR 预期为 7%左右。

同时,大模型的出现导致对服务器的算力要求大幅提升,单个服务器 CPU 数量也因此增长。今年最新发布的联想 ThinkSystem SR850 和浪潮服务器 NF8480M5 已经实现标配 4 颗 CPU,最大配置 8 颗 CPU,而中科曙光的服务器标配和最大配置 CPU 数量均达到 8 颗,相比 2016 年联想服务器标配和最高配置CPU数量仅 1 颗已有明显提升。

2)内存接口芯片进入替换周期,DDR5 升级带来 DB 芯片及内存模组配套芯片增量需求。内存接口芯片最主要的下游应用是服务器,自从 2020 年 JEDEC 提出 DDR5 规范标准以后,各大服务器厂商开始计划推出兼容 DDR5 的新平台。在 DDR4 世代,LRDIMM 内则通常配置 1 颗 RCD+9 颗 DB;根据 DDR5 标准,LRDIMM 内将配置 1 颗RCD 和 10 颗 DB,此外需要配套一个串行检测芯片(SPD)、一个电源管理芯片(PMIC),以及 1-3 个温度传感器(TS)。DDR5 内存模组首次采用电源管理芯片(PMIC)以提升电源管理效能。DDR5 的渗透率不断提升带来了 DB 芯片和内存模组配套芯片新的增量需求。

3)DDR5 子代迭代速度加快,内存接口芯片均价有望维持稳定。在某一代具体产品周期中,销售单价逐年降低,但新的子代产品在推出时的单价通常高于上一子代产品。澜起科技 DDR4 世代每个子代的迭代周期约 18 个月左右,而 DDR5 世代子代迭代周期缩短,有利于保持稳定的 ASP 水平。

高带宽存储器(High Bandwidth Memory,HBM)是 AMD 和 SK 海力士发起的一种基于 3D 堆栈工艺的高性能 DRAM,适用于高存储器带宽需求的应用场合,如图形处理器、网络交换及转发设备(如路由器、交换器)等。

目前在 HBM2E 规范下,当传输速率上升到每管脚 3.6Gbps 时,HBM2E可以实现每堆栈 461GB/s 的内存带宽。此外,HBM2E 支持 12 个 DRAM 的堆栈,内存容量高达每堆栈 24GB。

这种新型的 CPU/GPU 内存芯片是垂直堆叠而成,再由“中介层(Interposer)”连接至 CPU/GPU,这种设计使信息交换时间大幅缩短,只需将 HBM 堆栈插入中介层并放置于 CPU/GPU 旁边,再将其连接至电路板即可。HBM 所具备的功能特性与芯片集成的DRAM 几乎无异,且垂直堆叠的特殊设计使 HBM 具有功耗、性能、尺寸等多方面优势。

CXL 具有的高兼容性和内存一致性使其迅速取代传统数据中心环境中的 PCIe,成为行业内最领先的互联标准。在兼容性方面,CXL 标准在接口规格上可兼容 PCIe5.0,能够被现有支持 PCIe 端口的处理器(绝大部分的通用 CPU、GPU 和 FPGA)所接纳,且能够解决 PCIe 在内存使用效率、延迟和数据吞吐量上的缺陷,因此英特尔将 CXL 视为在 PCIe 物理层之上运行的一种可选协议,在 PCIe 6.0 标准上大力推进 CXL 的采用。

在内存一致性方面,CXL 可在 CPU,以及 GPU、FPGA 等之间建立高速且低延迟的互连,维护 CPU 内存空间和连接设备上的内存之间的内存一致性,允许 CPU 与 GPU之间绕过 PCIe 协议,用 CXL 协议来共享、互取对方的内存资源。透过 CXL 协议,CPU 与 GPU 之间形同连成单一个庞大的堆栈内存池,CPU Cache 和 GPU HBM2 内存犹如放在一起,有效降低两者之间的延迟,故此能大幅提升数据运算效率。

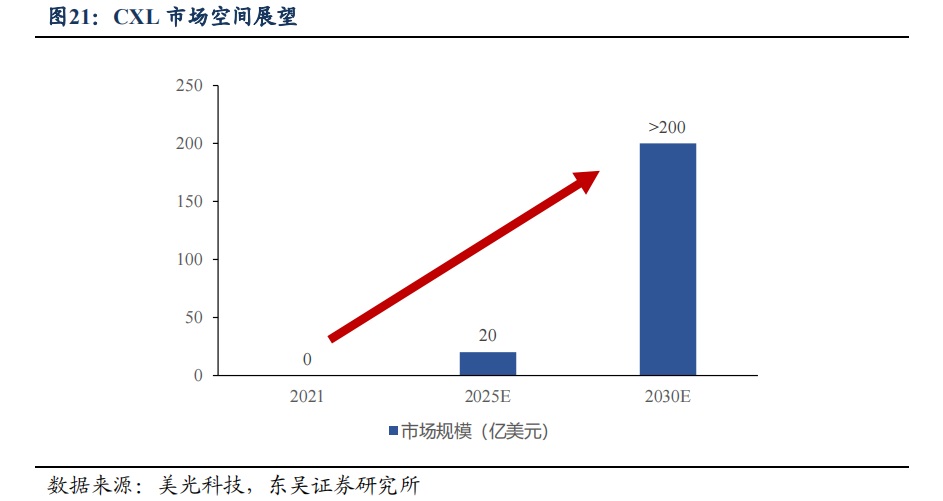

在 AMD、ARM、IBM 以及英特尔等主要 CPU 供应商的支持下,CXL 已经成为领先的行业标准。CXL 技术未来市场潜力较大。根据美光科技在 2022 年 5 月召开的投资人说明会资料,受异构计算快速发展的驱动,2025 年 CXL 相关产品的市场规模可达到 20 亿美元,到 2030 年超过 200 亿美元。

PCIe 总线是当前最流行传输总线,具有传输速度快,兼容性、拓展性强的特点。由于硬件数据交互传输速度要求日益提升,驱动传统并行总线向高速串行总线的过渡,PCIe 相比以往 PCI、AGP、PCI-X 具有更快传输速率,得到广泛认可,并且正在不断迭代升级,朝着更高传输速率方向发展。从兼容性来看,以硬盘为例,PCIe 总线支持 AHCI、NVMe 和 SCSI 协议,有 SATA Express、M.2、PCIe、U.2 等多种接口,具有兼容性、拓展性强等特点。无线网卡、有线网卡、声卡、采集卡、转接卡等设备均可以直接插入插槽。

伴随 PCIe 标准升级,总线传输速率几乎翻倍提升,同时带来严重信号衰减。主板PCIe 通道分为 x1、x2、x4、x8 和 x16 等多种配置,通道数量越多意味着带宽越高,传输速度越快。同时每一代 PCIe 标准升级,其传输速度几乎翻倍上升,从 PCIe 4.0 到PCIe 5.0,传输速度由 16GT/s 提升至 32 或 25GT/s,而整个链路插损预算从 4.0 时代的 28dB,增长到 5.0 时代的 36dB。信号衰减将限制超高速数据传输协议在下一代计算平台应用范围。

审核编辑:黄飞

-

RISC架构服务器简介2009-11-13 7075

-

回收服务器内存条 收购服务器内存条2021-01-07 965

-

高价收购服务器内存条,服务器内存条优势回收2021-09-22 1056

-

高价回收服务器内存条,专业收购服务器内存条2021-11-02 979

-

服务器内存2009-12-17 478

-

Rambus公司新推出服务器内存接口芯片组2015-08-27 2398

-

全内存转发服务器2017-01-04 481

-

什么是无服务器?无服务器架构的安全需要注意什么2019-09-28 4355

-

服务器内存的详细介绍2021-01-03 3004

-

阿里Arm架构服务器芯片或于近期发布2021-10-18 4338

-

站群服务器需要多大内存2024-03-04 1038

-

接口测试怎么测多个服务器连接2024-05-30 1352

-

ai服务器是什么架构类型2024-07-02 3732

-

从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析2026-01-20 1849

-

IDT:服务器内存接口芯片组的领导者2026-04-12 422

全部0条评论

快来发表一下你的评论吧 !