ChannelExpert平台如何对DDR信号进行时域眼图仿真分析

描述

前言

随着云计算、互联网和物联网的快速发展,电子产业在半导体技术的推动下,产品的功能不断增强,集成度不断提高,信号速率不断加快,产品的研发周期也日益缩短。由于电子产品持续向小型化、精密化和高速化发展,高速通道的设计需要全面考虑从发送端、过孔、传输线到接收端的整个通信链路,并支持对Buffer模型(IBIS/AMI)、S参数、传输线模型和Spice模型等的精确仿真。

ChannelExpert提供了一种快速、准确且简单的方法来分析、评估和解决高速通道信号完整性问题,并内置了业内先进的时域仿真引擎Xspice、2D传输线求解器、卷积求解器以及高级分析模块。

本文主要使用芯和半导体ChannelExpert平台演示如何对DDR信号进行时域眼图仿真分析,从而提升通道的整体性能。

ChannelExpert平台简介

芯和半导体的ChannelExpert平台支持:数字电路拓扑抽取、高速串Serdes通道分析、DDR通道分析以及串扰前仿真等。

DDR仿真流程可以通过bus形式构建拓扑,进行瞬态、PDA、统计、卷积分析,支持并行总线的IBIS-AMI仿真。

Serdes统计眼图分析,内嵌统计眼图仿真引擎,快速获得准确的BER和浴盆曲线。

层次化原理图支持用户对所有感兴趣的参数进行高级分析,如扫描、调谐、优化、Yield和DOE分析。

支持灵活的后处理与结果分析,内嵌的画图模块可以方便显示S参数、v/t曲线和眼图等。

支持Python脚本录制与回放功能。

ChannelExpert

DDR BUS时域眼图仿真分析流程介绍

DDR信号的通道仿真主要分析数据和地址控制命令信号;数据信号的仿真又分为写操作和读操作。本流程以数据信号的写操作仿真流程演示。

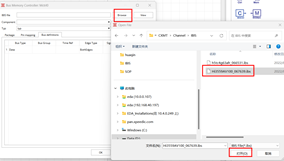

1.新建Channel仿真工程

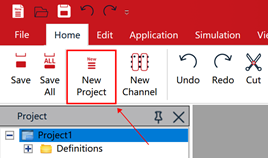

打开ChannelExpert软件,点击Home菜单栏下的NewProject,选择工程存放路径,点击“选择文件夹”,新建工程Project1;点击New Channel,生成Channel1仿真工程。

图1

新建Channel仿真工程

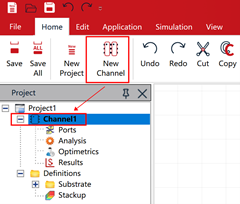

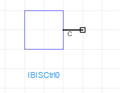

2.DDR Ctrl IBIS Model导入和Bus设置

右侧Components窗口,Type下拉框选择DDR,点击IBISCtrl图标,按住左键拖拽到编辑框内。双击模块进入模型导入对话框,点击Browse选择要导入的IBIS Model,点击“打开”,完成模型导入 。

在Bus definitions栏分别定义Bus Group、Time Ref、Signal Names,点击OK,完成Ctrl端模型及Bus设置。

图2

DDR Ctrl IBIS Model导入和Bus设置

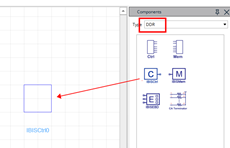

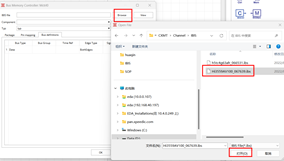

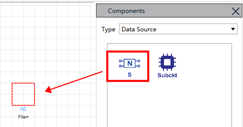

3.S参数模型导入

右侧Components窗口,Type下拉框选择Data Source,点击S参数图标,按住左键拖拽到编辑框内。双击模块进入S参数调用对话框,点击Browse选择要导入的S参数,点击“打开”,点击OK导入S参数。

图3

S参数 Model导入

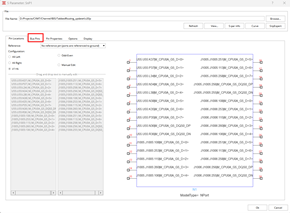

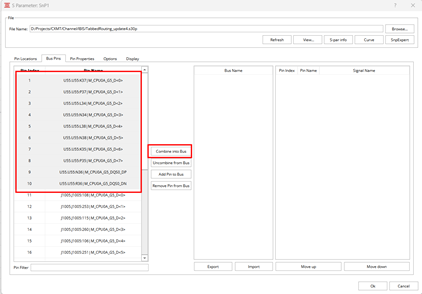

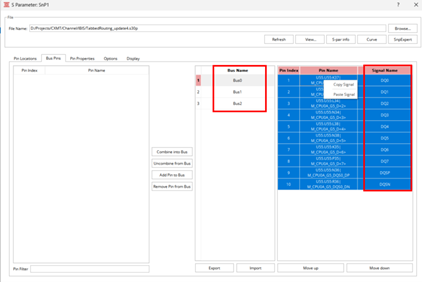

点击Bus Pins,进入Bus设置界面。左侧同时选中同一器件的同一Byte信号,包含DQS,点击“Combine into bus”完成一组Bus设置。设置完成可以对Signal Name重命名,方便后续查看信号。完成重命名后,选中全部信号,右键选择Copy Signal,分别点击其他Bus,在Signal Name栏右键选择Paste Signal,完成所有Bus信号的重命名。

点击OK,完成Bus设置。

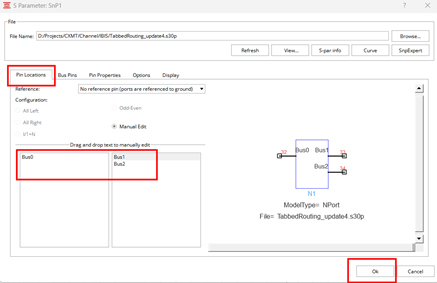

在Pin Locations中可以通过拖拽完成Bus的连接方向的改变,点击OK完成。

图 4

S参数Bus设置

4.Memory IBIS Model导入和Bus设置

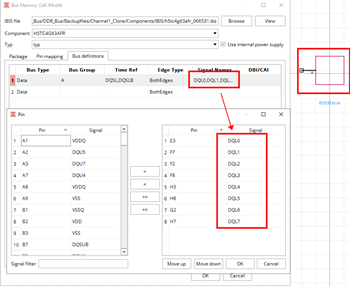

右侧Components窗口,Type下拉框选择DDR,点击IBISMem图标,按住左键拖拽到编辑框内。双击模块进入模型导入对话框,点击Browse选择要导入的IBIS Model,点击“打开”,完成模型导入。

在Bus definitions栏分别定义Bus Group、Time Ref、Signal Names,点击OK,完成Memory端模型及Bus设置。

图 5

Memory 端Bus设置

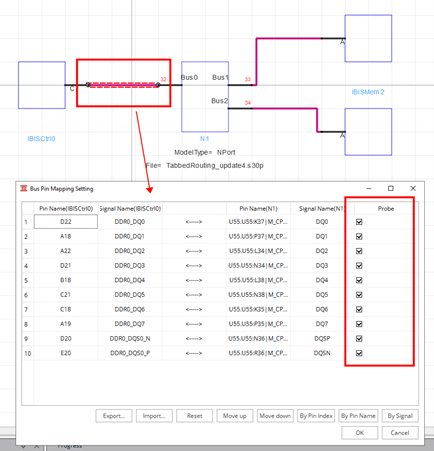

5.仿真链路搭建

点击菜单栏“Wire”连接电路,或拖拽模块使两个模块的引脚靠近也可以自动完成电路的连接。双击“Bus”互连线,可以显示信号的连接关系。点击Probe或者其下方的方块,可以全部选择或部分选择查看信号的波形。不勾选Probe选项软件默认也会输出接收端的波形。

图6

仿真链路搭建

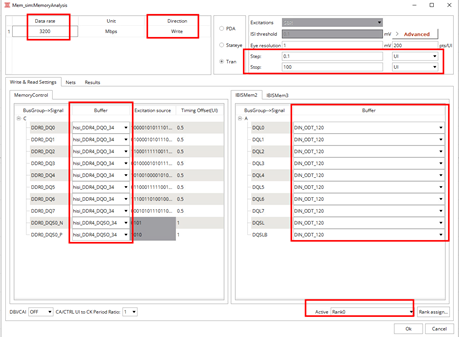

6.求解设置

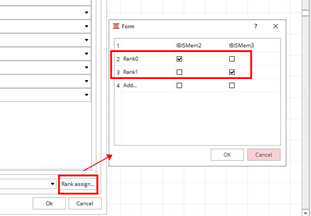

在左侧工程树Analysis处右键选择Add Memory Analysis仿真器,该仿真器支持Tran、Stateye、PDA三种分析模式。这里以Tran仿真为例,设置好求解步长和仿真时间。设置好信号速率和读写方向。设置好Control和Memory端的模型。

定义好Rank的数量,设置好Active Rank。点击OK,完成求解设置。

图7

求解设置

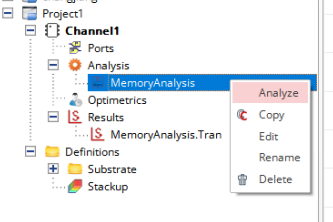

7.求解分析

工程树MemoryAnalysis处右键,选择Analysis,软件运行求解分析。

图 8

求解分析

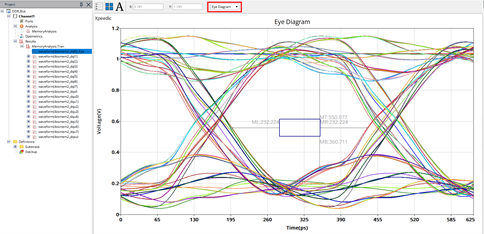

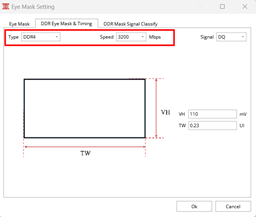

8.仿真结果查看及测量

仿真结束后会自动生成波形,点击左侧工程树Results下的TranAnalysis可以查看仿真波形。点击上方V-T右侧小三角,可以选择V-T和EyeDiagram的视图切换。眼图视图下,右键Measure->Configure Eye可以完成信号速率等设置。右键选择Measure还可以完成眼罩的添加与删除、眼图的测量与删除、PK-PK、Max、Min测量等。选择“Add Eye Mask”,可以通过选择信号的的type和speed自动产生Eye Mask,可以自动完成眼图的测量。

图9

仿真结果查看及测量

总结

本文主要介绍了使用ChannelExpert搭建原理图并进行时域眼图仿真分析的流程,其中特别关注了DDR模块及Bus总线连接的方式。采用Bus总线连接方式不仅提高了原理图创建的效率,还能降低信号连接的错误率。

在ChannelExpert中,内置了业内领先的时域仿真引擎Xspice,该引擎具有高度的准确性,可用于对高速并行和串行通道进行时域仿真分析,从而进一步提升通道的整体性能。通过深入的时域眼图仿真分析,用户能够更全面地了解通道的信号完整性,为优化设计和提高性能提供有力支持。

审核编辑:刘清

-

如何用泰克示波器进行眼图分析2025-12-10 1325

-

OptiSystem与OptiSPICE的联合使用:收发机电路的眼图分析2024-12-10 978

-

如何使用SIwizard的功能进行眼图分析2023-12-28 4565

-

请问ADS里如何仿真得到时域信号的功率谱密度?2023-10-20 3511

-

信号时域分析的步骤2023-09-28 3301

-

如何利用ADS仿真软件辅助进行DDR的电路仿真?2021-05-17 16513

-

利用DDR3数据眼图测试来实现快速检查信号质量2020-07-23 8872

-

DR3 数据眼图测试-快速检查信号质量2020-02-06 2268

-

【案例分享】运用眼图分析USB在布线中的信号完整性2019-07-12 4075

-

详解眼图分析USB在布线中的信号完整性问题2019-06-12 4927

-

测量眼图 眼图代表着什么? 该如何分析眼图的好与坏?2018-09-14 27232

-

DDR3内存的PCB仿真与设计2014-07-24 6500

-

DDR 1&2&3的“读”和“写”眼图分析2009-09-14 1096

全部0条评论

快来发表一下你的评论吧 !