FPGA物理约束之布局约束

描述

在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果能够保持稳定不变,使用增量式编译是一种选择,而使用布局约束是另一种更灵活的选择。此时的布局约束,通常不会针对用户逻辑部分,而是针对一些相对固定的片内存储器或乘法器,基于第一次编译的结果进行固定布局约束的设计重用,保证后续每次新的编译不再改变其布局位置,从而达到获得相对稳定的编译结果的目的。

这类基于设计重用的布局约束,简单易用,可以减少一定的编译时间,也无需设计者对底层器件结构非常了解。但也有其局限性,不适用于较大的设计变更,也不适合于固定太多的设计逻辑。因为这类设计重用,相当于为前期设计锁定了资源,使其占据了先发优势,而对于随后的设计变更,则因为无法分配到较优的资源,可能引起时序违规。因此,在实际工程应用中,此类固定布局约束需要谨慎使用。

点击OpenImplemented Design,进入Implemented页面。

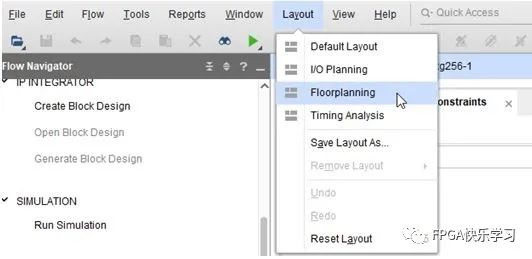

Implemented页面下,如图1所示,点击菜单Layout->Floorplanning。

图1 Floorplanning菜单

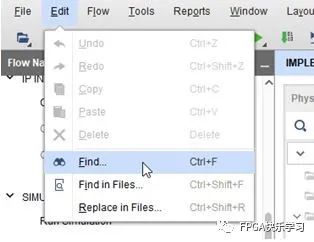

接着,如图2所示,点击菜单Edit->Find。

图2 Find菜单

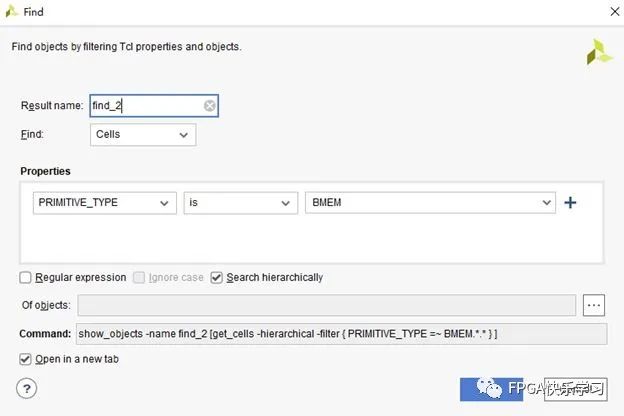

如图3所示,在弹出的Find对话框中,设置Find为Cells,Properties为PRIMITIVE_TYPEis BMEM。即查找设计中已经布局的所有Block Memory(FPGA片内块RAM)。

图3 Find对话框

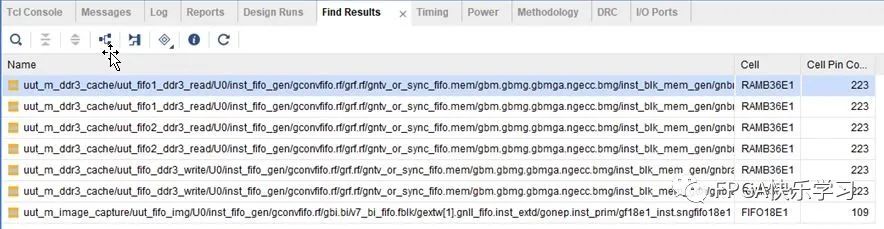

此时,如图4所示,在FindResults列表中,出现了所有搜索到的设计中使用了BMEM的Cell。

图4 FindResults列表

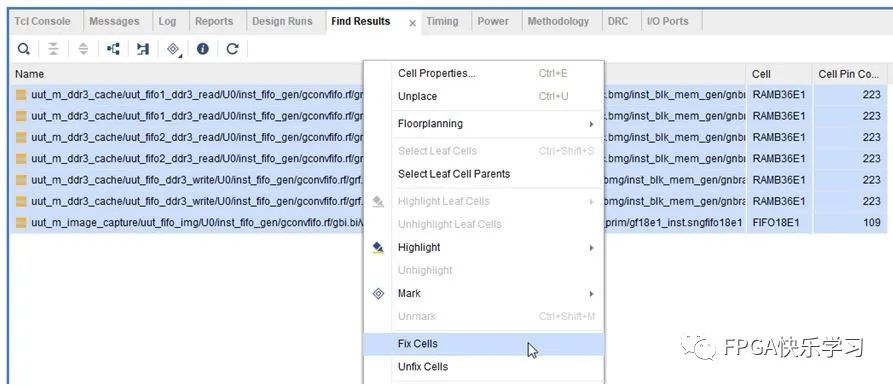

如图5所示,选中所有搜索到的RAMB36E1,右键单击,弹出菜单中点击FixCells,将所有已布局的BMEM的位置固定,使其在下一次编译时不被移动。

图5 FixCells菜单

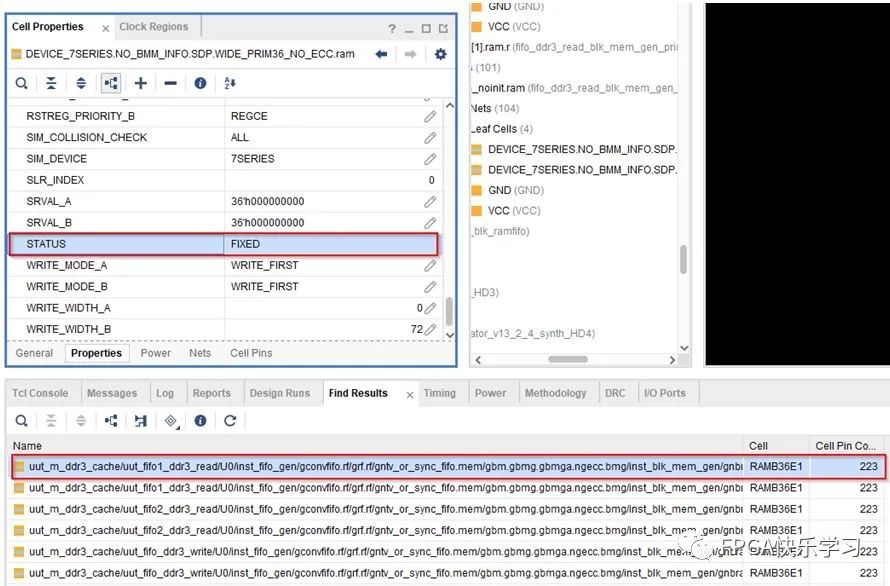

如图6所示,可以选择FindResults中的任意一个Cell,查看其Cell Properties,其STATUS项都已被修改为了FIXED。

图6 查看BMEM属性

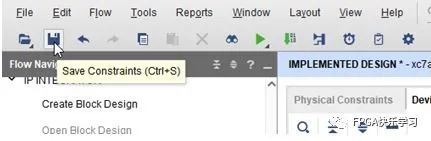

如图7所示,可以直接点击保存按钮,覆盖到当前的xdc文件中。

图7 SaveConstraints按钮

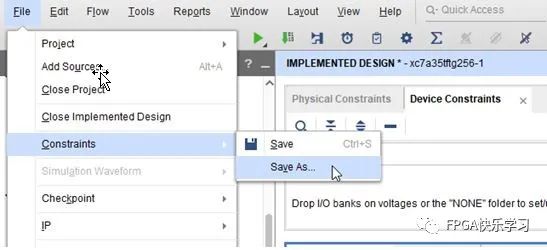

如图8所示,也可以点击菜单File->Constraints->SaveAs创建新方案存储约束脚本。

图8 SaveConstraints As菜单

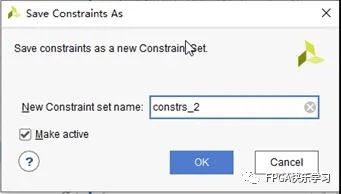

如图9所示,新的约束设置将会另存到新创建的约束方案constrs_2中。

图9 SaveConstraints As对话框

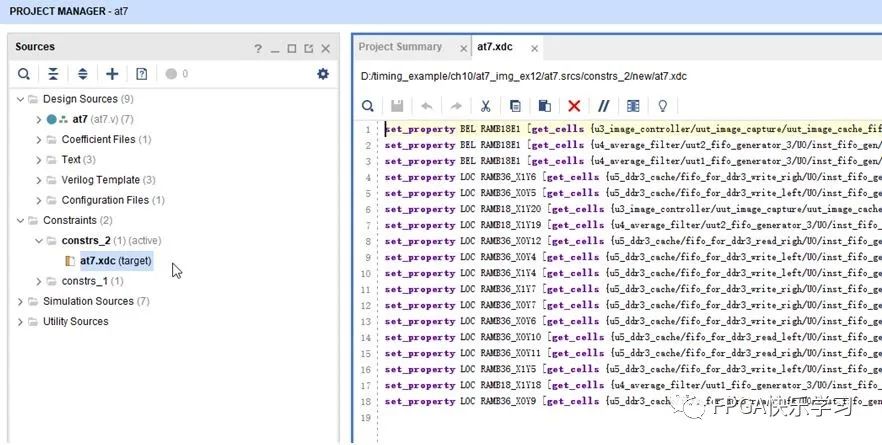

最后,如图10所示,在Source面板中可以看到,新创建的约束方案constrs_2被高亮为active状态,同时打开其下的约束文件at7.xdc,set_property BEL或set_property LOC脚本即刚添加的布局约束。重新编译后,约束将会生效。

图10 约束脚本文件

审核编辑:汤梓红

-

Xilinx FPGA的约束设置基础2024-04-26 2717

-

FPGA物理约束之布线约束2023-12-16 2511

-

FPGA的约束设计和时序分析2023-09-21 682

-

FPGA时序约束之建立时间和保持时间2023-08-14 2418

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4560

-

Xilinx FPGA管脚物理约束介绍2022-07-25 6211

-

【MiniStar FPGA开发板】配套视频教程——Gowin进行物理和时序约束2021-05-06 6320

-

简述Xilinx FPGA管脚物理约束解析2021-04-27 6546

-

XDC约束及物理约束的介绍2019-01-07 7442

-

物理约束之布局约束2018-09-26 3404

-

FPGA约束的详细介绍2018-06-25 7329

-

基于FPGA 和 SoC创建时序和布局约束以及其使用2017-11-17 3409

-

FPGA时序约束的几种方法2016-06-02 5134

全部0条评论

快来发表一下你的评论吧 !