原理图设计阶段如何考虑静电防护设计

描述

大家都知道在设计阶段解决问题的成本是最低,同样道理在原理图设计阶段做好关键信号、敏感电路的防护设计可以达到事半功倍的效果,本期将与大家探讨在原理图的设计阶段如何考虑静电防护设计。

一、防护对象识别方法

1.1 根据应用手册识别防护对象

对于芯片级的防护对象识别应根据原厂提供的应用手册,结合以往的使用经验来识别敏感信号,或者说防护对象。

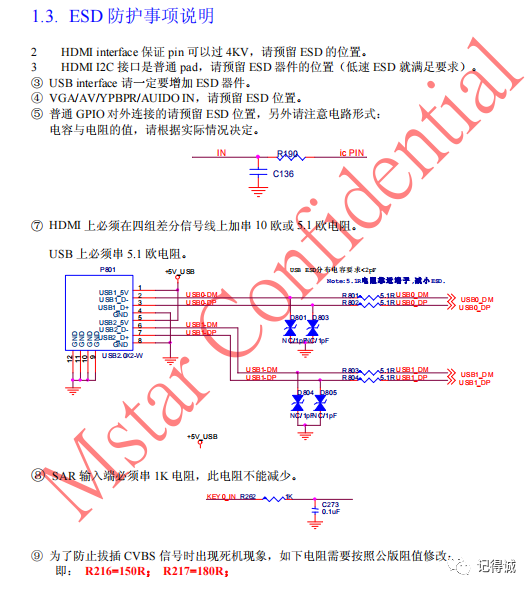

图1:原厂应用手册(AP)防护设计说明

1.2 根据端口信号类型识别防护对象

根据静电放电测试标准要求可知,外部端口根据其结构类型分别需要做不同的静电放电测试。所以针对外部互连端口在原理图设计阶段需要重点关注静电放电防护设计,具体端口类型如下:

图2:外部塑胶按键、屏蔽缝隙空气放电测试

图3:金属端子外壳测试接触放电、塑胶端子测试空气放电

1.3 根据信号类型识别防护对象

除外部互连端口信号需要重点考虑静电放电防护,系统内部互连端口也需要重点考虑静电放电防护之外,板内的小信号、关键信号、敏感信号也需要重点考虑静电放电防护。

板内需要重点关注的防护信号如:复位信号、通讯信号、串行Flash通讯信号、敏感GPIO信号、模拟信号、高速差分信号等。

二、电路级ESD防护设计

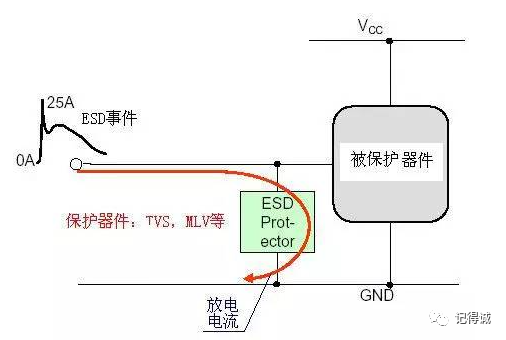

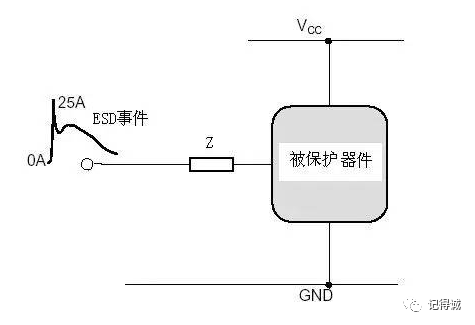

当集成电路IC经受静电放电(ESD)时,放电回路电阻通常很小,无法限制放电电流,造成高达数十安培的瞬间放电尖峰电流,流入相应的IC管脚,瞬间大电流会严重损伤IC,甚至造成IC内部烧毁。

当集成电路IC经受静电放电(ESD)时的尖峰脉冲电压时,会引起IC内部死锁;当脉冲电压超过内部CMOS器件的击穿电压时,则会击穿内部半导体器件,导致IC内部的集成电路损坏,失效。

根据集成电路损坏的机理,电路级ESD防护设计主要从静电尖峰脉冲电压钳位、静电电流限制、以及电压钳位与电流限制的双重保护设计方面进行控制。

2.1 静电尖峰脉冲电压钳位设计(ESD器件并联)

图4:并联ESD器件进行尖峰电压钳位

一是利用齐纳二极管反向击穿特性进行ESD敏感器件保护。二是利用多层金属氧化物具有非线性电压-电流(阻抗曲线)关系进行ESD敏感器件保护。三是利用气体放电管击穿气体时的损耗来进行ESD敏感器件保护。

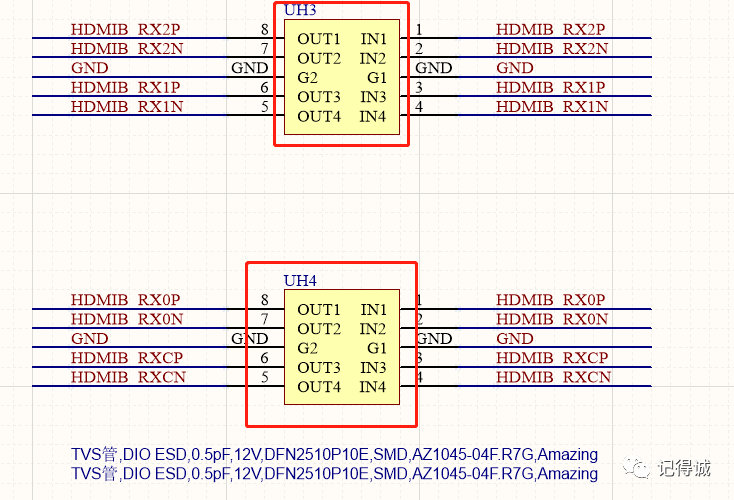

2.1.1 高速差分信号ESD防护设计

在这里插入图片描述

图5:高速差分信号并联ESD器件防护

设计要点说明:

我们知道高速差分信号需要使用低容值ESD器件,低容值ESD意味着PN结面积小,则相应的通流量差,在差分信号线上串联低阻值的电阻,可以有效减小静电电流对芯片的冲击,TVS管器件对脉冲型骚扰电压起到很好的抑制效果,二者结合可以对后端芯片进行有效的ESD防护。

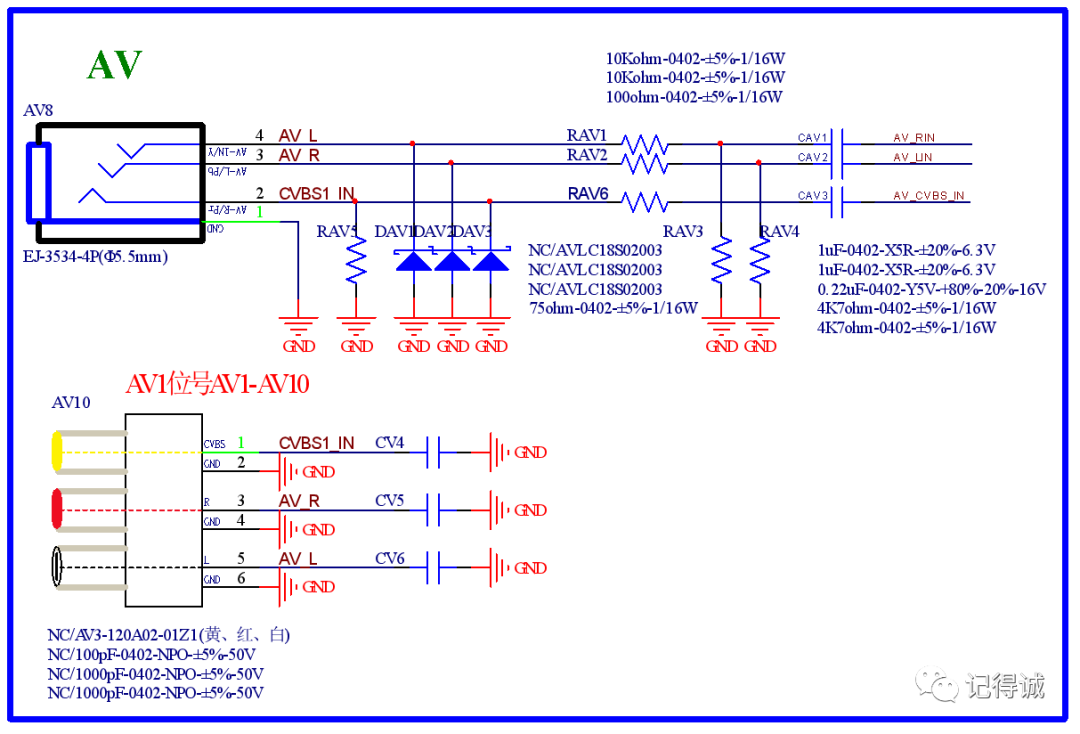

2.1.2 低速信号ESD防护设计

图6:模拟音视频信号并联ESD器件防护

设计要点说明:

低速信号ESD保护器件可选择的范围较宽,低电压的ESD器件应用较特殊,相对来说成本较高,低速信号还是建议在信号线上串联电阻,可以低成本解决ESD保护问题。

2.2 静电放电电流限制设计(串联阻抗)

一般通过串联电阻或者磁珠来限制ESD放电电流,达到静电防护的目的。如GPIO信号、ADC信号、音视频信号、串口、I2C信号等。电阻的效果通常会优于磁珠的效果,磁珠通常在100MHz频率以上阻抗较大,而电阻阻抗基本恒定。

图7:串联电阻限制静电放电电流

2.3 增加滤波电路

2.3.1 RC滤波在ESD防护设计中的应用

根据IEC61000-4-2标准给出的电流波形可知其高次谐波非常丰富,如果用滤波器滤掉主要的能量也能达到静电防护的目的。对于低频信号:如GPIO信号、ADC信号、音频输入信号可以用RC滤波电路,滤除静电放电干扰。

审核编辑:汤梓红

-

从设计阶段排查预防PCB短路2026-01-23 659

-

静电、浪涌与TVS:从测试标准到选型指南,一篇搞定电路防护2025-10-29 1067

-

在芯片设计阶段如何防护“单粒子翻转”2020-11-29 8898

-

【转】电路级静电防护设计技巧与ESD防护方法2019-04-23 2971

-

电路级静电防护设计技巧与ESD防护方法2018-10-23 2738

-

混合动力汽车在前期设计阶段整改案例2018-05-07 7483

-

电源测量的小贴士 10 个设计阶段2017-10-19 695

-

电源测量小贴士 10 个设计阶段2017-10-16 998

-

如何在设计阶段考虑降低XILINX的功耗2017-02-11 2246

-

静电防护规则2016-12-17 1107

-

LED静电防护要点2012-12-24 3455

-

静电对电子元器件的危害及防护原理2012-09-21 3489

-

自动装配设备中的静电防护问题2011-01-25 870

-

输变电工程设计阶段的造价控制2008-11-20 831

全部0条评论

快来发表一下你的评论吧 !