AMD Vitis™ Libraries Vision L3 Isppipeline U50流程示例

描述

一. 关于 AMD Vitis Vision Library

Vitis Vision 库是一组 90 多个内核,基于 OpenCV 计算机视觉库,针对 AMD FPGA、AMD AI Engine 和 AMD SoC 进行了优化。 Vitis Vision 库中的内核在 Vitis 工具套件中进行了优化和支持。

二. 硬件和软件要求

Vitis Vision 库设计用于与 AMD Zynq、AMD Zynq Ultrascale+、AMD VCK190 和 AMD Alveo FPGA 配合使用。 该库已在 zcu102、zcu104、vck190、U50 和 U200 板上经过验证。

必要条件:

有效安装 Vitis 2022.2 或更高版本以及相应的许可证。

必须安装 Xilinx Runtime (XRT)。 XRT 为 AMD FPGA 提供软件接口。

安装 OpenCV-4.4.0 x86 库(兼容 libjpeg.so)。 x86 库必须用于:

a.L1 flow irrespective of target FPGA device being PCIe or embedded.

b.L2/L3 flow when the target device is PCIe based

c.L2/L3 flow when performing software emulation for an embedded platform.

对于针对嵌入式平台的 L2/L3 Flow(针对hardware emulation and hardware build),应使用 sysroot 中附带的 aarch32/aarch64 版本 OpenCV。

如果 libOpenCL.so 不存在,则必须安装。

安装 Vitis 2022.2 或更高版本支持该平台的卡。

如果针对嵌入式平台,请安装它并设置评估板。

三. OpenCV 安装指导

建议全新安装 OpenCV 4.4.0,不要使用系统的现有库,因为它们可能适用于 Vitis 环境,也可能不适用于。

请确保更新和升级系统的软件包和操作系统库,并安装 cmake 版本>3.5,然后再继续。不然可能遇到如下的错误:

#CMake Error: The source directory "/home/***/Desktop/source/source/build/WITH_V4L=ON" does not exist.

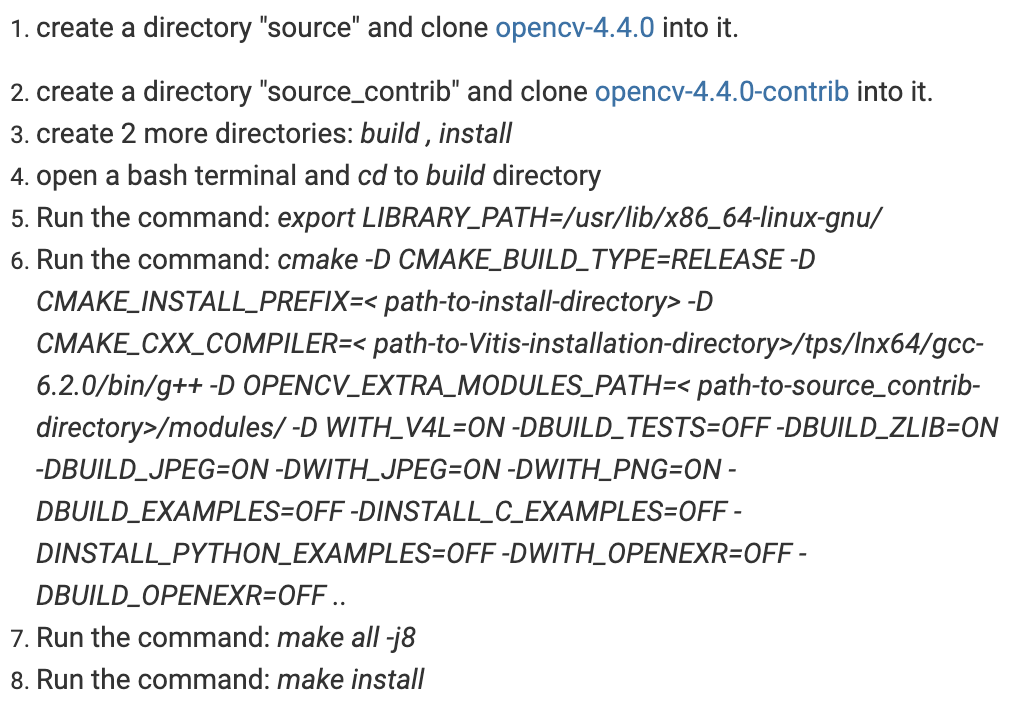

以下步骤可帮助安装编译和链接 Vitis Vision 主机代码中的 OpenCV 调用所需的基本库。

下面是一个完整的示例,基于 Ubuntu 22.04/bash,在 /home/ycw/Desktop 路径下操作。

以下为可能会遇到的问题:

Q1: 遇到下面的这个错误,可能 cmake 的版本没有大于3.5。

CMake Error: The source directory "/home/ycw/Desktop/source/source/build/WITH_V4L=ON" does not exist.

Q2:FATAL: In-source builds are not allowed.

需要安装上面的步骤 mkdir build文件夹,注意如果已经创建了 build 目录,还是出现这个 FATAL ERROR 注意 cd 回 source 目录内,尝试使用如下命令清理一下 cache:rm -rf CMakeCache.txt CMakeFiles

Q3:CMAKE_CXX_COMPILER=< path-to-Vitis-installation-directory>.

这里的 path-to-Vitis-installation-directory应该设置成 Vitis_HLS 的路径。

见上面的完整示例。

五. 两种 platform 的 master/vision/L3/examples/isppipeline 的流程

Level 3: Pipeline Applications:

https://github.com/Xilinx/Vitis_Libraries/tree/master/vision/L3#level-3-pipeline-applications

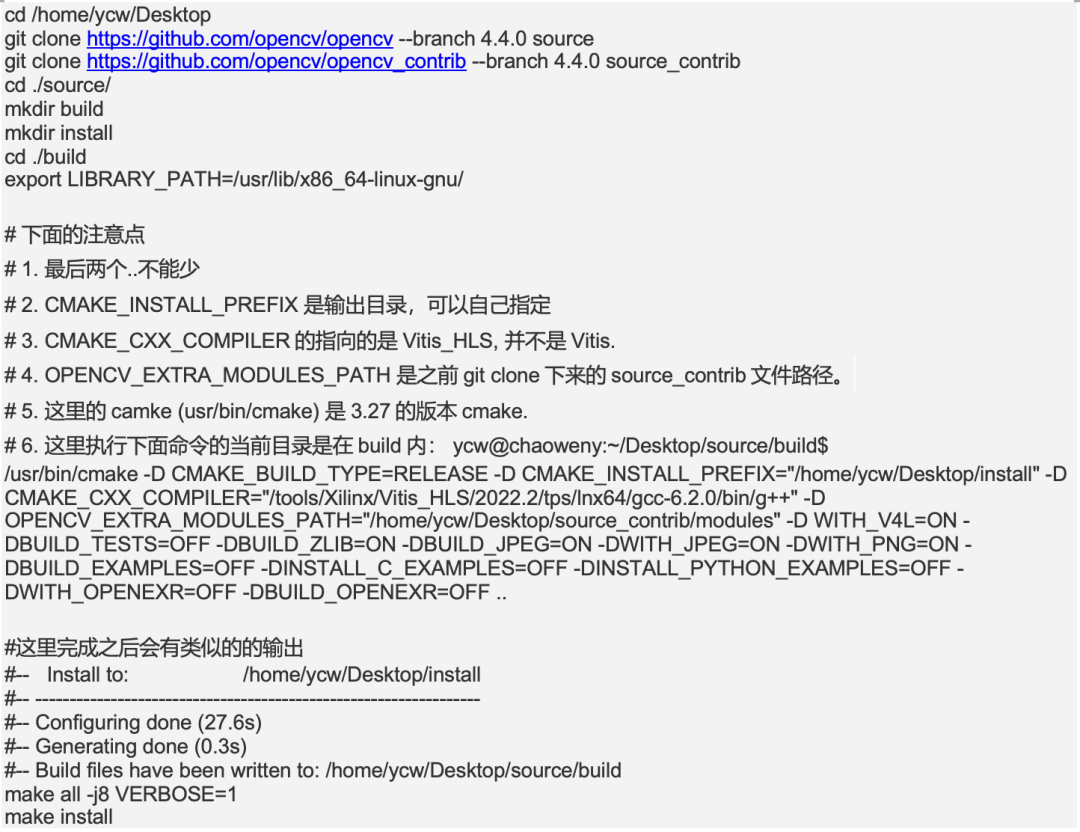

不同设备和行为流程如下:

实例:

1. Pcie设备示例(U50):

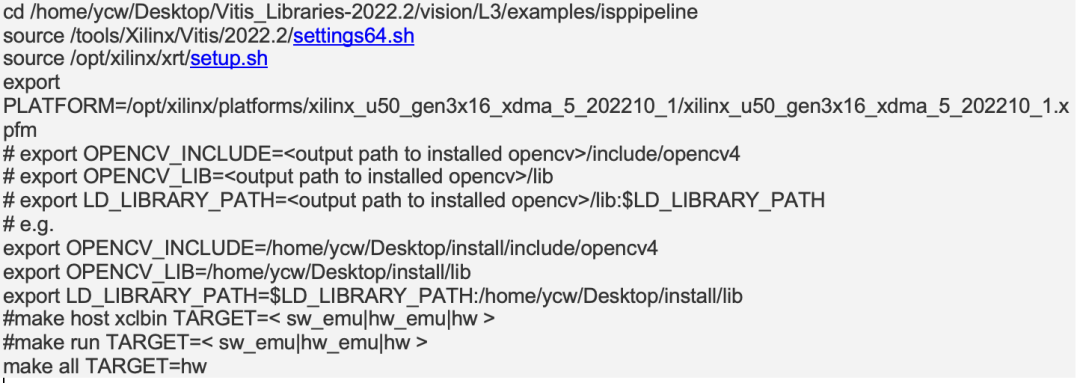

xilinx_u50_gen3x16_xdma_5_202210_1.xpfm的编译 make 流程:

a. OPENCV_INCLUDE、OPENCV_LIB 指向的是步骤3(OpenCV 安装指导)CMAKE_INSTALL_PREFIX 设置的目录内。

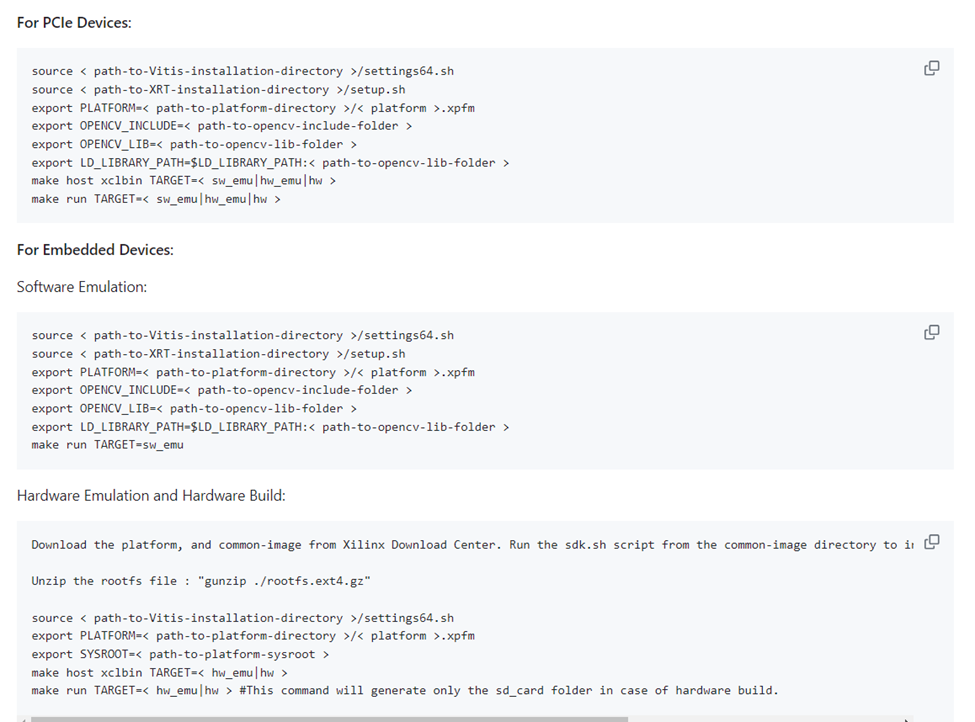

b. U50 的 platform

(xilinx_u50_gen3x16_xdma_5_202210_1.xpfm)

该示例 xilinx_u50_gen3x16_xdma_5_202210_1.xpfm 默认部署在下图的路径。

c. 示例代码:

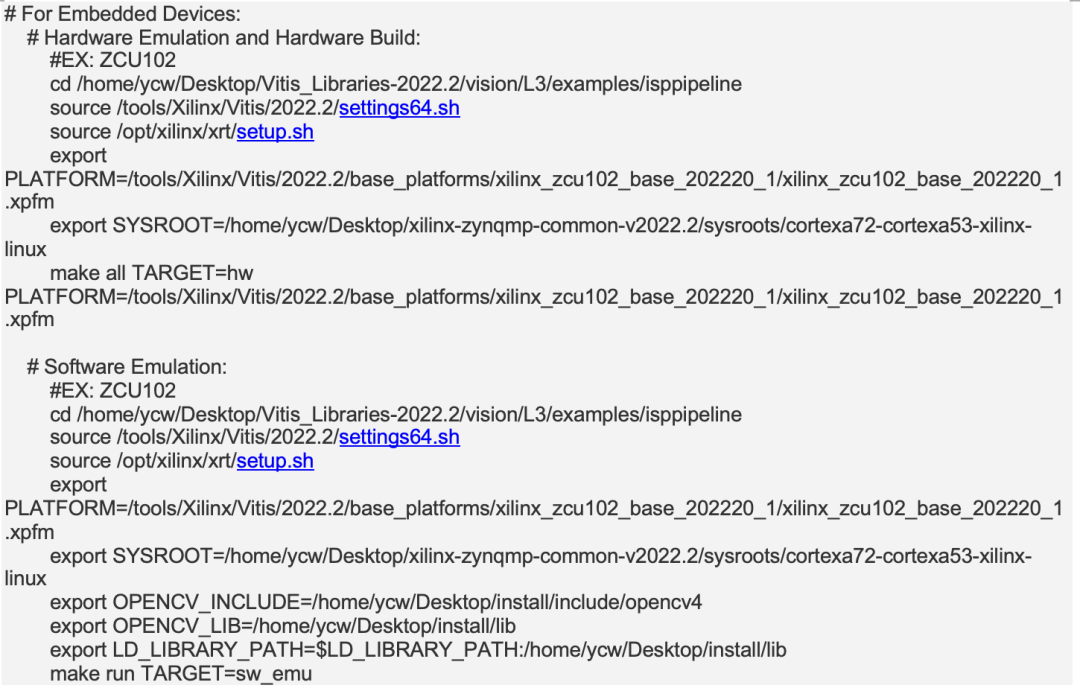

2. Embedded 设备示例(ZCU102):

xilinx_zcu102_base_202220_1.xpfm 的编译 make 流程:

注意点:

a. OPENCV_INCLUDE、OPENCV_LIB指向的是步骤3(OpenCV 安装指导)CMAKE_INSTALL_PREFIX 设置的目录内。

b. SYSROOT 可以通过如下的方式获取:

2.1 在下面的链接下载 zynqmp 的 common image :

https://www.xilinx.com/member/forms/download/xef.html?filename=xilinx-zynqmp-common-v2022.2_10141622.tar.gz

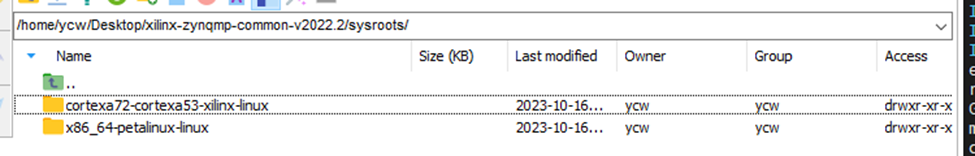

2.2 解压之后,cd 到 common-image 目录内,使用命令(./sdk.sh -y -d ./ -p)安装 sysroot。该示例安装完成之后,安装在下图显示的目录:/home/ycw/Desktop/xilinx-zynqmp-common-v2022.2/sysroots/

c. 示例代码:

六. 板上运行

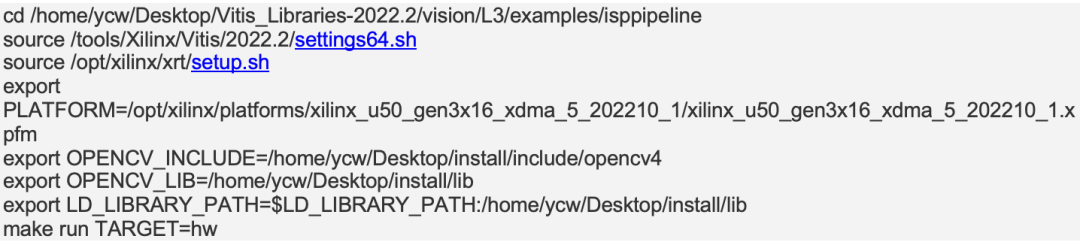

U50 的 HW 运行示例:

1. 使用 make run TARGET=hw 运行的示例代码:

注:运行之后可以看到在

/home/ycw/Desktop/Vitis_Libraries-2022.2/vision/L3/examples/isppipeline/ 目录下生成了 hls_output.png 文件。

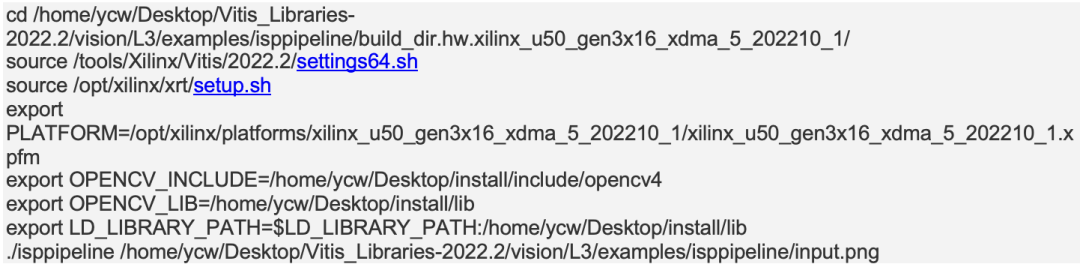

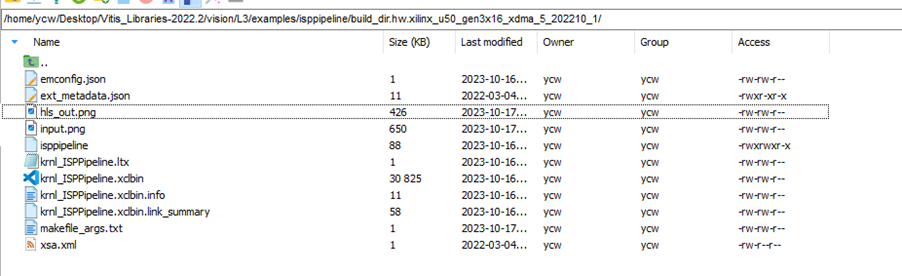

2. Build HW 之后生成的 App 运行示例:

注:

1. 当前在

/home/ycw/Desktop/Vitis_Libraries-2022.2/vision/L3/examples/isppipeline/build_dir.hw.xilinx_u50_gen3x16_xdma_5_202210_1/

路径内,isppipeline 需要带入输入图片的绝对路径参数,这里输入图片的路径是:

/home/ycw/Desktop/Vitis_Libraries-2022.2/vision/L3/examples/isppipeline/input.png

2. 生成的图片默认也在

/home/ycw/Desktop/Vitis_Libraries-2022.2/vision/L3/examples/isppipeline/build_dir.hw.xilinx_u50_gen3x16_xdma_5_202210_1/

路径内。

审核编辑:刘清

-

使用AMD Vitis Unified IDE创建HLS组件2025-06-20 2599

-

U50的AMD Vivado Design Tool flow设置2024-11-13 1765

-

AMD Vitis™设计工具中的Libraries新功能介绍2024-05-29 1707

-

在Windows 10上创建并运行AMD Vitis™视觉库示例2024-05-08 2085

-

Alveo U50数据中心加速卡数据表2023-09-15 571

-

【KV260视觉入门套件试用体验】部署DPU镜像并运行Vitis AI图像分类示例程序2023-09-10 3773

-

Vitis 库流程:视觉 L1 重映射函数 Zynq baremetal 设计实例2023-07-13 1272

-

如何在IWR1642/AWR1642上修改L3 RAM的分布?2022-11-10 737

-

基于Vitis HLS的加速图像处理2022-02-16 3490

-

如何修改代码来改变L3 RAM分布的具体流程和步骤2022-01-13 2634

-

今天发布!详解赛灵思加速卡Alveo U50的轻与重2019-08-07 17551

-

有具有CMT,MBM,L3 CAT,L3 CDP和MBA的处理器吗2018-11-06 2925

-

传AMD将放弃Vision品牌 改用platform区分产品2012-12-29 2407

全部0条评论

快来发表一下你的评论吧 !