pcb关键信号怎么样去布线

PCB设计

描述

在pcb布线规则中,有一条“关键信号线优先”的原则,即电源、摸拟信号、高速信号、时钟信号、差分信号和同步信号等关键信号优先布线。接下来,我们不妨就来详细了解下这些关键信号的布线要求。

模拟信号布线要求

模拟信号的主要特点是抗干扰性差,布线时主要考虑对模拟信号的保护。

对模拟信号的处理主要体现在以下几点:

1. 为增加其抗干扰能力,走线要尽量短。

2. 部分模拟信号可以放弃阻抗控制要求,走线可以适当加粗。

3. 限定布线区域,尽量在模拟区域内完成布线,远离数字信号。

高速信号布线要求

1. 多层布线

高速信号布线电路往往集成度较高,布线密度大,采用多层板既是布线所必须的,也是降低干扰的有效手段。合理选择层数能大幅度降低印板尺寸,能充分利用中间层来设置屏蔽,能更好地实现就近接地,能有效地降低寄生电感,能有效缩短信号的传输长度,能大幅度地降低信号间的交叉干扰等。

2. 引线弯折越少越好

高速电路器件管脚间的引线弯折越少越好。高速信号布线电路布线的引线采用全直线,需要转折,可用45°折线或圆弧转折,这种要求在低频电路中仅仅用于提高钢箔的固着强度,而在高速电路中,满足这一要求却可以减少高速信号对外的发射和相互间的耦合,减少信号的辐射和反射。

3. 引线越短越好

高速信号布线电路器件管脚间的引线越短越好。引线越长,带来的分布电感和分布电容值越大,对系统的高频信号的通过产生很多的影响,同时也会改变电路的特性阻抗,导致系统发生反射、振荡等。

4. 引线层间交替越少越好

高速电路器件管脚间的引线层间交替越少越好。所谓“引线的层间交替越少越好”,是指元件连接过程中所用的过孔越少越好。据测,一个过孔可带来约0.5pf的分布电容,导致电路的延时明显增加,减少过孔数能显着提高速度。

5. 注意平行交叉干扰

高速信号布线要注意信号线近距离平行走线所引入的“交叉干扰”,若无法避免平行分布,可在平行信号线的反面布置大面积“地”来大幅度减少干扰。

6. 避免分枝和树桩

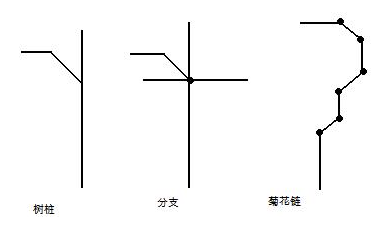

高速信号布线应尽量避免分枝或者形成树桩(Stub)。树桩对阻抗有很大影响,可以导致信号的反射和过冲,所以我们通常在设计时应避免树桩和分枝。采用菊花链的方式布线,将对信号的影响降低。

7. 信号线尽量走在内层

高频信号线走在表层容易产生较大的电磁辐射,也容易受到外界电磁辐射或者因素的干扰。将高频信号线布线在电源和地线之间,通过电源和底层对电磁波的吸收,所产生的辐射将减少很多。

时钟信号布线要求

在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。时钟电路在数字电路中点有重要地位,同时又是产生电磁辐射的主要来源。时钟的处理方法也是在PCB布线时需要特别重视的。在一开始就理清时钟树,明确各种时钟之间的关系,布线的时候就能处理得更好。并且时钟信号也经常是EMC设计的难点,需要过EMC测试指标的项目尤其要注意。

时钟线除了常规的阻抗控制和等长要求外,还需要注意以下问题:

1. 时钟信号尽量选择优选布线层。

2. 时钟信号尽量不跨分割,更不要沿着分割区布线。

3. 注意时钟信号与其他信号的间距,至少满足3W。

4. 有EMC要求的设计,较长的时候线尽量选择内层布线。

5. 注意时钟信号的端接匹配。

6. 不要采用菊花链结构传送时钟信号,而应采用星型结构,即所有的时钟负载直接与时钟功率驱动器相互连接。

7. 所有连接晶振输入/输出端的导线尽量短,以减少噪声干扰及分布电容对晶振的影响。

8. 晶振电容地线应使用尽量宽而短的导线连接至器件上;离晶振近的数字地引脚,应尽量减少过孔。

9. 在数字电路中,通常的时钟信号都是边沿变化快的信号,对外串扰大。所以在设计中,时钟线宜用地线包围起来并多打地线也来减少分布电容,从而减少串扰;对高频信号时钟尽量使用低电压关分时钟信号并包地方式,需要注意包地打孔的完整性。

差分信号布线要求

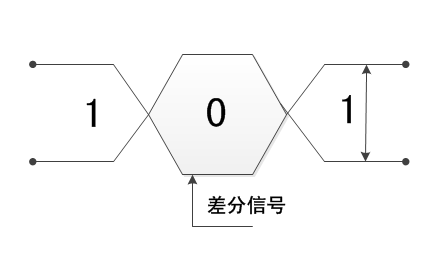

差分信号,有些也称差动信号,用两根完全一样,极性相反的信号传输一路数据,依靠两根信号电平差进行判决。为了保证两根信号完全一致,在布线时要保持并行,线宽、线间距保持不变。

pcb关键信号如何去布线

在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

1. 等长:等长是指两条线的长度要尽量一样长,是为了保证两个差分信号时刻保持相反极性。减少共模分量。

2. 等宽等距:等宽是指两条信号的走线宽度需要保持一致,等距是指两条线之间的间距要保持不变,保持平行。

提醒:尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其的回路面积。采用屏蔽和加大安全间距等方法,保证信号质量。

-

电路板厂PCB关键信号如何去布线?2023-11-22 1788

-

PCB布线对模拟信号传输的影响如何分析2023-10-31 1947

-

PCB布线减少高频信号串扰的措施都有哪些?2023-10-19 2851

-

PCB布线技巧升级:高速信号篇2023-08-01 4352

-

电路板厂PCB关键信号如何去布线?2023-04-12 1890

-

浅谈PCB关键信号的布线要求2023-01-13 2682

-

PCB线路板关键信号如何去布线2022-11-07 3563

-

PCB设计中关键信号的布线要求2022-10-11 2275

-

混合信号PCB的布线技巧2020-09-18 2668

-

pcb关键信号如何去布线2020-01-01 4351

-

怎么样去使用PCB自动布线的功能2019-09-25 2880

-

高速PCB设计系列基础知识58|高速信号关键信号的布线要求2017-10-19 3140

-

PCB布线技巧之去耦电容的摆放2016-10-26 1448

-

pcb布线面临的关键时刻2013-10-25 3937

全部0条评论

快来发表一下你的评论吧 !