DDR5 dimm里为什么要设计两个channel?

存储技术

描述

为什么DDR5要设计sub channel的概念,sub channel的设计初衷是什么?一个sub channel的带宽是32bit,要组成一个64bit的cache line岂不是还是需要两个channel同时工作?

首先引入2个概念:

1、Burst Length: 突发(Burst) 是指在同一行中相邻的存储单元连续进行数据传输的方式。连续传输的周期数就是突发长度 (Burst Lengths,简称BL)。

对于DDR3和DDR4内存,其BL=8: 对于DDR5内存,其BL=16.

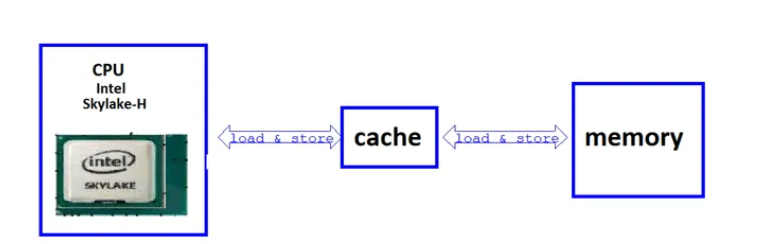

2、Cache line: 我们知道CPU是不能直接读取内存当中的数据,CPU要想读取内存当中的数据,首先要将数据从内存里加载到高速缓存cache中,然后再读取cache中的数据

我们将一个cache平均分成相等的很多块,每一个块大小我们称之为cache line。

例如: 一个32 Bytes大小的cache,如果我们将其平均分成32块,那么每一块cache line就是1Byte,总共有32行cache line。如果我们将其平均分成8块,那么cache line大小就是4 Bytes,总共8行cache line。

cache line是cache和内存之间数据传输的最小单位。什么是最小单位?

例: cache从Memory获取数据的最小单位是64Bytes,当cache要从内存里读取一个32 Bytes的数据时,不会只把这32 Bytes的数据读进来,而是会把64 Bytes的数据一起读进来

而对于X86架构的CPU来讲,它的Cache line大小正好就是64Bytes。

在我们DDR4时,数据位宽是64位的,就是我们一次读写64bit的数据,每次读写最高的BurstLength是8位,乘起来就是64bit*8=512bit=64Byte,也就是我们X86架构的CPU cache line 的大小。

那么到了DDR5的时候,每次读写最高的Burst Length变为了16位,如果我们的通道还是维持64bit的位宽,那么我们乘起来就是64bit*16=1024bit,1024bit超过了我们的cpu cache line%的传统大小。如果我们依然要这么做的话,那么我们的内存控制器的架构,从底层硬件到上层读写数据的软件配套都要去改,这样改动就非常大。所以在DDR5时,就引入了sub-channel的概念

每个sub-channel有效数据位是32位,32bit*16 (Burst Length) =512bit,这样就能够满足我们cpu cache line 的需求。所以就是DDR5引入sub-channel的原因。

Reference:为什么DDR5要在一个dimm里面设计两个channel?- 知乎 (zhihu.com)

审核编辑:黄飞

-

Amphenol ICC DDR5 SO - DIMM连接器:高速高密度的理想之选2025-12-12 637

-

TE Connectivity DDR5 DIMM插槽技术解析与应用指南2025-11-07 1028

-

DDR5 设计指南(一):DDR5 VS LPDDR52025-10-27 11579

-

DDR5内存的工作原理详解 DDR5和DDR4的主要区别2024-11-22 9434

-

Introspect DDR5/LPDDR5总线协议分析仪2024-08-06 4855

-

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?2024-03-17 5670

-

DDR4和DDR5规格之间的差异2023-05-08 4383

-

千呼万唤始出来的DDR5 DIMM插槽连接器,买它!2023-05-06 2362

-

呼万唤始出来的DDR5 DIMM插槽连接器,买它!2023-02-19 1293

-

千呼万唤始出来的DDR5 DIMM插槽连接器2023-02-16 2193

-

什么是驱动DDR5 有什么新功能2022-04-26 5000

-

Longsys DDR5内存条预计在2022年进入量产阶段2021-11-02 4164

-

嘉合劲威将在2021年率先实现DDR5内存量产2020-12-02 2759

-

新技术内存接口DDR5有望2019年量产2017-09-26 3736

全部0条评论

快来发表一下你的评论吧 !