阻抗知识介绍

描述

一、什么是阻抗:

具有电阻、电容、电感的电路里,对交流电所起的阻碍作用叫阻抗,阻抗常用字母Z表示,单位是欧姆。阻抗是一个复数,实部为电阻,虚部为电抗,其中电容在电路中对交流电所起的阻碍作用称为容抗,电感在电路中对交流电所起的阻碍作用称为感抗,电容和电感在电路中对交流电引起的阻碍作用总称为电抗。

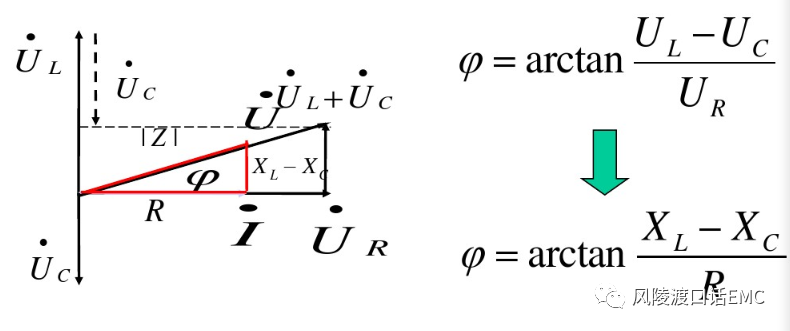

1.1、阻抗计算公式:

Z= R+j(XL–XC)其中R为电阻,XL为感抗,XC为容抗。如果( XL–XC) > 0的情况下,称为“感性负载”,如果( XL –XC) < 0的情况下,称为“容性负载”。

1.2、阻抗相位:

如果阻抗的相位角为负值,此电路是容性的,如果阻抗相位角为正值,那么此电路是感性的。如果相位角是+90℃,那么电路是纯感性的,如果相位角是-90℃,那么电路是纯容性的,如果相位角是0℃,那么电路是纯电阻值的。

二、瞬时阻抗与特性阻抗:

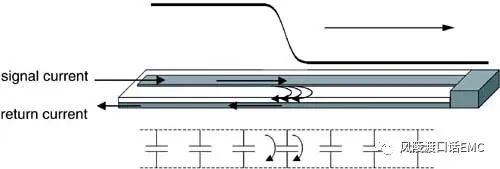

2.1、特性阻抗(Characteristic Impedance):

信号在传输过程中,信号线与参考平面间由于电场的建立,则会产生一个瞬间电流,如果信号的输出电平为V,在信号传输过程中,传输线就会等效成一个阻抗,即V/I,把这个等效阻抗称为传输线的特性阻抗。

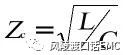

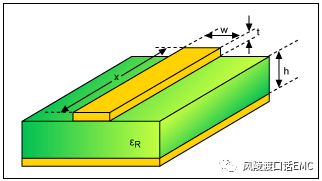

特性阻抗的计算:

2.2、瞬时阻抗:

信号在传输过程中,每个瞬间感受到的阻抗,我们称做瞬时阻抗。信号传输过程中的瞬时阻抗是影响高速差分信号EMC辐射的重要因素之一。

瞬时阻抗与特性阻抗之间的联系:

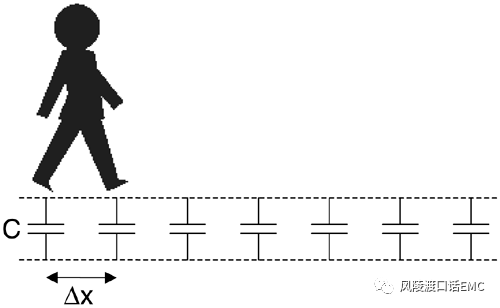

对于均匀传输线,信号传输过程中每点感受到的瞬时阻抗均相等,瞬时阻抗相等时的阻抗我们称着特性阻抗。特性阻抗在数值上与均匀传输线的瞬态阻抗相等,它是传输线的固有特性,且仅与材料特性、介电常数、和单位长度电容量有关,而与传输线长度无关。

2.3、影响PCB特性阻抗的因素:

影响PCB特性阻抗的因素:

PCB布线的线宽

PCB布线敷铜厚度

PCB介质的介电常数

PCB介质的厚度

参考平面的距离

元件焊盘的宽度与厚度

三、阻抗匹配(Impedance matching) :

3.1、什么是阻抗匹配:

阻抗匹配主要用于传输线上,以此达到所有高频的微波信号均能传递至负载点的目的,而且几乎不会有信号反射回来源点,从而提升能源效益。信号源内阻与所接传输线的特性阻抗大小相等且相位相同,或传输线的特性阻抗与所接负载阻抗的大小相等且相位相同,分别称为传输线的输入端或输出端处于阻抗匹配状态,简称为〝阻抗匹配〞。

阻抗匹配的条件:

负载阻抗等于信号源内阻抗,即它们的电阻与阻抗相等,电阻可视为相位为零时的阻抗,也就是 jx=XL-XC =0,这时在负载阻抗上可以得到无失真的电压传输。

负载阻抗等于信号源内阻抗的共轭值,即它们的模相等而辐角之和等于零,这时在负载阻抗上可以得到最大功率,这种匹配叫共轭匹配。

在纯电阻电路中,负载电阻等于激励源内阻时,则输出功率最大,这种状态称作匹配;当激励源内阻抗与负载阻抗含有电抗成份时,为使时负载得到最大功率,负载阻抗与激励源内阻抗则必须满足共轭关系,即电阻成份相等,电抗成份绝对值相等而符号相反,称为共轭匹配。

3.2、反射与反射系数:

反射的定义:

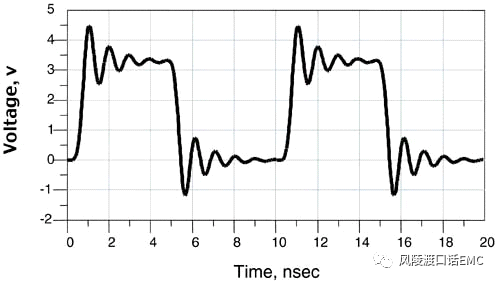

信号沿传输线传播时,感受到的瞬态阻抗发生了改变,部分信号将沿着与原传播方向相反的方向反射,另一部分将继续传播,但幅度有所改变。反射会使信号产生过冲、振铃、形成驻波。

上冲又叫过冲,它指的是沿着信号边沿的跳变方向,信号波形中超出稳定的“1”或“0”状态电平的部分。

下冲又叫反冲,它指的是信号在过冲后,又沿着跳变方向的反方向,信号波形越过稳定的“1”或“0”状态电平的部分。

振铃是指信号发生连续多次的上冲和下冲所形成的震荡,一般其振幅应是一次比一次小逐渐趋于零。

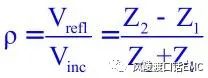

反射系数:

为量化信号反射,引入反射系数指标。反射系数计算公式是

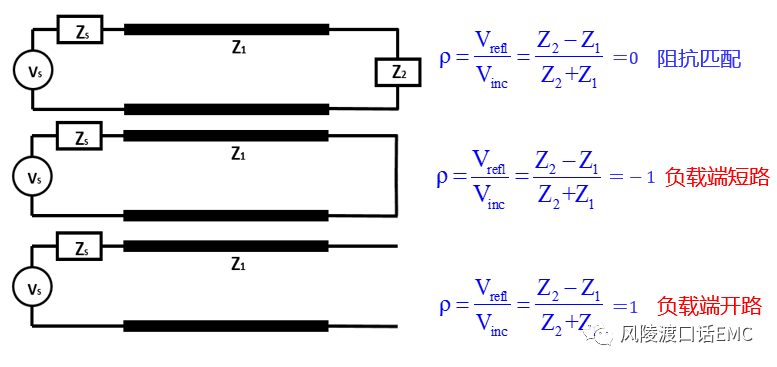

反射的三种极端情况:

3.3、阻抗匹配的形式:

阻抗匹配有两种,一种是通过改变阻抗力(Lumped-Circuit Matching),另一种则是调整传输线的波长(Transmission Line Matching)。要匹配一组线路,首先把负载点的阻抗值,除以传输线的特性阻抗值来归一化,然后把数值划在史密斯图上。

改变阻抗力:

把电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿着代表实数电阻的圆圈走动。如果把电容或电感接地,首先图表上的点会以图中心旋转 180 度,然后才沿电阻圈走动,再沿中心旋转 180 度。重复以上方法直至电阻值变成 1,即可直接把阻抗力变为零完成匹配。阻抗匹配:简单的说就是「特性阻抗」等于「负载阻抗」

调整传输线波长:

由负载点至来源点加长传输线,在图表上的圆点会沿着图中心以逆时针方向走动,直至走到电阻值为 1 的圆圈上,即可加电容或电感把阻抗力调整为零完成匹配。

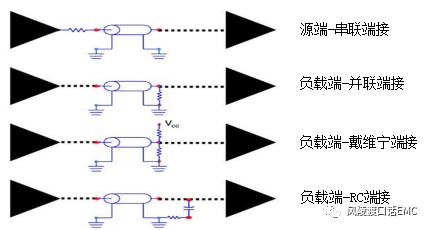

3.4、阻抗匹配的端接方法:

源端串联匹配:

源端串联匹配的理论出发点是在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻 R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

源端串联匹配的特点:

反射信号与源端传播的信号叠加,使负载端接受到的信号与原始信号的幅度近似相同。

负载端反射信号向源端传播,到达源端后被匹配电阻吸收。

反射信号到达源端后,源端驱动电流降为0,直到下一次信号传输。

源端串联匹配不适合链状拓扑结构的信号网络。

选择串联终端匹配电阻值的原则很简单, 就是要求匹配电阻值与驱动器的输出阻抗之和与传输线的特征阻抗相等。

负载端并联匹配:

负载端并联匹配的理论出发点是在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。实现形式分为单电阻和双电阻两种形式 。

负载端并联匹配的特点:

驱动信号近似以满幅度沿传输线传播。

所有的反射都被匹配电阻吸收。

负载端接受到的信号幅度与源端发送的信号幅度近似相同。

并联终端匹配优点是简单易行,显而易见的缺点是会带来直流功耗。单电阻

方式的直流功耗与信号的占空比紧密相关,双电阻方式无论信号是高电平

是低电平都有直流耗。

负载端并联匹配总结:

单电阻形式的负载端并联匹配要求负载端的并联电阻值必须与传输线的特征阻抗相近或相等;而双电阻形式的负载端并联匹配也叫戴维南终端匹配,要求的电流驱动能力比单电阻形式小。这是因为两电阻的并联值与传输线的特征阻抗相匹配,每个电阻都比传输线的特征阻抗大。考虑到芯片的驱动能力,两个电阻值的选择必须遵循三个原则:两电阻的并联值与传输线的特征阻抗相等;与电源连接的电阻值不能太小,以免信号为低电平时驱动电流过大;与地连接的电阻值不能太小,以免信号为高电平时驱动电流过大。

负载端RC并联匹配:

不论单电阻形式还是双电阻形式的负载端并联匹配都会带来直流损耗的问题,为解决此问题负载端RC并联匹配应时而生,由于电容具有〝隔直通交〞的特性,交流信号通过时电容相当于短路,负载端阻抗与传输线阻抗相等,可以有效抑制信号反射,而直流信号流过时,电容相当于开路,匹配电阻相当于不存在,对直流几乎无损耗。

本条内容来自微信公众号“风陵渡口话EMC”,由“星空yzg”选编。如有任何反馈,请留言给我们。

-

器件知识介绍及图片2009-09-16 4154

-

阻抗匹配知识2012-08-03 6266

-

Polar Si8000阻抗计算基本知识2019-06-11 2454

-

电阻的基础知识介绍2021-02-26 2990

-

输入阻抗和输出阻抗的基本知识2009-04-22 4840

-

阻抗匹配的详细介绍2009-10-20 2142

-

阻抗匹配及相关知识汇集2010-01-23 1280

-

阻抗匹配知识概述2010-10-26 2669

-

微动开关使用知识介绍(含保护)2016-02-23 1465

-

天线阻抗是什么?天线阻抗的介绍和阻抗调谐及孔径调谐的详细资料概述2018-08-30 3389

-

射频电路的基础知识介绍2019-09-27 24189

-

阻抗LCR测量基础2021-06-16 1271

-

风扇基础知识:气流、静压和阻抗2023-03-13 12465

-

电感器和电容器的高频特性基础知识——阻抗和谐振(1)2023-10-09 2564

-

Polar Si8000阻抗计算基本知识.zip2022-12-30 762

全部0条评论

快来发表一下你的评论吧 !