SiC外延层的缺陷控制研究

描述

文章来源:宽禁带半导体技术联盟 原文作者:IAWBS

探索SiC外延层的掺杂浓度控制与缺陷控制,揭示其在高性能半导体器件中的关键作用。

目前常见的SiC外延技术有化学气相沉积(CVD)、液相外延生长(LPE)、分子束外延生长(MBE)等,当前,CVD是主流技术,具备较高生长速率、能够实现可控掺杂调控等优点。CVD外延生长通常使用硅烷和碳氢化合物作为反应气体,氢气作为载气,氯化氢作为辅助气体,或使用三氯氢硅(TCS)作为硅源代替硅烷和氯化氢,在约1600℃的温度条件下,反应气体分解并在SiC衬底表面外延生长SiC薄膜。

1. SiC外延层的掺杂浓度控制

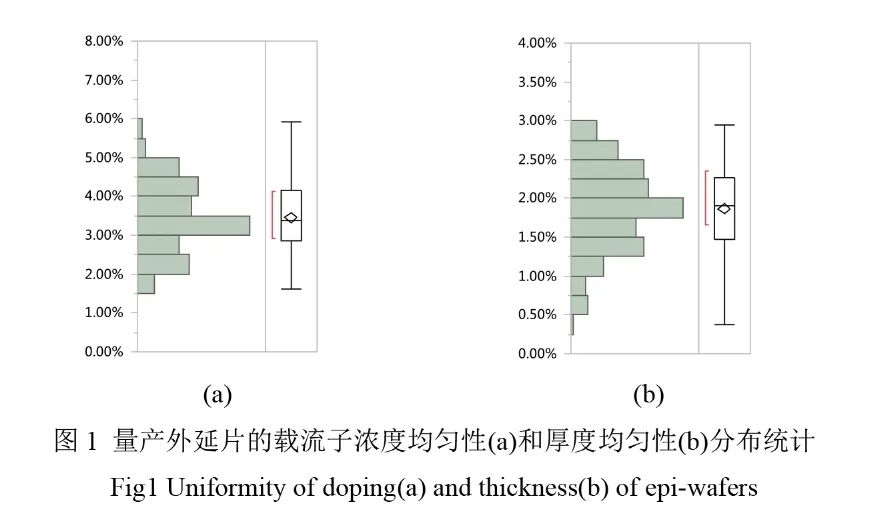

本团队采用水平式外延生长方法,三氯氢硅和乙烯作为反应气源,氮气作为掺杂气体,氢气作为载气,氢气和气作为驱动托盘旋转的气源,生长厚度适用于1200V的SiC基MOSFET用SiC外延层。通过调整掺杂氮气在中心和边缘分布比例、托盘旋转的速度以及旋转气体中氯气与氢气的比例,优化外延工艺的C/Si比等生长参数,实现SiC外延层掺杂浓度以及均匀性的有效控制,图1是量产1000片的厚度和浓度均匀性统计数据,C/Si比在1.0~1.2、温度在1600~1650C和压力在100mbar的工艺条件下,统计的外延产品100%达到厚度均匀性小于3%、浓度均匀性小于6%。

2. SiC 外延层的缺陷控制研究

根据晶体缺陷理论,SiC外延材料的主要缺陷可归纳为4大类:点缺陷、位错(属于线缺陷)、层错(属于面缺陷)和表面缺陷(属于体缺陷)。

2.1 点缺陷

SiC外延材料的点缺陷主要有硅空位、碳空位、硅碳双空位等缺陷,它们在禁带中产生深能级中心,影响材料的载流子寿命。在轻掺杂的SiC 外延层中,点缺陷产生的深能级中心浓度通常在5E12~2E13 cm-3,与外延生长条件特别是C/Si 比和生长温度相关。

2.2 位错缺陷

SiC 材料的位错包括螺位错(TSD)、刃位错(TED)和基平面位错(BPD)。微管是伯氏矢量较大的螺位错形成的中空管道,可认为是一种超螺位错。SiC 外延层的位错缺陷基本都和衬底相关,大部分微管和螺位错会复制到外延层中,在合适的工艺条件下,部分微管分解为单独的螺位错,形成微管闭合,只有一小部分TSD(通常<2%)转为Frank 型层错;衬底TED基本都会复制到外延层中。

BPD位错主要源于衬底中BPD向外延层的贯穿,通常偏4º 4H-SiC衬底中大部分BPD位错(>99%)在外延过程中会转化为TED位错,只有少于1%左右的BPD会贯穿到外延层中并达到外延层表面。在后续器件制造中,BPD主要影响双极型器件的稳定性,如出现双极型退化现象。在正向导通电流的作用下,BPD可能会延伸至外延层演变成堆垒层错(SF),造成器件正向导通电压漂移。由于刃位错对器件性能的影响要小得多,所以提高SiC外延生长过程中BPD转化为TED的比例,阻止衬底中的BPD向外延层中延伸对提高器件的性能十分重要。

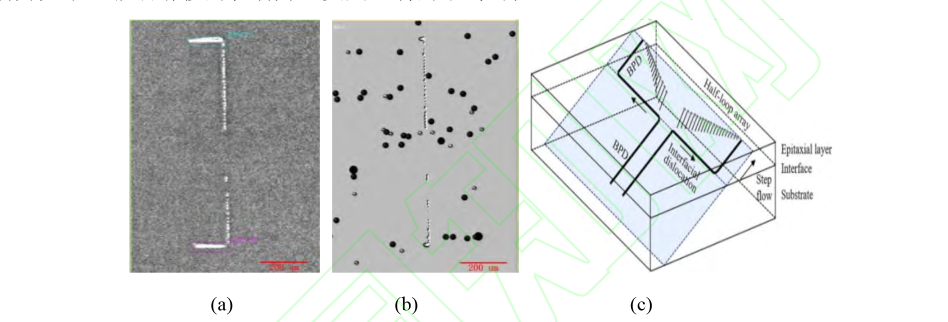

在生长过程中,在应力等条件作用下,BPD很容易在衬底和外延层界面上沿着台阶流法线方向发生滑移,形成界面位错(interfacial dislocations,滑移方向取决于BPD的伯氏矢量及应力方向。特定条件下,成对BPD同时发生滑移,会形成Σ-BPD。在研发过程中也观察到过该缺陷,其典型形貌如图2所示,Photoluminescence 检测BPD形貌如图3(a),对外延片进行KOH腐蚀后形貌如图3(b)所示,可以看到一个Σ-BPD包含两条界面位错,其长度可以达到毫米级,在其尾部存在两个BPD。Σ-BPD形成机理示意图如图3(c)所示,其起源于衬底的BPD对,其伯氏矢量方向刚好相反,滑移过程中形成两条界面位错和2个半环位错(half-loop arrays,HLAs)。半环位错的长度不一,决定于其驱动力大小,影响滑移的驱动力主要是温场的不均匀性。

图2 Σ-BPD 形貌图(a)、氢氧化钾腐蚀坑图(b)和形成机理示意图(c)

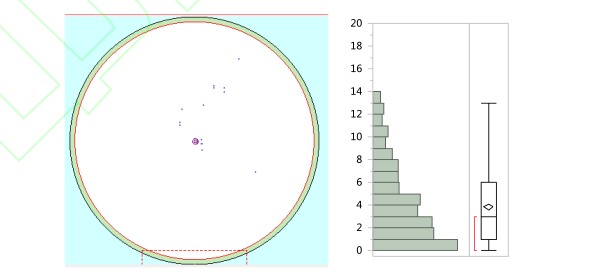

针对外延BPD,研究团队在快速外延生长的基础上优化外延层缓冲层工艺窗口,目前可以实现BPD 密度小于0.1 cm-3 的外延层批量制备,如图3所示。

图3 外延片的BPD分布及其控制

2.3 层错缺陷

SiC外延层中的层错包括两大类,一类来源于衬底的层错和位错缺陷,衬底的层错会导致外延层形成Bar-shaped SFs,衬底的部分TSD会形成Frank SFs;另一类层错为生长层错(in-grown SFs),是外延生长过程中产生的,与衬底质量没有关系。目前,大多数外延层错属于第二类,这些层错中绝大部分为Shockley SFs,是通过在基平面中的滑移产生的。

降低外延生长速率、原位氢气刻蚀优化、增加生长温度、改善衬底质量都可以有效降低层错数量,天科合达已经可以提供Shockley SFs 密度小于0.15 cm-2的6英寸SiC衬底。

2.4 表面缺陷

SiC外延层表面缺陷尺度比较大,一般通过光学显微镜可以直接观察到,包括掉落物、三角形缺陷、“胡萝卜”缺陷、彗星缺陷、硅滴和浅坑。

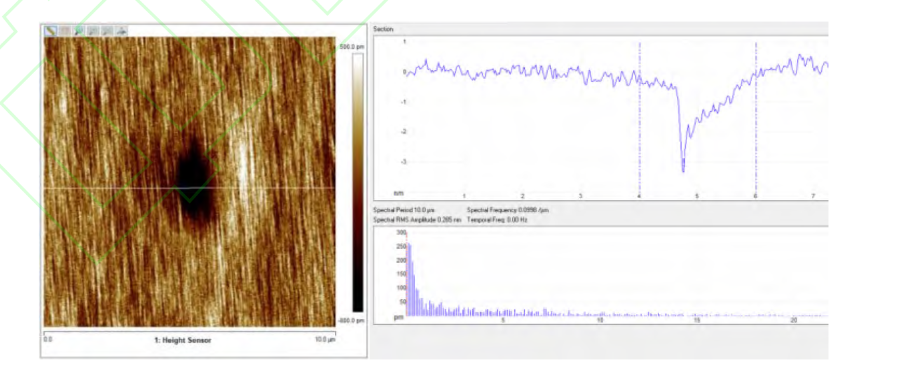

表面缺陷与器件性能的影响目前也已经有了较多的研究报道,除浅坑缺陷外,其他表面缺陷基本都会对器件的性能产生一定的不利影响,导致器件击穿电压降低或者反向漏流增加。浅坑(Pits)是4H-SiC外延层表面出现在TSD位错顶端的小凹陷或小坑状的形貌缺陷,其宽度尺度小于10 μm。TED在外延层表面引起的小坑尺寸远小于TSD诱发的小坑尺寸,很难被观察到。图4是典型的浅坑AFM 形貌。

图4 外延表面宽度和深度分别为2和4 nm的浅坑的AFM形貌

Ohtani、Noboru等则利用TUNA技术研究了Pits和Large Pits的产生机理,认为宽度在几微米、深度在14 nm左右的Large pits是由TSD产生,而宽度在1 μm、深度在3-4 nm的Pits由TED产生。

降低Pits的主要途径包括:优选TSD数量较少的优质衬底、降低碳硅比和降低外延生长速率。目前市场上主要的商业化衬底中TSD的密度为小于1000/cm-3。本研究团队已经可以提供TSD密度小于300/cm-3的6英寸SiC衬底。通过采用优质衬底,调整外延工艺,可以将Pits数量从103降低到50以内。

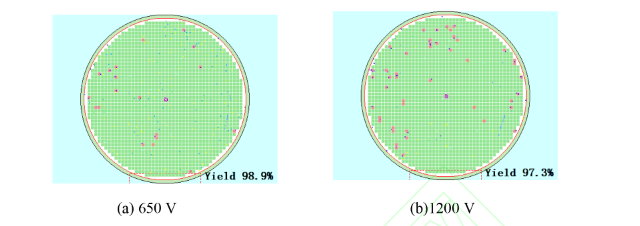

综合来看,SiC外延层缺陷一方面取决于衬底结晶质量以及表面加工质量,另一方面受制于外延生长工艺窗口的优化,需要综合考虑各种缺陷的调整方案。基于研究团队量产的高质量6英寸SiC衬底,通过大量的实验研究,可以有效控制住SiC外延的各种缺陷,完成650V和1200V外延片产品开发和产业化工作。图5是典型的650V和1200V外延片产品缺陷mapping图,3mm×3mm良品率分别为98.9%和97.3%。

图5 650 V和1200 V外延片,3 mm×3 mm良品率分别为98.9%和97.3%

展 望

SiC外延在产业链中起着承上启下的重要作用,一方面通过不断积累对SiC材料的性能认知和改良,一方面通过器件的不断迭代验证,最终提升外延品质,推动SiC器件的应用。本文采用天科合达自有的商业化6英寸衬底,在4H SiC同质外延过程中,研究了外延层中BPD、层错、硅滴和Pits缺陷的控制,并对Σ-BPD的产生机理和消除进行研究,最终获得厚度均匀性小于3%、浓度均匀性小于6%、表面粗糙度小于0.2m、良品率大于96%、BPD密度小于0.1cm的外延产品。目前从本团队的研发进度来看,通过对工艺温度、C/Si比和长速等参数优化使得浓厚度分别控制在3%和2%以内,BPD的密度可以控制在0.075cm以内,但仍需要大量的外延数据进行工艺稳定性验证。

-

SiC外延片的化学机械清洗方法2025-02-11 414

-

有效抑制SiC外延片掉落物缺陷生成的方法2025-02-10 401

-

提高SiC外延生长速率和品质的方法2025-02-06 1892

-

SiC外延生长技术的生产过程及注意事项2024-11-14 2798

-

4H-SiC缺陷概述2023-12-28 5545

-

SiC外延片测试需要哪些分析2023-08-05 4846

-

国产CVD设备在4H-SiC衬底上的同质外延实验2023-06-19 2744

-

SiC外延工艺基本介绍2023-05-31 8821

-

外延层的掺杂浓度对SiC功率器件的重要性2022-04-11 10598

-

SiC功率器件的封装技术研究2018-09-11 3004

-

钝化层刻蚀对厚铝铝须缺陷影响的研究2018-03-06 8298

-

改善4H-SiC晶圆表面缺陷的高压碳化硅解决方案2016-11-04 2526

-

Sic mesfet工艺技术研究与器件研究2009-10-06 6779

-

硅单晶外延层的质量检测与分析2009-03-09 4207

全部0条评论

快来发表一下你的评论吧 !