电源门控单元的实现原理

电子说

描述

标题为“电源门控”的文章演示了电源门控单元的实现以及它如何帮助最大限度地减少 SoC 的泄漏功耗。其基本原理是切断从电池(VDD)到接地(GND)的直接路径。虽然有效地节省泄漏功率,实施讨论遭受一个主要的缺点!它不挽留的状态!这意味着,一旦SoC的功率恢复,功率门控单元的输出将变为“X”。你不能确定它是逻辑1还是逻辑0。在乎吗是的!因为如果这个X传播到设计中,整个设备就可能进入亚稳态!为了防止这种灾难性的情况:系统软件可以简单地重置SoC。这将从头启动,并确保所有设备都已初始化。

这意味着,每次我决定给我的SoC的一部分供电时,一旦恢复电源,我就必须重新设置那个电源门控部分。这对上一篇文章中讨论的电源门的应用施加了严重的限制。设计一个保持状态的电源门怎么样?但要说服自己,为了做到这一点,你需要花费,虽然很小,一些泄漏功率。我们把这个结构称为:状态保持伪功率门。术语“伪”意味着它将消耗一点泄漏功率,而不是先前的结构。但与此同时,您不再需要重置SoC的电源门控部分,因为标准单元保留了它们以前的数据!!不说了!下面我们来讨论一下实现。

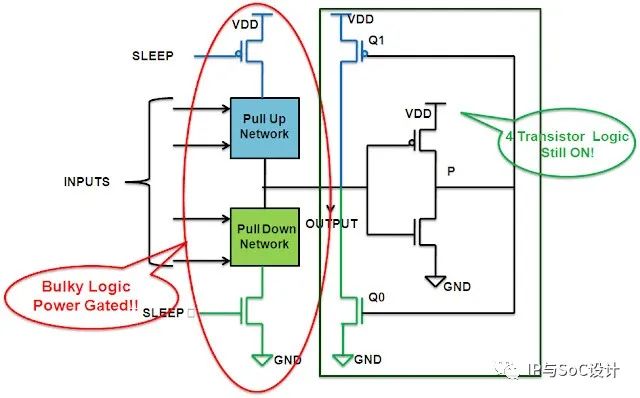

以上电路有两部分。

·红色椭圆形内部的结构与普通的功率门控结构相同。

·绿框内的一个(右边)是使该设备保持其状态所需的附加电路。

操作:在进入睡眠模式之前,设备的输出为逻辑1。进入睡眠模式(关闭电源)后,睡眠晶体管开始工作,并切断设备的电源和接地轨,从而节省泄漏功率。但是右边的逻辑(在绿色矩形中)仍然是ON!反相器的输出现在将变成OUTPUT’,即逻辑0。这将反过来使PMOS晶体管Q1和输出将恢复到逻辑1。

当输出在电源门控之前为逻辑0时,情况也是如此。在这种情况下,NMOS晶体管Q0将起作用,以帮助输出节点保留其数据。

请注意:在此期间,当设备处于睡眠模式时,输出节点将继续泄漏。通过添加额外的电路,如图所示,我们基本上是试图创建一个反馈回路,这再次有助于保持状态。命中,当然是4个晶体管的泄漏功率。然而,标准单元逻辑(红色椭圆形)通常是笨重的。即使是一个简单的双输入"与非"门本身也有4个晶体管。而更高阶的输入会有更多!同样的技术可以应用于任何顺序的设备,如触发器,锁存器,甚至时钟门控集成单元。

审核编辑:汤梓红

-

PyTorch教程10.2之门控循环单元(GRU)2023-06-05 915

-

什么是时钟门控?如何去实线时钟门控的设计呢2022-12-19 1793

-

门控时钟实现低功耗的原理2022-07-03 3372

-

电源门控可以降低泄漏功耗吗2022-02-11 1189

-

LPMM阅读笔记——第五章 电源门控设计part12022-01-11 639

-

如何去实现一种电源门控的设计呢2021-12-31 1033

-

什么是门控时钟 门控时钟降低功耗的原理2021-09-23 15908

-

电动后尾门控制单元主要功能2021-08-26 1802

-

通常有两种不同的时钟门控实现技术2021-06-13 3457

-

一种门控循环单元兴趣点推荐算法2021-05-13 935

-

模块化气动阀门控制单元的原理及设计2019-01-03 2560

-

低功耗时钟门控算术逻辑单元在不同FPGA中的时钟能量分析2015-11-19 679

-

基于门控时钟的低功耗电路设计方案2011-02-21 4129

全部0条评论

快来发表一下你的评论吧 !