Bandgap常用电路及误差分析

描述

A Single-Trim CMOS Bandgap Reference With a 3δ Inaccuracy of 0.15% From 40C to 125C

概述:

1、为了消掉process偏差导致的每片chip的偏差,需要使用trim技术对每片进行单独的校准

2、bandgap中process的偏差一般是线性的,可以通过单点校准来上下调节曲线的纵坐标进行校准

3、Bandgap中的运放offset偏差是非线性的,不能通过单点校准来消除

4、通常要降低运放的offset偏差可以使用bipolar充当输入对管,也可以使用大尺寸的MOS对管

前者的匹配性比较好但是需要bicmos工艺;后者在牺牲面积的情况下可以减小MOS对管的offset

5、运放的offset还可以通过添加调零电路和chopper电路来实现

前者会导致输出不连续同时增加运放的低频噪声;后者会使用时钟,增加动态功耗,同时带来高频下的ripple,需要大的滤波电容来减小ripple

6、VBE的温度特性是轻微非线性的(二阶非线性),需要使用曲率补偿减小该温度特性

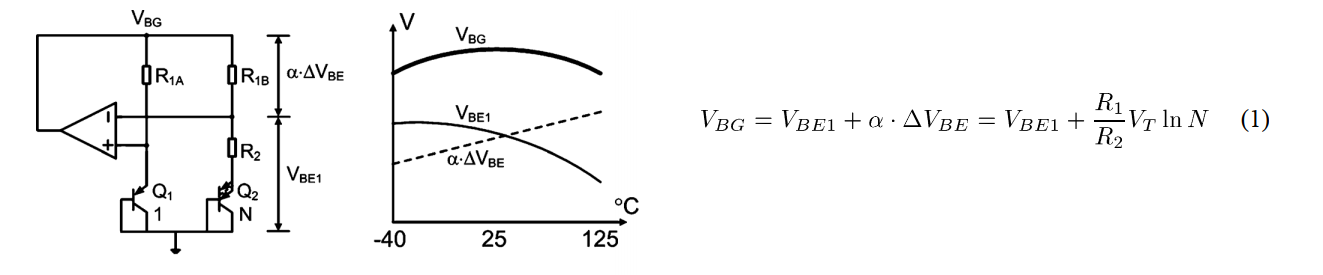

Bandgap原理:

通过运放将VBEQ1钳位到R2上端,使得R2上电压压降为ΔVBE=VBEQ1-VBEQ2=VT*lnN,流过R1/R2支路的电流相等(R1/R2两端电压差值相等),则VBG表达式如公式(1)所示

Bandgap常用电路及误差分析:

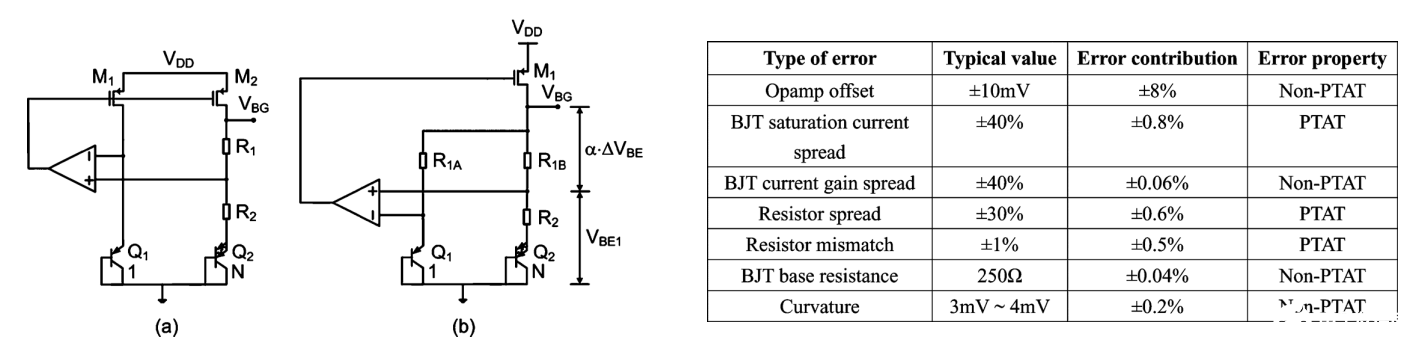

实际bandgap电路如(a)所示,该架构中M1/M2存在失配,为了减小失配的影响,一般采用(b)架构,主要是利用R1A/R1B(电阻大,数量多,匹配度高)之间的失配比M1/M2小得多这个原理

Bandgap中的误差:

线性误差: a、三极管饱和漏电流IS的偏差 b、电阻的偏差 c、电阻mismatch

以上的线性误差可以通过trimming进行单点消除

非线性误差:

a、运放的失调电压offset -- 使用chopper电路

b、三极管的VBE电压 -- 使用曲率补偿电路

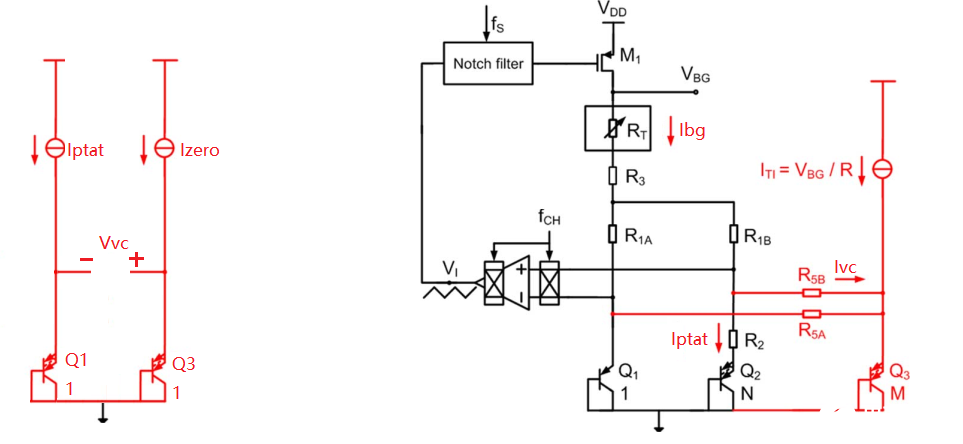

Trimming原理:

VBG = VBEQ1 + IPTAT*R1A + 2*IPTAT*(R3+RT),其中IPATA=VT*ln8/R2

调节RT的阻值,就能使得VBG的电压上升或者下降,此时VBG温度曲率不发生改变(IPTAT未被处理)

此处修改:RT的阻值改变不仅会影响BG的温度特性(RT直接影响IPTAT的系数)还会影响BG的DC电平,此处涉及到两种校准目标:

1、不关心VBG曲线的上下移动,当不同PV下,温度曲线会呈现不同的正温、负温特性(PVT仿真仿一仿就知道了)

此时需要两点校准:在0℃和80℃下(此处取值为假设)分别测量到VBG输出电压1.12V和1.18V,得到正温斜率,则按照编程code位控制减小RT值,可以调节温度特性变为水平

2、不关心调节RT对温度特性的影响,只需要单点校准,在室温27℃下,测量得到两片die,一片1.12v,一片1.25v,则前一片RT增大,后一片RT减小,使得VBG调整到1.2V

假设27℃下VBG随PV会发生40mV的上下总偏差,电阻RT变化范围设计20kohm,要想得到至少0.5mV的调节精度,则至少需要7BIT编程调节,得到40mV/(2^7)=0.3125mV的调节精度

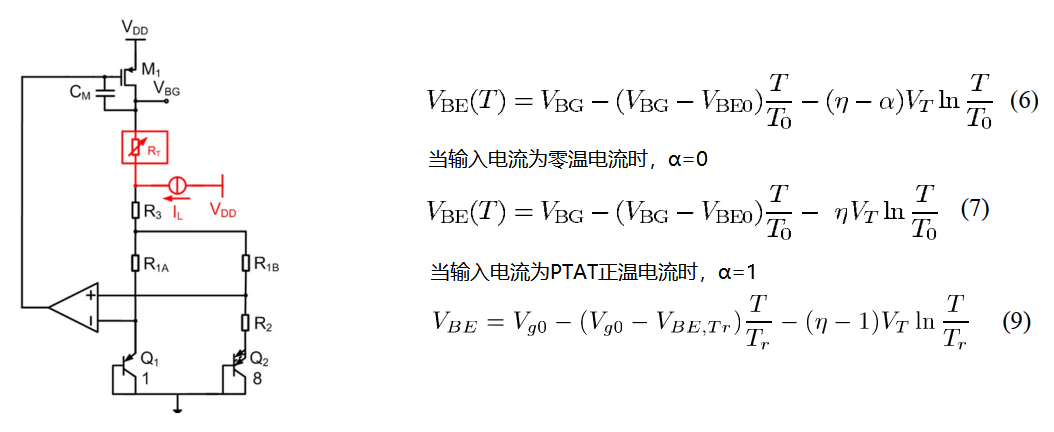

VBE曲率补偿原理:

VBE非线性表达式如(6)所示,当三极管输入零温漂电流时,α=0;当输入为PTAT电流时,α=1

如上图左所示,Q1路流入PTAT正温电流,Q3路流入ZERO零温漂电流,则根据等式(7)(9)有:

Vvc = VBEQ3 - VBEQ1 = VT*ln(T/T0)

则上图右所示的实际电路中有:

Ibg/2 = Ipata+Ivc = VT*lnN/R2 - (-Vvc/R5)=VT*lnN/R2+VT*ln(T/T0)/R5

VBG = VBEQ1+R1*(Ibg/2)+(R3+RT)*Ibg = VBEQ1+(R1+2R3+2RT)/R2*VT*lnN+(R1+2R3+2RT)/R5*VT*ln(T/T0)

其中两个绿色部分VBEQ1中存在的-(η-1)*VT*ln(T/T0)非线性项和(R1+2R3+2RT)/R5*VT*ln(T/T0)项,可以通过电阻比例的合适取值抵消掉 → (R1+2R2+2RT)/R5=(η-1) η通常取4

最终的VBG=VBEQ0*(T/T0)+(R1+2R3+2RT)/R2*VT*lnN,无二阶非线性项存在

审核编辑:黄飞

-

常用电路模块分析2012-08-12 8396

-

200常用电路2013-07-17 3869

-

常用电路2014-03-13 2560

-

常用电路精选2014-08-03 7093

-

常用电路的分析方法与技巧2017-07-12 4082

-

常用电路知识分享2019-05-15 3851

-

实验常用电路元器件2010-07-17 597

-

常用电话拨号集成电路2006-06-30 2857

-

[常用电路的分析方法与技巧].王俊峰.李素敏.扫描版2012-11-23 1458

-

555常用电路2017-09-18 1075

-

几个常用电路2018-03-04 17113

-

常用电路的分析方法与技巧pdf2021-10-08 1706

-

348常用实用电路图大全2021-11-10 10682

-

负反馈放大电路误差分析2023-12-01 8057

-

多款常用电子电路分享2025-02-08 527

全部0条评论

快来发表一下你的评论吧 !