浅谈三维单片异构集成的发展历程

描述

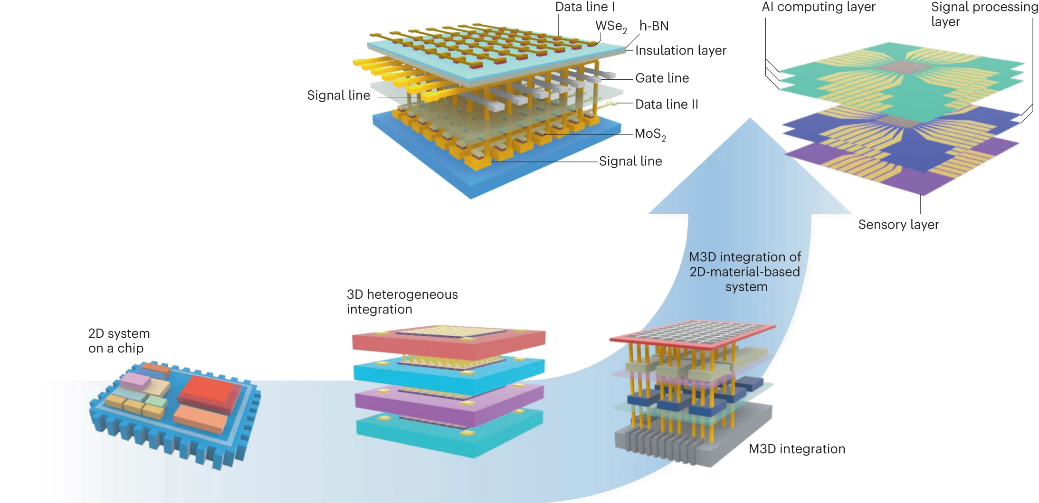

近年来,三维异质集成技术正在崭露头角,通过协同设计和微纳制造工艺,将不同材料和功能的电子器件堆叠在一起。其独特之处在于,不同类型的器件垂直组合,形成了更小巧且高效的器件单元。然而,器件层与层之间的连接一直是该技术的巨大挑战,将器件从衬底剥离极容易发生机械故障。此时,基于二维材料的电子器件展现出巨大潜力,这些材料具有极低的刚度和几乎为零的内应力,或许能够完全摆脱传统刚性三维材料在三维异质集成技术中的物理限制。

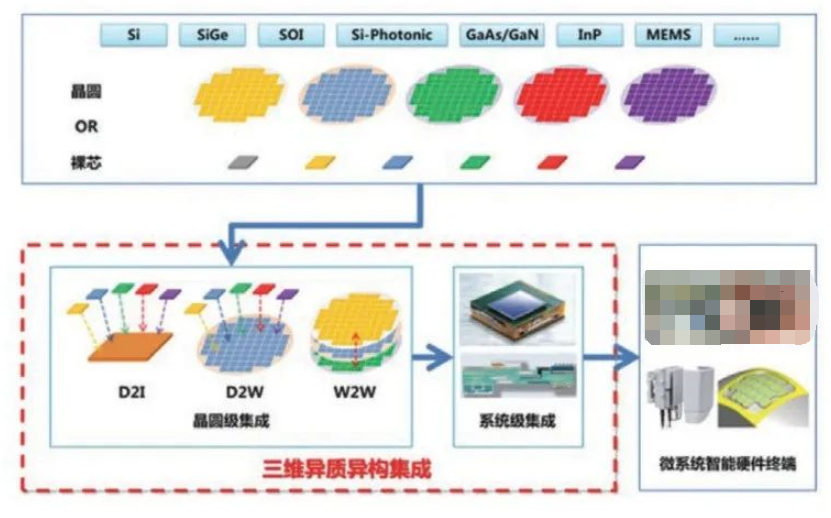

三维异质集成示意图

近日,圣路易斯华盛顿大学Sang-Hoon Bae、麻省理工学院Jeehwan Kim、韩国延世大学Jong-Hyun Ahn等研究者合作在Nature Materials 杂志上发表论文,展示了基于二维材料的晶体管和忆阻器的三维单片异构集成,可作为高效率人工智能(AI)处理器执行AI任务。

三维单片异构集成的发展历程示意图 总共六层器件垂直堆叠,整体厚度不到2微米,为了验证3D异质集成的器件性能,研究者利用AI处理器进行了DNA测序计算,忆阻器显示数值与软件模拟结果相匹配,显示出良好的并行计算能力。此外,随着3D集成层数量的增加,每层阵列的电压降减小,减少了冗余数据传输,可以降低器件功耗,缩短预测的处理时间和延迟。

基于2D材料的3D单片异质集成策略为下一代芯片制备铺平了道路。中国科学院大学胡伟达研究员在同期Nature Materials 杂志上评论道,“非冯•诺依曼体系结构与3D单片异质集成的融合,极大地降低了处理时间延迟和功耗……AI处理器具有处理更快速、电压降更低、单元面积更小等优势,这得益于垂直集成技术”。Sang-Hoon Bae教授也表示,“你可以把芯片集成想象成建造一座房子,3D单片异质集成有利于开发出更紧凑、更强大和更节能的设备,重塑整个微电子和计算行业,从自动驾驶汽车到医疗诊断和数据中心,该技术的应用可能性是无限的”。

审核编辑:黄飞

-

世界级专家为你解读:晶圆级三维系统集成技术2011-12-02 10386

-

单片机三维控制平台2013-03-04 5467

-

三维曲线加速度2013-10-23 3511

-

三维逆向工程的成果及应用案例2016-03-02 3691

-

三维快速建模技术与三维扫描建模的应用2018-08-07 3977

-

广西扫描服务三维检测三维扫描仪2018-08-29 6057

-

三维设计应用案例2019-07-03 2557

-

晶圆级三维封装技术发展2020-12-28 4450

-

基于LTCC技术的三维集成微波组件2011-06-20 1054

-

三维数字化集成检测系统实现关键技术分析2018-11-30 1720

-

惯性微系统正在朝着三维封装集成架构发展2019-11-30 8030

-

蔡坚:封装技术正在经历系统级封装与三维集成的发展阶段2021-01-10 3255

-

基于三维集成技术的红外探测器2022-04-25 3491

-

智慧城市_实景三维|物业楼三维扫描案例分享_泰来三维2023-05-16 2141

-

泰来三维|文物三维扫描,文物三维模型怎样制作2024-03-12 1802

全部0条评论

快来发表一下你的评论吧 !